第三章 作业(7BF)【计算机系统结构】

第三章 作业(7BF)【计算机系统结构】

- 前言

- 推荐

- 第三章 作业(7BF)

-

- 7

- 11

- 15

- 鲲鹏流水线调研

-

- 华为鲲鹏处理器

- ARM体系的总体思想

- ARM的流水线结构

- 最后

前言

2023-4-10 18:49:41

以下内容源自《【计算机系统结构】》

仅供学习交流使用

推荐

第一章 作业【计算机系统结构】

第三章 作业(7BF)

第一章 作业【计算机系统结构】

7

3.7简述3种向量处理方式,它们对向量处理机的结构要求有何不同?

横向处理方式 按行的方式从左到右横向地进行

纵向处理方式 按列的方式从上到下横向地进行

纵横处理方式 把向量分为若干组,组内按纵向处理方式,再依次处理各组

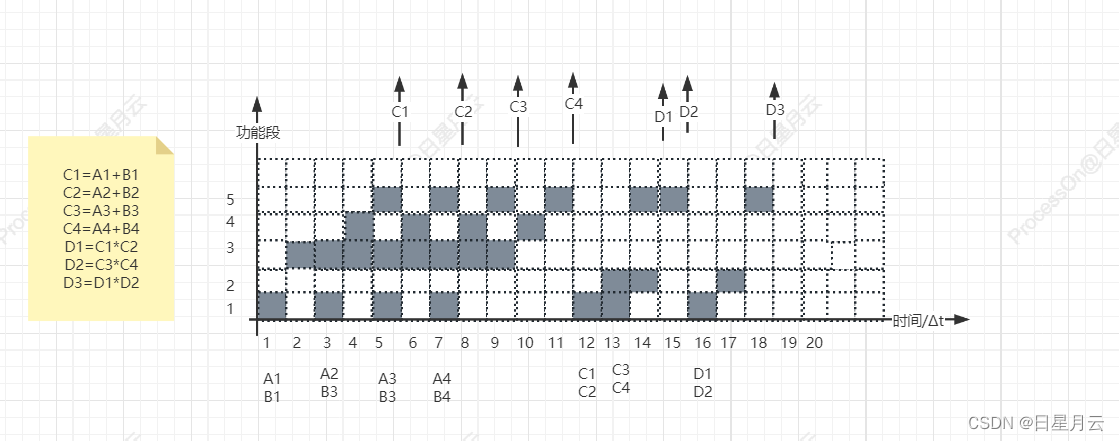

11

3.11有一条静态多功能流水线出5段组成(如图3.45所示加法用1、3、4、5段,乘法用1、2、5段,第3段的时间为2△t ,其余各段的时间均△t, 而且流水线的输出端或暂存于相应的流水寄存器中。现要在该流水线上计算Πi=1-4(Ai+Bi),画出其时空图,并计算其吞吐率、加速比和效率。

相关例题:3.1

吞吐量:TP=7/18

加速比:S=(5*4+3*3)/18=29/18

效率:E=29/(5×18)=29/90

15

3.15在CRAY-1计算机上按照链接方式执行下述4条间量指令(括号中给出了相应功能部件的执行时间),如果向量寄存器和功能部件之间的数据传送需要1拍,试水此链接流水线的通过时间是多少拍?如果向量长度为64,则需多少拍才能得到全部结果?

V0<一存储器 (从存储器中取数:7拍)

V2<-V0+V1(向量加:3拍)

V3<-V2<A3(按(A3)左移:4拍)

V5-V3 ∧V4(向量逻辑乘:2拍)

相关例题:3.3

链接流水线的通过时间:(7+1)+(1+3+1)+(1+4+1)+(1+2+1)=23

如果向量长度是64需要23+(64-1)=86拍得到全部结果

鲲鹏流水线调研

了解

鲲鹏920

世界第一ARM CPU?鲲鹏920规格

Kunpeng处理器组织和芯片架构详解

参考

鲲鹏920流水线

华为鲲鹏处理器

- 华为鲲鹏处理器基于Arm架构。Arm是一种CPU架构,有别于Intel、AMD CPU采用的CISC复杂指令集,Arm CPU采用RISC精简指令集(reduced instruction set computer,精简指令集计算机)。

- 传统的CISC体系由于指令集庞大,指令长度不固定,指令执行周期有长有短,使指令译码和流水线的实现在硬件上非常复杂,给芯片的设计开发和成本的降低带来了极大困难。

- 随着计算机技术的发展需要不断引入新的复杂的指令集,为支持这些新增的指令,计算机的体系结构会越来越复杂。然而,在CISC指令集的各种指令中,其使用频率却相差悬殊,大约有20%的指令会被反复使用,占整个程序代码的80%。而余下的80%的指令却不经常使用,在程序设计中只占20%,显然,这种结构是不太合理的。

- RISC结构优先选取使用频率最高的简单指令,避免复杂指令。将指令长度固定,指令格式和寻址方式种类减少。以控制逻辑为主,不用或少用微码控制等措施来达到上述目的。

- Arm架构具有更好的并发性能,匹配业务特征能耗比更佳,更加灵活丰富的选择,业界热点快速发展。

ARM体系的总体思想

- 在不牺牲性能的同时,尽量简化处理器。同时从体系结构上灵活支持处理器扩展。采用RISC结构,RISC处理器简化了处理器结构,减少复杂功能指令的同时,提高了处理器速度。ARM及MIPS都是典型的RISC处理器。

ARM的流水线结构

-

ARM处理器使用流水线来增加处理器指令流的速度,这样可以使几个操作同时进行。并使处理和存储器系统连续操作。

ARM处理器分为三级

取指:指令从存储器中取出;

译码:对指令使用的寄存器进行译码;

执行:从寄存器组中读取寄存器,执行移位和ALU操作,寄存器被写回到寄存器组中。 -

流水线对PC值的影响

SPSR保存的程序状态寄存器,结构与CPSR完全一样,用来保存CPSR的值。以便出现异常时恢复CPSR的值。CPU内部的组成分为:指令寄存器,指令译码器,指令执行单元(包括ALU和通用寄存器组)CPU执行指令的步骤:取指->译码->执行

取指:将指令从内存或指令cache中取入指令寄存器

译码: 指令译码器对指令寄存器中的指令进行译码操作,辨识add,或是sub等操作

执行:指令执行单元根据译码的结果进行运算并保存结果

流水线操作:并发多条流水线(以3条为例)

1-取指 译码 执行

2-取指 译码 执行

3-取指 译码 执行

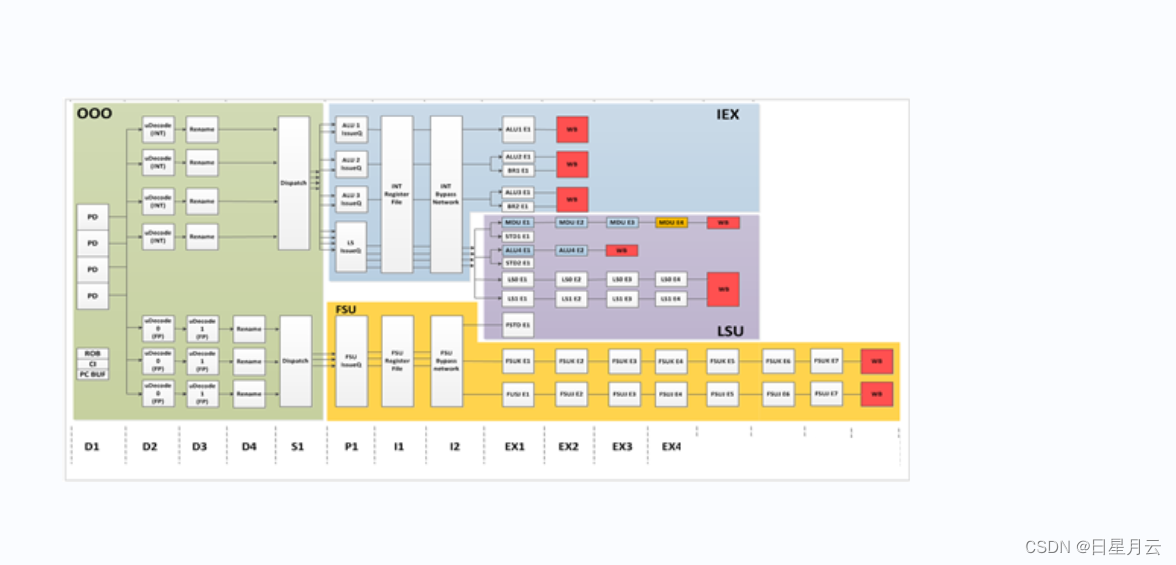

鲲鹏920处理器的流水线支持2个访存指令的发射队列,如下图中的红色框内所示,其访存单元WB支持每拍2条读或写访存指令。

最后

2023-4-19 20:49:32

祝大家逢考必过

点赞收藏关注哦