E4--光纤接口通信测试应用2023-04-17

1.场景

使用两块开发板A和B,通过光纤接口将在A板上ROM中存储的图片数据转发到B板并显示在B板连接的显示屏上,实现光纤接口通信。 具体场景是,由于A735T片上资源有限,因此ROM IP存储了一张1024*600(LVDS屏幕)分辨率图像的1/16,在发送端添加按键,第一次按键按下,将发送这1/16的数据到接收端,第二次按下,发送的则是每个像素取反后的数据。接收端使用RAM IP作为数据缓存实时更新来自光口的数据,读出端则是根据LVDS驱动模块产生的数据请求信号读出,最后达到的效果是发送端按一次按键,接收端切换一张图片。以此例程学习GT收发器、aurora协议,验证光纤接口通信。下面介绍开发与调试步骤。下图为板卡连接图。

2.基本概念

涉及该场景的术语有,serdes接口、GT、Aurora协议,光模块,光纤收发器等。通常SerDes(Serializer-Deserializer)是串行器和解串器的简称,Xilinx公司的许多FPGA已经内置了一个或多个GT收发器,通常二者是等价的,都指的是使用xilinx器件的内部收发器实现通信。需要说明,不同xilinx器件上的GT收发器不同,所支持的最大最小速率也不同,例如7系列的芯片有GTP、GTX、GTZ。serdes接口显著特点有三个,一是较之传统的源同步接口,serdes属于自同步接口,不需要发送时钟;二是使用了较少的引脚,实现了更大速率的传输,很多高速通信协议都是基于此串行协议,是目前高速通信的主流方案;三是通过加重和均衡技术实现了远距离传输,如背板。Aurora 是xilinx提出的一个用于在点对点串行链路间移动数据的可扩展轻量级链路层协议,因此在本文的场景中,物理层使用serdes,链路层使用aurora协议实现两个板卡点对点的通信。光纤是光通信的传输介质,通常板卡要与外部设备通信,需要使用光纤收发器进行光电转换,所谓SFP、QSFP等就是光纤收发器的一种。光模块是插接到光纤收发器上的,用于连接光纤和光纤收发器,也有很多封装类型。上述每一个概念都涉及很多东西,后续会继续分享,现在只需将每一个概念和实际的器件对应,知道正在做的事情处于通信架构中什么位置即可。

3.确认硬件环境

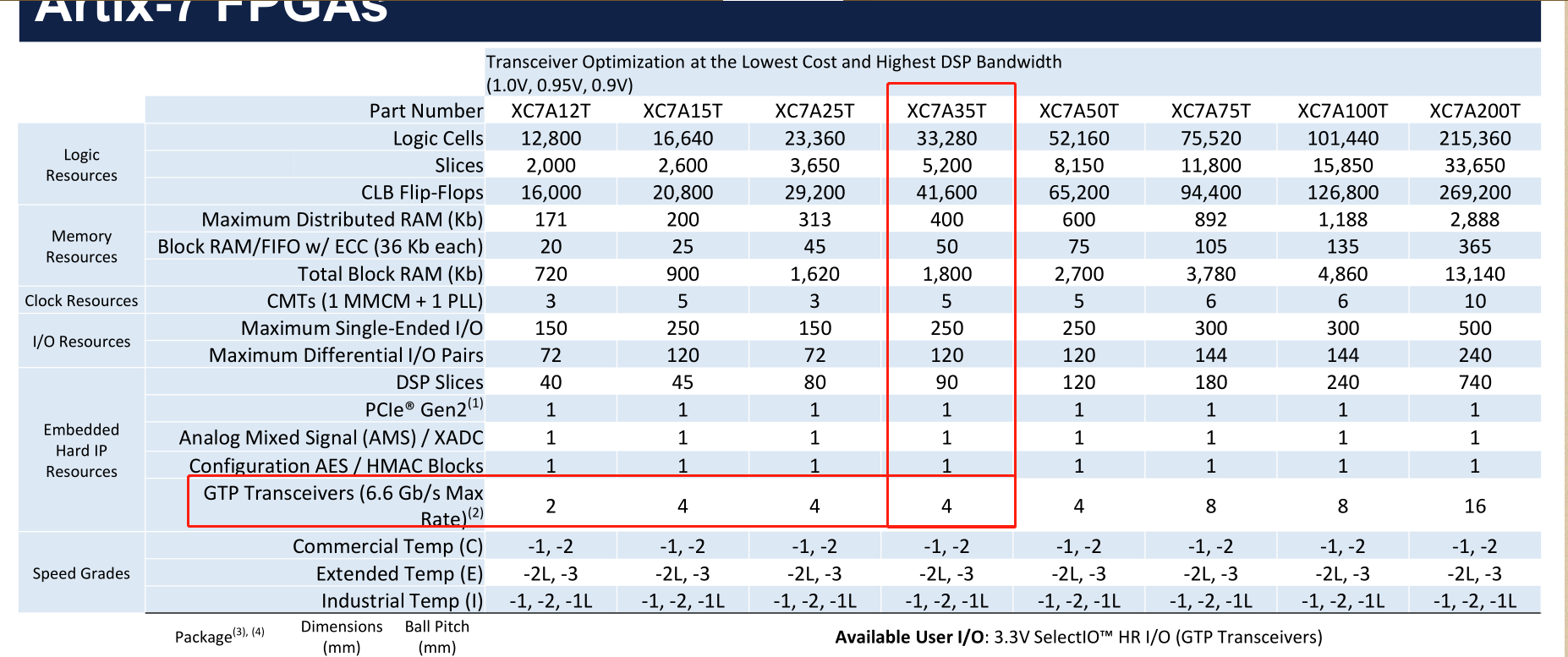

①使用两块米联客MA703FA开发板,FPGA芯片是xc7a35tffg484-2。

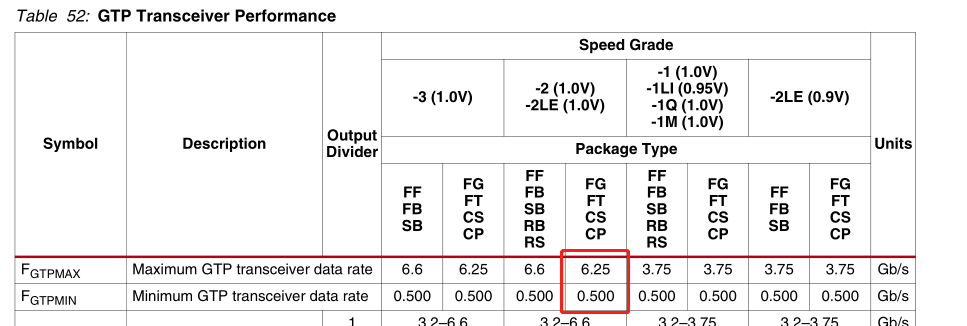

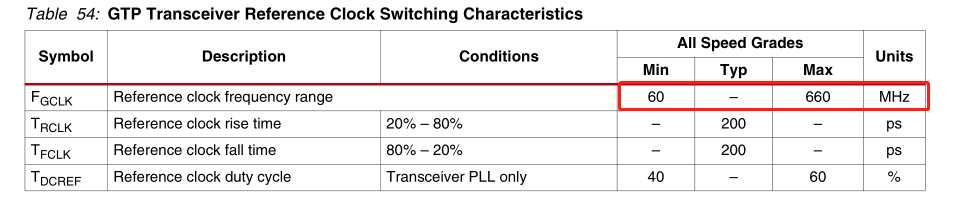

②确认GTP收发器速度

截图出自《Artix‐7 FPGAs Data Sheet: DC and AC Switching Characteristics》

参考时钟范围

③确认FPGA芯片GTP资源

③确认FPGA芯片GTP资源

截图出自《7 Series Product Selection Guide》

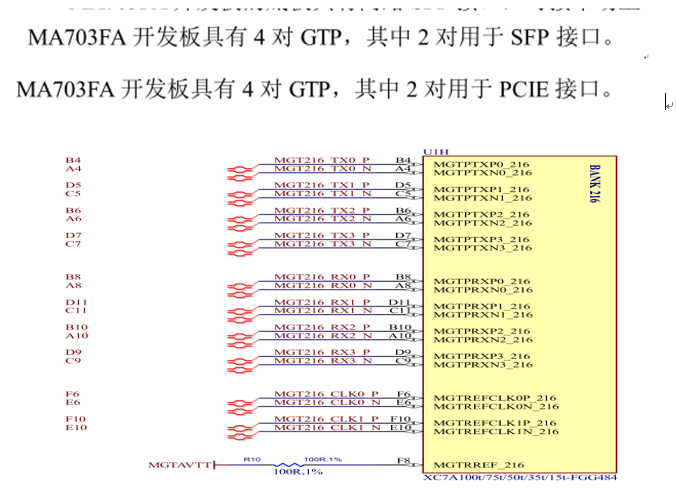

④确认开发板GT连接情况

截图出自《米联客硬件手册说明、原理图》

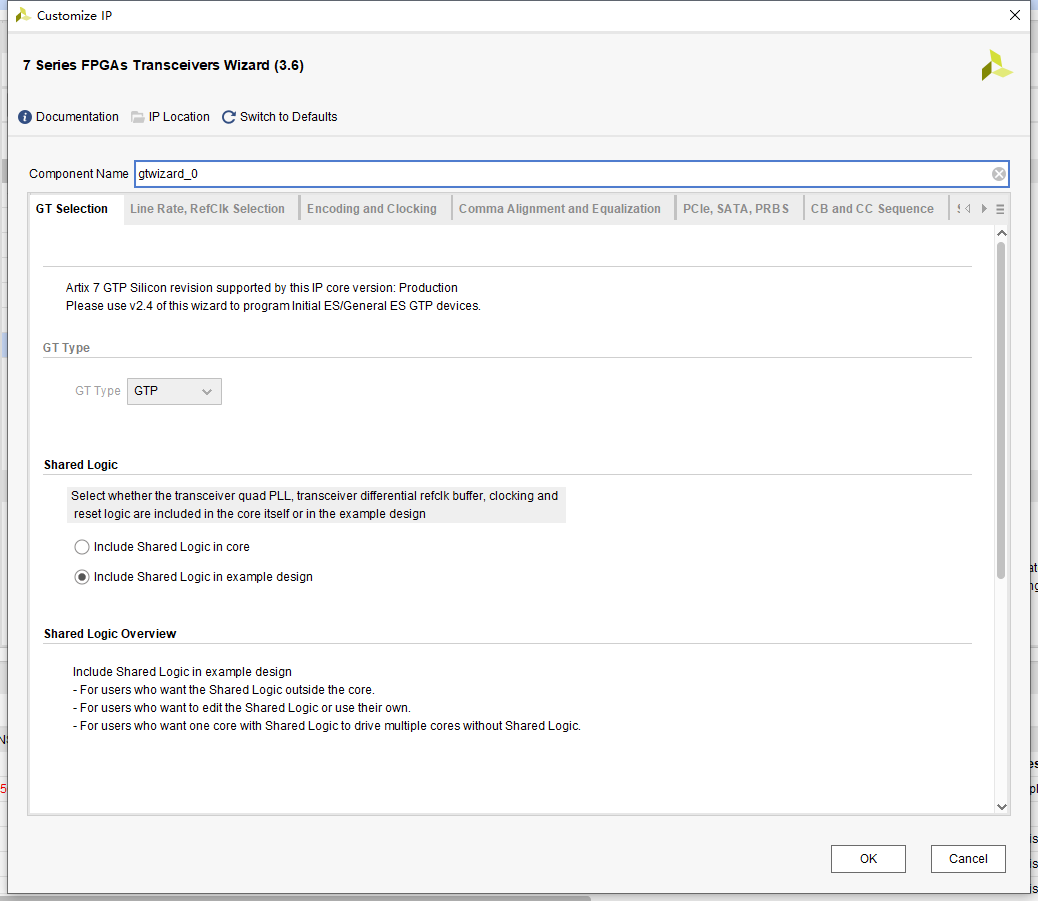

4.GT IP核配置

①图中share logic指共享逻辑是包含在内核本身还是示例设计( example design)中,把共享逻辑包含在内核本身的 IP 称为主核,内核中不包含共享逻辑的 IP 称为从核。从核与主核的区别是:我们可以在 Example Design 中修改共享逻辑。这里选择的是主核。此处共享逻辑指的是,IP涉及的多个时钟的来源都可以有几个地方,通过多路选择器选择,共享逻辑就包含了这些多路器的配置。

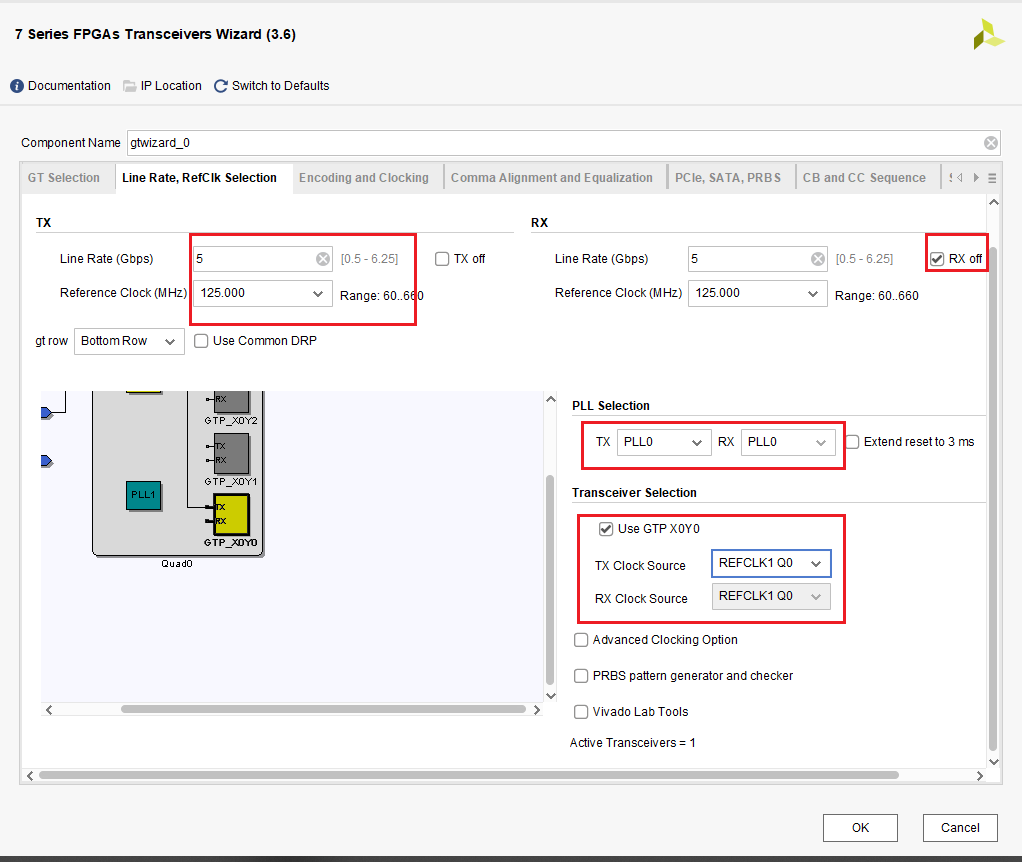

②线速率选择在芯片支持范围内结合自身应用场景,此处选择5G;参考时钟的选择看具体的硬件设计,这里选择125;发送端设计将Rx OFF打勾,接收端设计将Tx OFF打勾;PLL可选PLL0和PLL1,均可;X0Y0代表收发器的位置,与原理图中的设计应该是一致的;Clock Source选择REFCLK1,这是由硬件设计决定的。关于参考时钟GT内部的原理参看第六节。

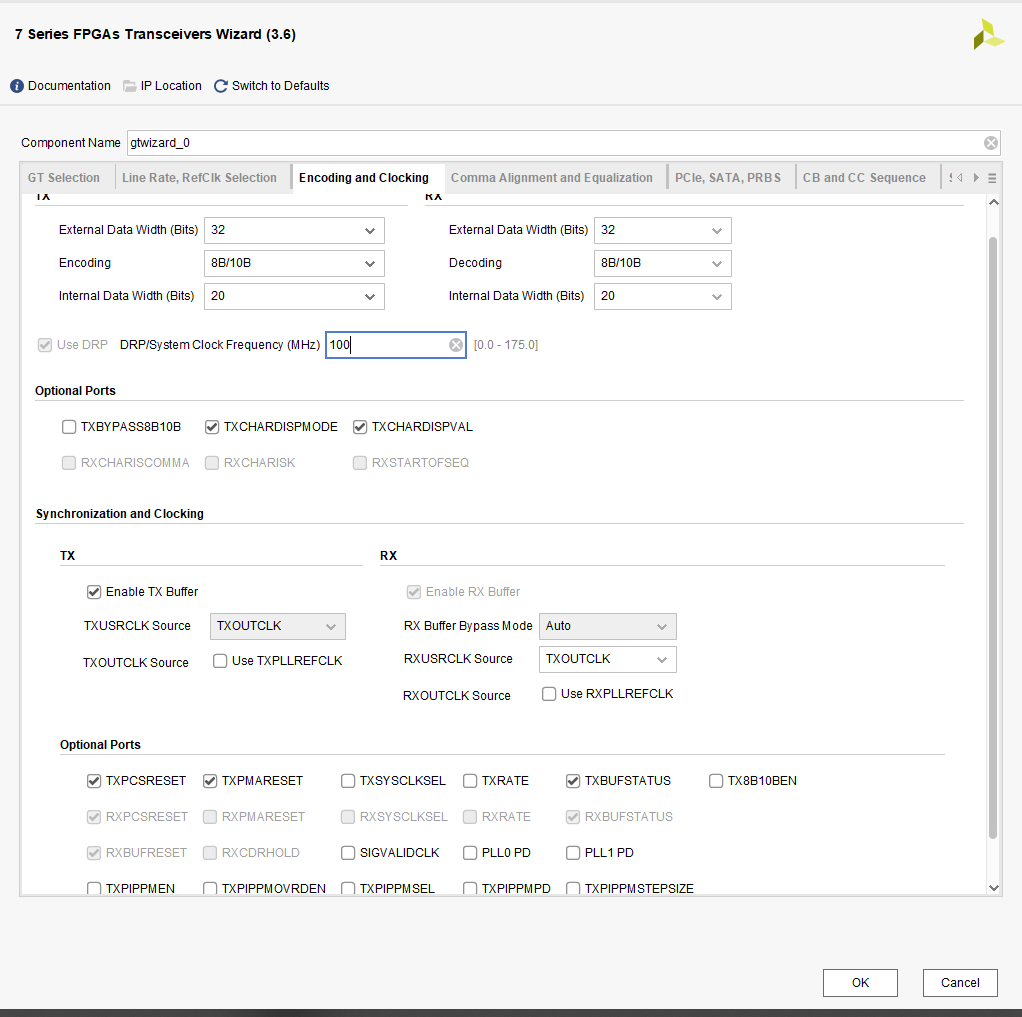

③该页中数据位宽设计如下图所示,DPR设置为50MHz(与图不对应)。勾选Enable Tx Buffer。

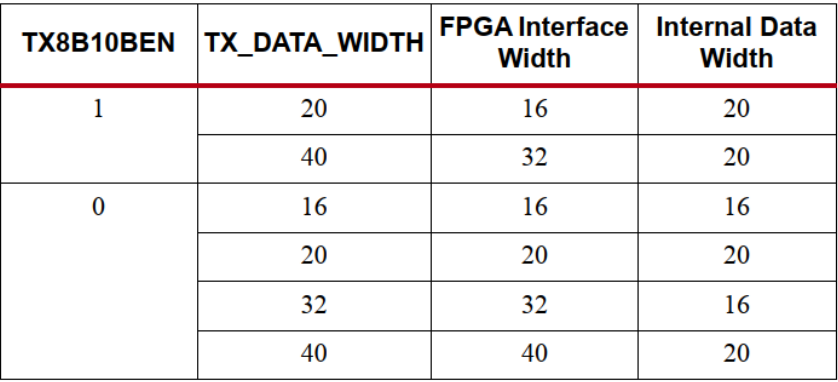

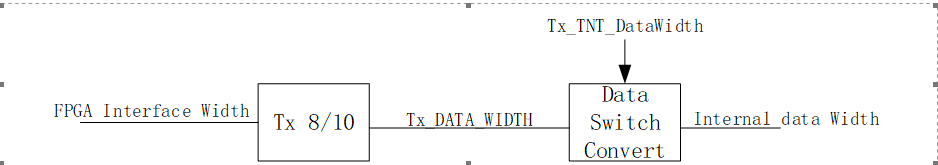

TXDATA 的位宽可以配置成 16/20/32/40 位宽,通过 TX_DATA_WIDTH 、FPGA Interface Width、TX8B10BEN 三个属性设置可以配置成不同的位宽,具体属性如下图所示.

几个位宽之间的关系,总之Aurora 8b10b single lane 4byte选择这个协议并且,External Data width选择为32bit即为IP核的输出位宽。

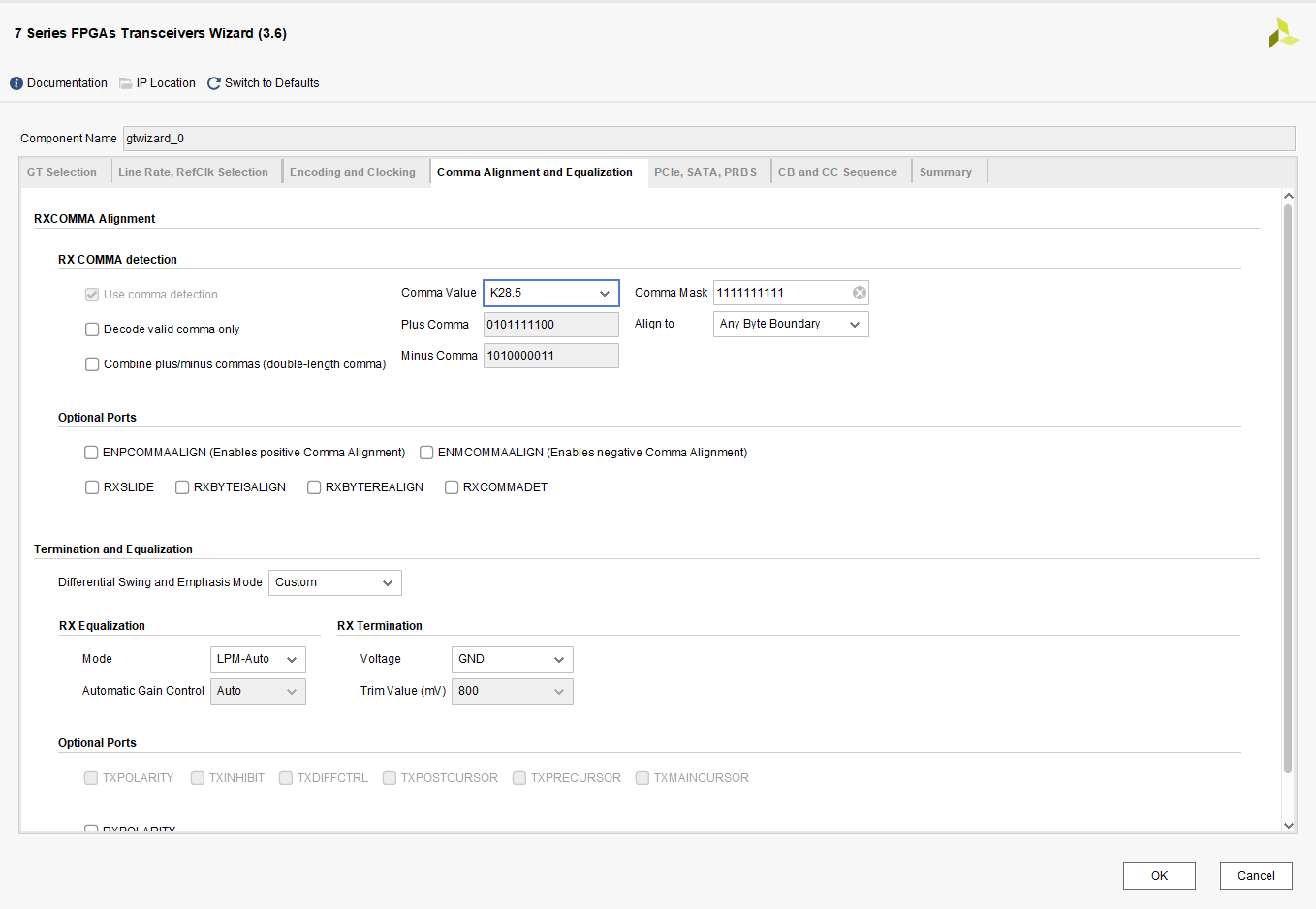

④本页设置K28.5即可,其余及后面页按照默认配置即可。

5.修改源代码

生成ip核之后,右键选择open in example design,会打开一个新的工程,这是xilinx写好的代码用于光口回环测试与验证。基本的架构是support模块输入参考时钟,生成各个所需时钟,并完成GT ip核、COMMON等模块的例化,数据收发接口也在该模块。Frame_gen模块根据生成的发送端用户时钟和复位产生IP核接收的数据信号和gt0_txcharisk_i信号,用户发送可修改这几个信号即可完成用户数据的发送。本例工程源码

发送端光接口源代码修改,①在topdesign中要改的主要是,IP核生成的复位和时钟信号要供外部使用。②开发板SFP 屏蔽笼的 tx_disable 引脚都默认接了上拉电阻,当为低时代表光接口使能,要使能该信号,否则无法工作;③发送的数据以及k码有效指示,要从外部模块给过来,因此屏蔽掉自产生模块;④添加顶层模块,自己编码并将数据源打造成从rom中来;⑤还有一个时钟要从板卡的晶振上提供或者从时钟IP核提供,注意板卡晶振的信号是单端信号,修改为IBUF,DRPCLK_IN;⑥依据板卡原理图添加约束。

发送端其他代码,主要包含了添加按键检测,添加了ROM IP存储图片数据,可参考Qt生成COE文件,ROM IP的配置。添加了数据生成的逻辑,添加了LED灯用于指示用户时钟的周期以此判断ip核是否正确生成。

接收端光接口源代码修改,①修改drp时钟来源为ip生成的50MHz或者来自晶振的时钟,修改为IBUF的相关硬件描述;②添加关于tx_disable的描述,并使能该信号;③IP核生成的复位和时钟信号要供外部使用,留下接口;④接收的数据以及k码有效指示,也要给到外部模块;④修改check模块生成的几个信号 supprot调用ip核那一段,如下所示;

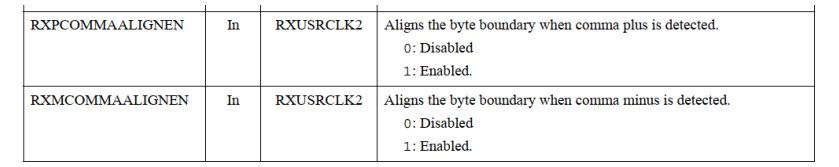

// .gt0_rxmcommaalignen_in (gt0_rxmcommaalignen_i),

// .gt0_rxpcommaalignen_in (gt0_rxpcommaalignen_i),.gt0_rxmcommaalignen_in (1'b1),.gt0_rxpcommaalignen_in (1'b1),

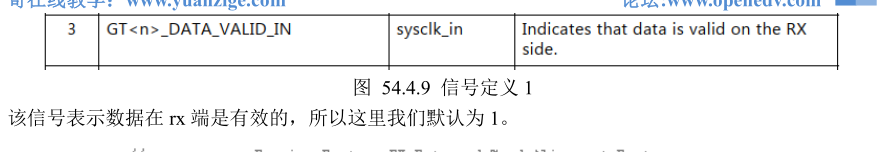

// .gt0_data_valid_in (gt0_track_data_i),.gt0_data_valid_in (1'b1),

接收端其他模块简介,u1_clk_ip模块产生lvds接口需要的时钟,以及DRP动态重配置时钟;u2_gt模块输入参考时钟接收数据通道以及光收发使能信号完成GT收发器数据及其指示信号的接收;u3_sfp_decode模块完成数据的对齐以及数据解码生成有效数据及其同步信号;u4_ram_ip模块作为数据缓存模块,接收来自光口的信号,并根据lvds屏幕的数据请求读出数据;u5_lvds模块是写好的屏幕驱动模块,可参考LVDS接口LCD驱动测试,将lcd_de信号发送到lvds线上的时间打一拍,保证RGB数据与lcd_de信号是同步的。这是因为等待ram数据两个周期的延迟。

其他重要信号说明,TXCHARISK用于指示TXDATA上的数据是K字符还是常规数据,看到很多资料上都说要发送comma,但是目前没看到应该至少t时间发送以此comma。RXCHARISK信号用于数据对齐,实现并不复杂可参考sfp_decode模块。Txuseclk Rate=line Rate/Internal Data Width,本例中Txuseclk Rate = 5G/20=250M.

6.GT原理简介

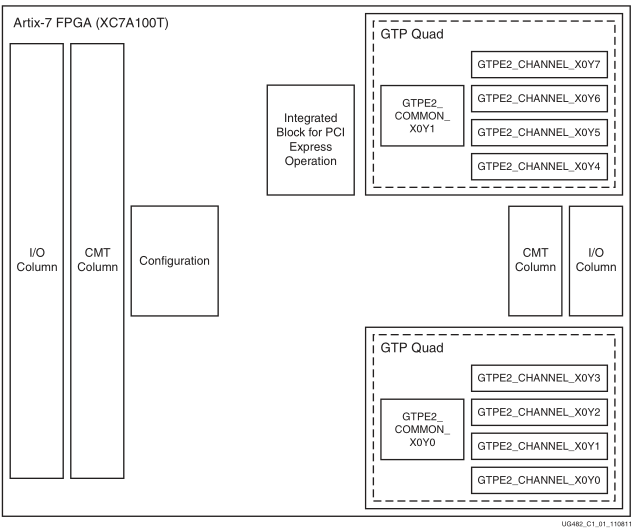

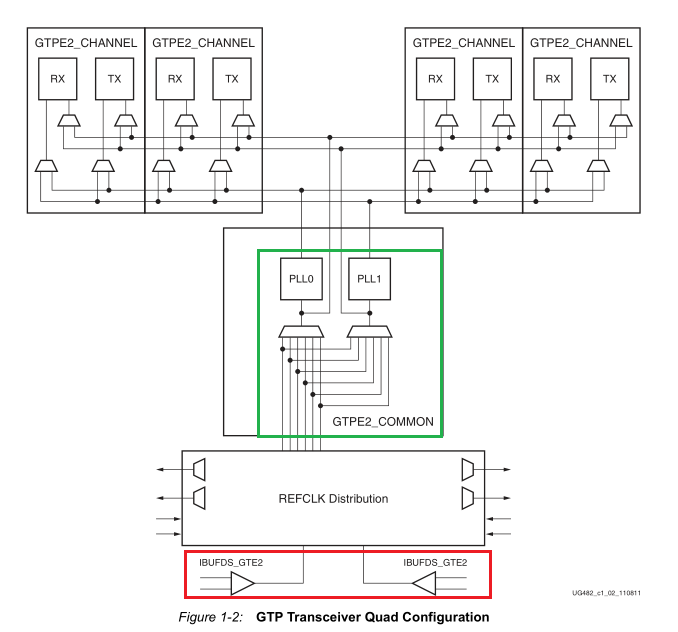

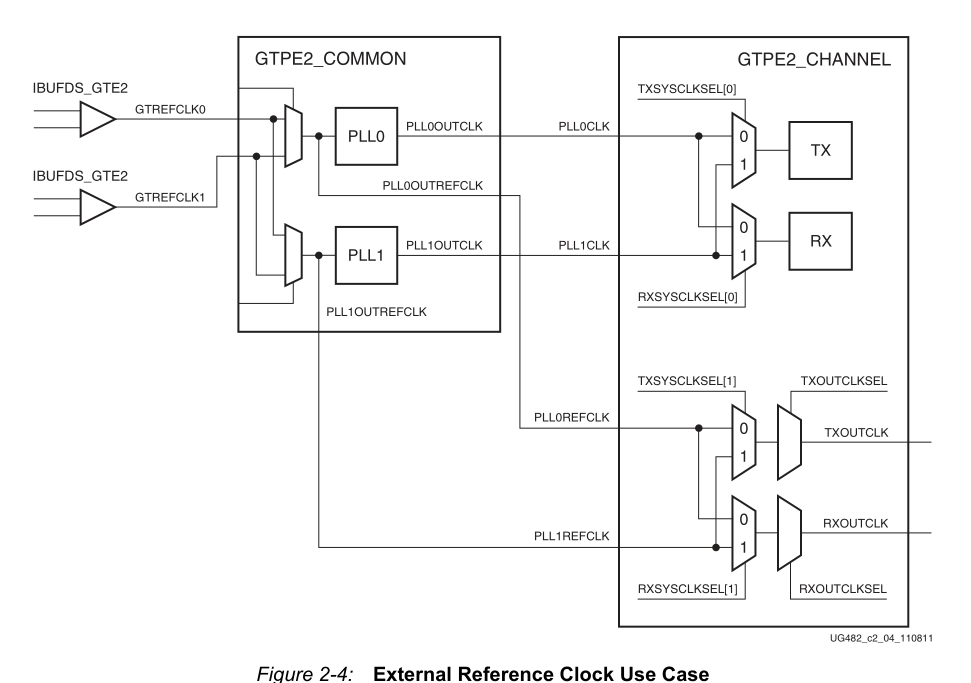

目的是为了对GT收发器有一个宏观的认识,清楚代码中的动作是在做哪里的配置,也清楚数据的流向。主要介绍内部结构下图所示为GTP内部的逻辑示意,由四个收发器通道GTPE2_CHANNEL和一个GTPE2_COMMON组成。每路 GTPE2_CHANNEL 有两个子层:PCS(物理编码子层)和 PMA(物理媒体连接子层)。PCS 子层包含 8B/10B 编解码、缓冲区、通道绑定和时钟修正等电路;PMA 层主要进行串并、并串转换、预加重、去加重、串行数据的发送和数据时钟的提取。

上图所示,红色框显示了GT参考时钟可以的来源由两个(实际参考时钟还可以来自相邻的GT,这在UG482都有详细),这也是IP和配置中选择REFCLK0还是REFCLK1的原因,这个具体要看原理图的连接情况。在example中,参考时钟经exdes、support在source模块中差分转单端,进入COMMON模块,COMMON模块就是图中绿色部分的原语,例化根据IP核的配置选择PLL0还是1,都可以选。此处需要注意,PLL的前级叫做PLL0_OUTREFCLK,后级叫做PLL0OUTCLK,后级PLL0OUTCLK后面的操作交给了GT IP核,ip核生成了TXOUTCLK和RXOUTCLK,然后example中source文件调用专用mmcm模块生成用户时钟txuseclk2_i(rxuseclk2_i)和GT逻辑时钟txuseclk_i(rxuseclk_i)。

7.效果

1/16图

屏幕显示图