静态时序分析Static Timing Analysis3——特殊路径(多周期、半周期、伪路径)的时序检查

前言

2023.4.12

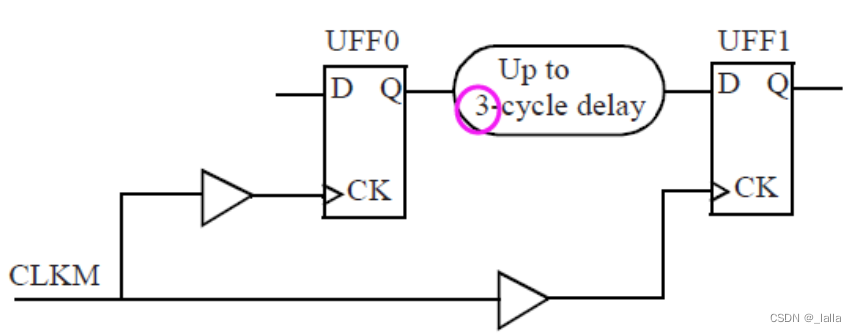

一、多周期路径

对于建立时间,要设置为N(向后移);对于保持时间,要设置为N-1(向前移)。

create_clock -name CLKM -period 10 [get_ports CLKM]set_multicycle_path 3 -setup -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

set_multicycle_path 2 -hold -from [get_pins UFF0/Q] -to [get_pins UFF1/D] //把建立时间检查点向前移两个周期

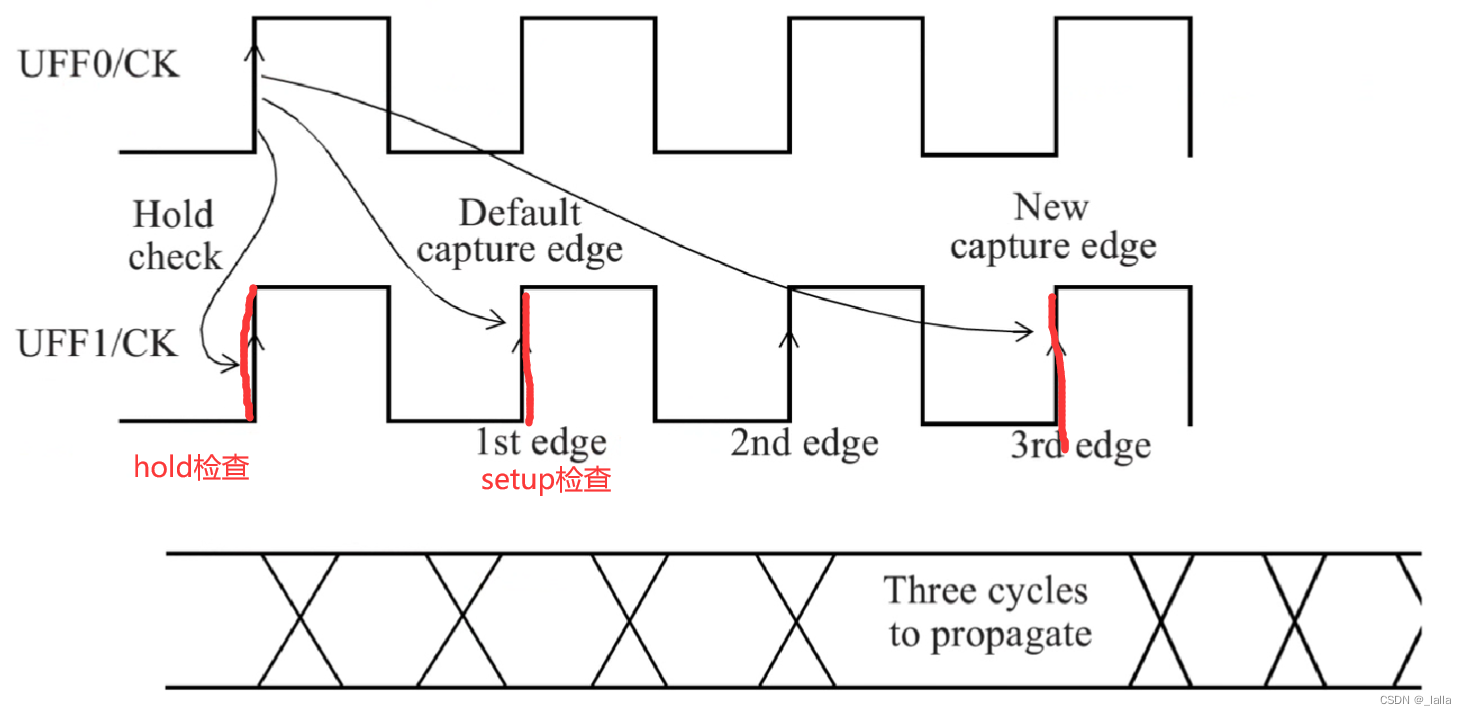

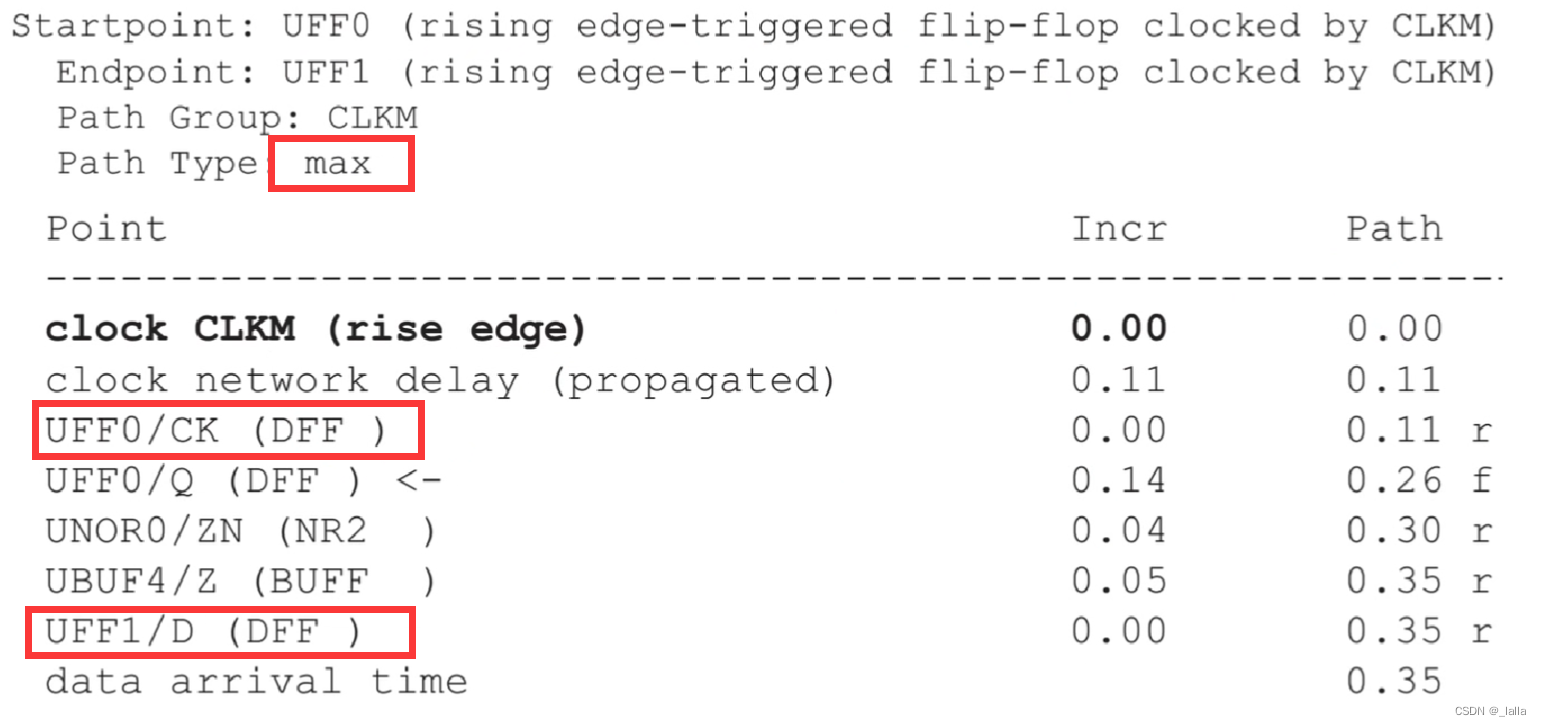

1、建立时间检查

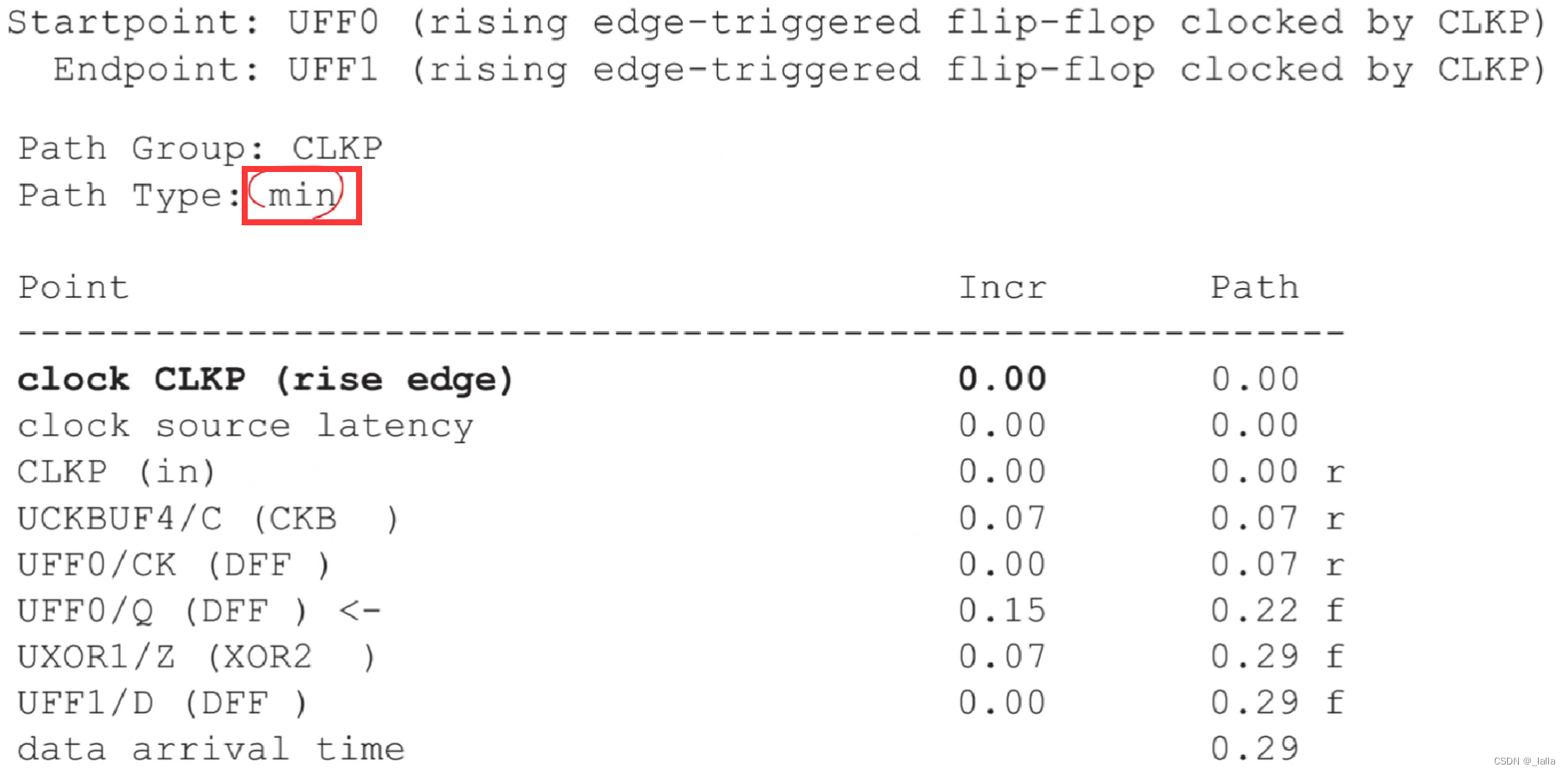

2、保持时间检查

本来默认的保持时间检查边沿是建立时间检查的前一个周期,在这里第三个周期检查建立时间,理论上第二个周期检查,但是这样对于保持时间的时序要求太严格了,也不符合我们实际的需求,需要保持这么多个周期,因此把保持时间检查节点向前移了两个周期。

所以时钟边沿从0开始了

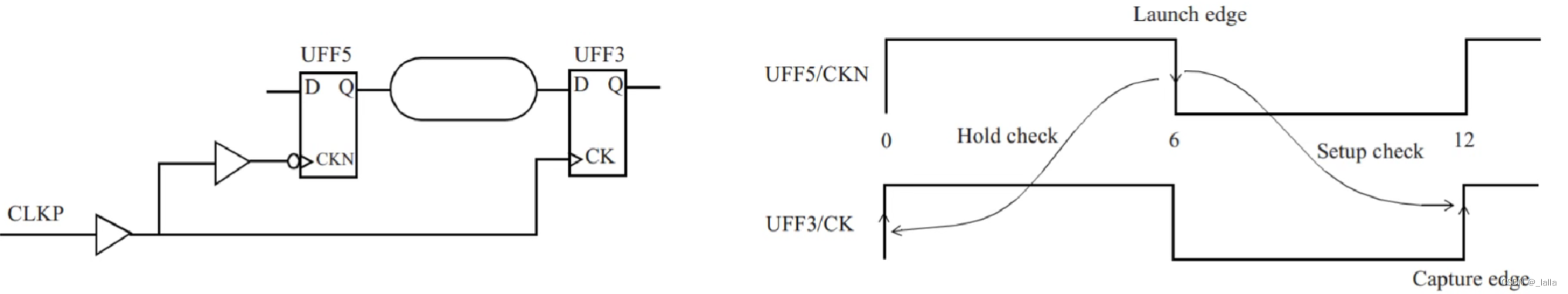

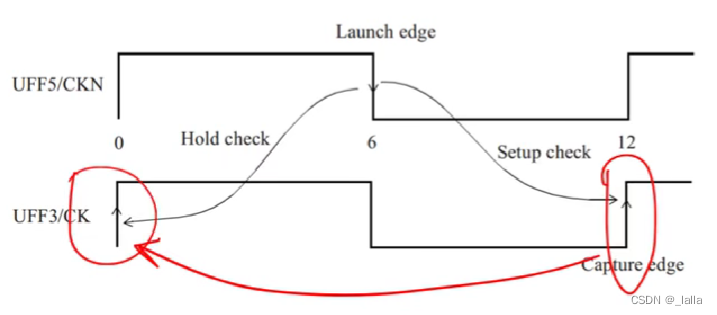

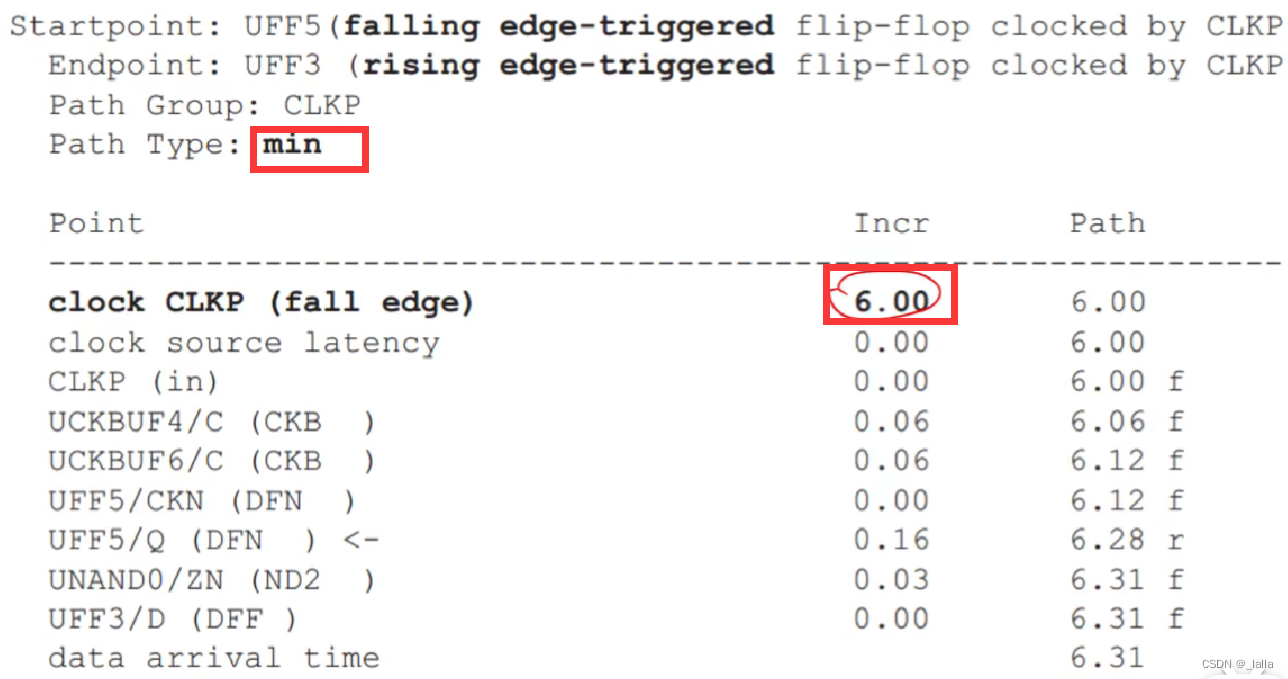

二、半周期路径

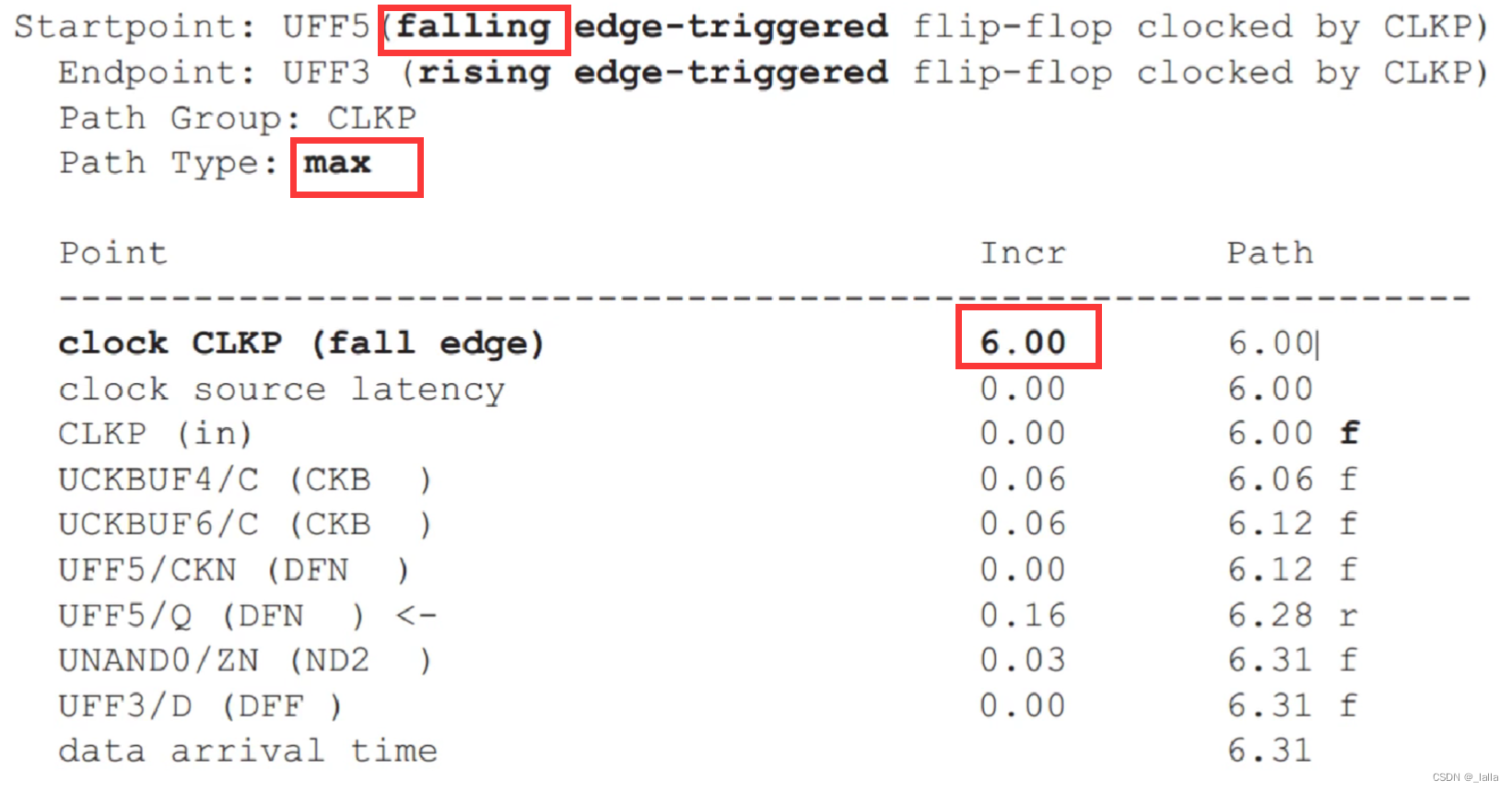

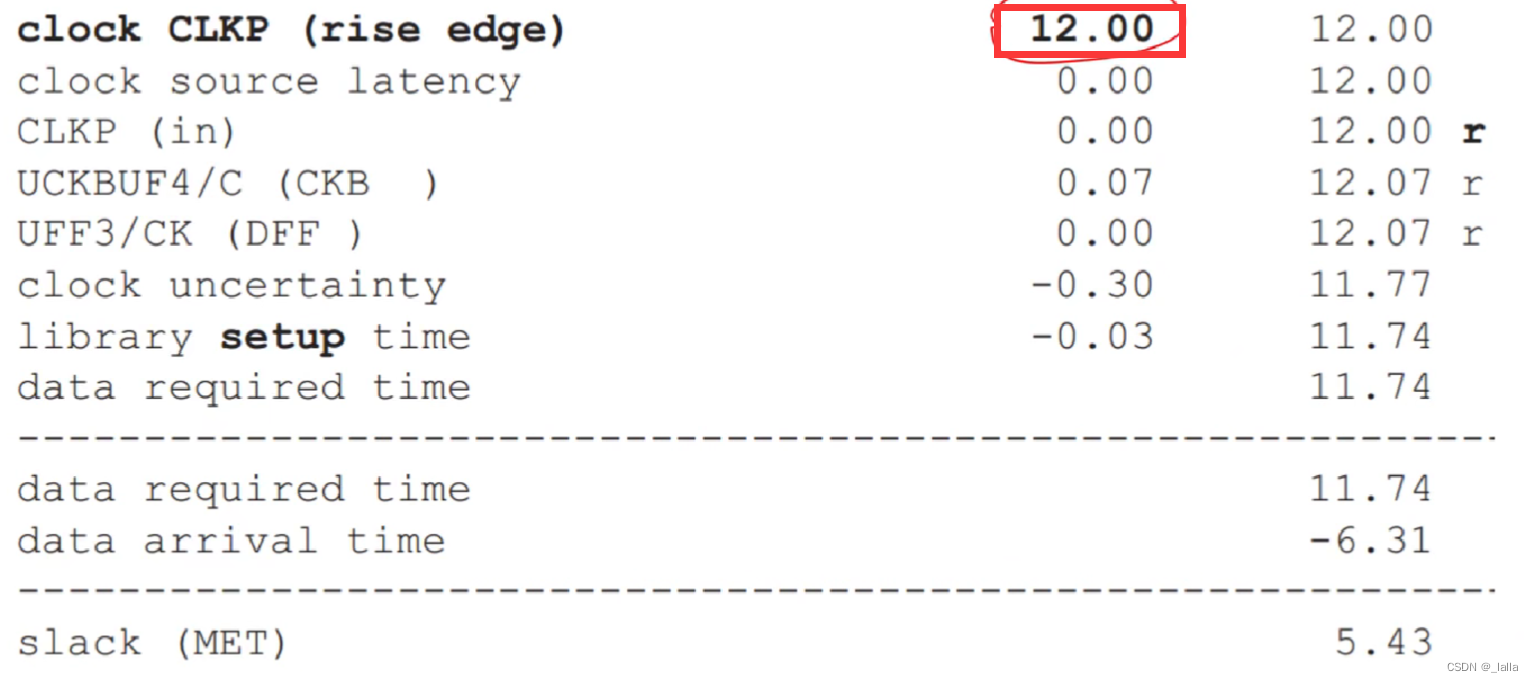

前者下降沿发送数据,后者上升沿采集数据,留给中间组合逻辑的时间就只剩下半个周期。

在半周期路径中,保持时间很容易满足,而建立时间要求比较严格。(hold很难修改违例)

1、建立时间检查

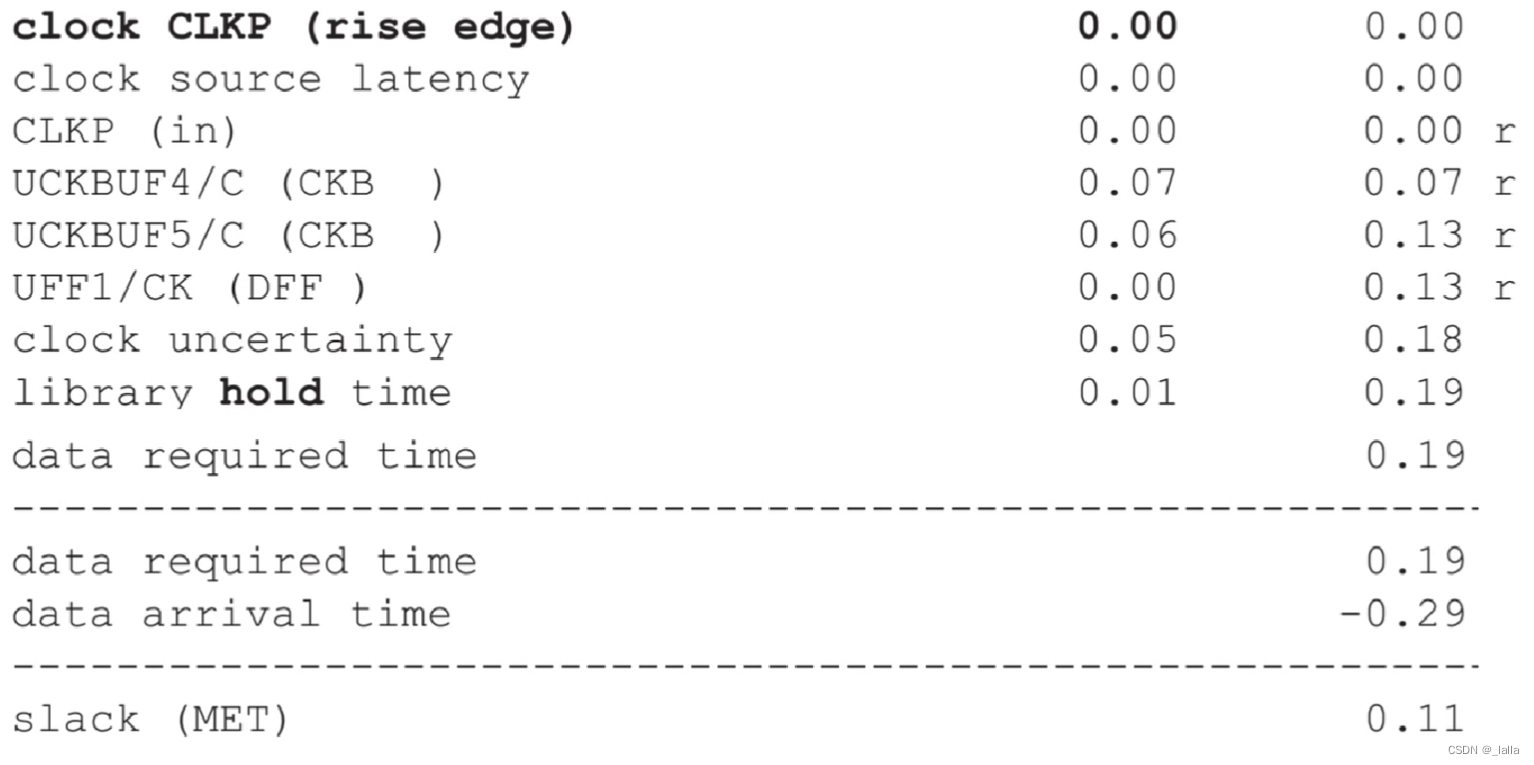

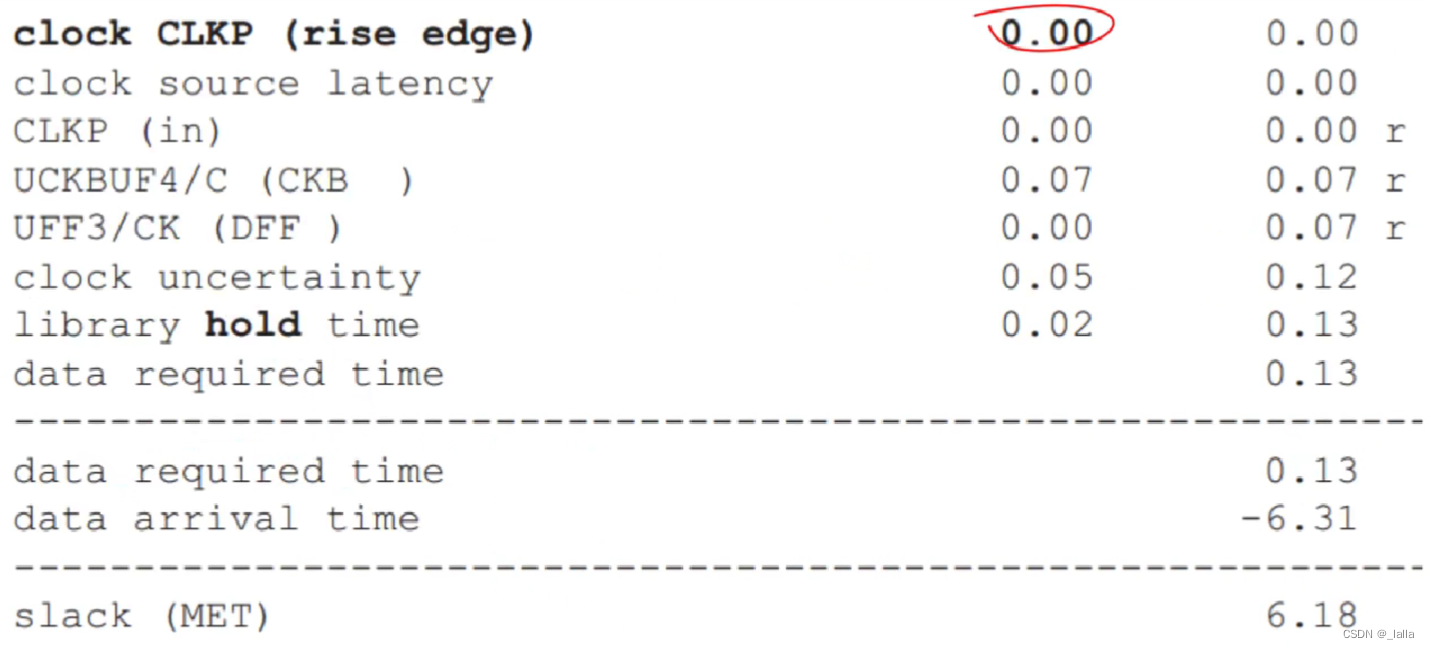

2、保持时间检查

保持时间检查周期默认就在检查时间的前一个时钟周期,因此在下图中的0时刻。

三、伪路径

- 伪路径,STA不会去分析,一方面提高分析的准确性,另一方面,提高软件PT运行的速度。

- 跨时钟域信号涉及的路径都不用STA,所以

跨时钟域的路径都需要设置伪路径。 - 设置过多的伪路径,可能会使得仿真速度变慢。

- 尽量少使用

through这种方式,推荐使用第一种,分别指定两个时钟域,更加准确

set_false_path -from [get_clocks SCAN_CLK] -to [get_clocks CORE_CLK]set_false_path -through [get_pins UMUX0/S] //通过这个pin的路径都不分析set_false_path -through [get_pins SAD_CORE/RSTN]set_false_path -to [get_ports TEST_REG*] //以这个pin结尾的都是伪路径set_false_path -through UINV/Z -through UAND0/Z //按顺序依次通过上述pin的是伪路径