【STM32】基础知识 第四课 编译 下载

【STM32】基础知识 第四课 编译 & 下载

- MDK5 编译例程

-

- 编译数据类型

- 配置下载工具

- STM32 启动模式 (M3 和 M4)

- 硬件连接

- JTAG/SWG 调试原理概述

MDK5 编译例程

编译数据类型

| 数据类型 | 占用 Flash or SRAM | 说明 |

|---|---|---|

| Code | Flash | 代码 |

| RO-Data | Flash | 只读数据, 一般指 const 修饰的数据 |

| RW-Data | Flash and SRAM | 初值为非 0 的可读可写数据 |

| ZI-Data | SRAM | 初值为 0 的可读可写数据 |

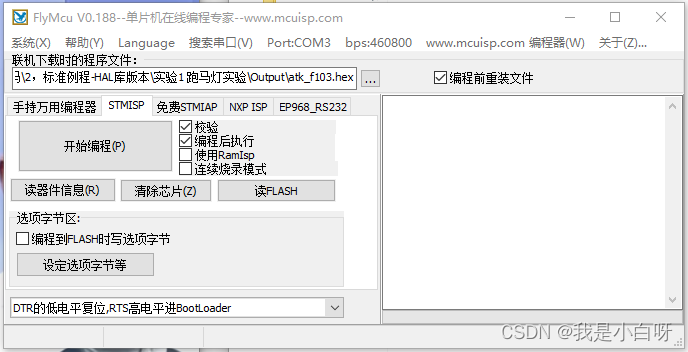

配置下载工具

- 搜索并选择 CH340 虚拟的串口, 然后设置波特率

- 选择 hex 文件 (在 Output 文件夹)

- 勾选 “编程前重装文件”

- 勾选 “校验” 和 “编程后执行”

- 不要勾选 “编程到 FLASH 时写选项字节”

- 选择 “DTR 的低电平复位, RTS 高电平进 BootLoader”

代码:

#include "./SYSTEM/sys/sys.h"

#include "./SYSTEM/delay/delay.h"

#include "./SYSTEM/usart/usart.h"

#include "./BSP/LED/led.h"int main(void)

{HAL_Init(); /* 初始化HAL库 */sys_stm32_clock_init(RCC_PLL_MUL9); /* 设置时钟, 72M */delay_init(72); /* 初始化延时函数 */led_init(); /* 初始化 LED */while(1){LED0(0); /* LED0 亮 */LED1(1); /* LED1 灭 */delay_ms(500);LED0(1); /* LED0 灭 */LED1(0); /* LED1 亮 */delay_ms(500);}

}

STM32 启动模式 (M3 和 M4)

| 引脚 BOOT1 | 引脚 BOOT0 | 启动模式 | 说明 |

|---|---|---|---|

| X | 0 | 主闪存存储器 | 主闪存存储器 |

| 0 | 1 | 系统存储器 | 系统存储器被选为启动区域 |

| 1 | 1 | 内置 SRAM | 内置 SRAM 被选为启动区域 |

ISP 下载程序一般步骤:

- BOOT0 接高电平, BOOT1 接低电平

- 按复位键

程序执行一般步骤:

- BOOT0 接低电平, BOOT1 接任意

- 按复位键

硬件连接

- 连接 12V 直流电源供电

- 按下电源开关

- DAP 通过 20P 排针连接开发板, 另一端连接电脑, 显示蓝色常亮为正常

- BO 和 B1 通过短路帽连接 GND

- 上电后确保 PWR 电源灯常亮 (蓝色)

JTAG/SWG 调试原理概述

Cortex-M 内核含有硬件调试模块, 该模块可在取指 (指令断点) 或访问数据 (数据断点) 时停止. 内核停止时, 可以查询内核的内部状态和系统的外部状态. 完成查询后, 可恢复程序执行.

| SWj-SP 端口引脚名称 | JTAG 调试接口类型 | 描述 | SW 调试接口类型 | 调试功能 | 引脚分配 |

|---|---|---|---|---|---|

| JTMS/SWDIO | 输入 | JTAG 模式选择 | 输入/输出 | 调试功能 | PA13 |

| JTCK/SWCLK | 输入 | JTAG 时钟 | 输入 | 串行时钟 | PA14 |

| JTDI | 输入 | JTAG 数据输入 | - | - | PA15 |

| JTDO/TRACESWO | 输出 | JTAG 数据输出 | - | 跟踪时为 TRACESWO 信号 | PB3 |

| JNTRST | 输入 | JTAG 模块复位 | - | - | PB4 |

引脚分配:

| 可用的调试端口 | PA13/JTMS/SWDIO | PA14/JTCK/SWCLK | PA15 / JTDI | PB3/JTDO | PB4 / NJTRST |

|---|---|---|---|---|---|

| 全部 SWJ (JTAG-DP + SW-DP) 复位状态 | X | X | X | X | X |

| 全部 SWJ (JTAG-DP + SW-DP), 但不包括 NJTRST | X | X | X | X | |

| 禁止 JTAG-DP 和使能 SW-DP | X | X | |||

| 禁止 JTAG-DP |

F1 系列可以通过 AFIO_MAPR 寄存器的 SWJ_CFG [2:0] 位来释放部分或者全部 SWJ-DP 引脚. F4/F7/H7 系列默认全部 SWJ-DP 引脚复用功能并映射到复用功能 0 (AF0).

出处: 笔记摘自正点原子