二、总线频率设置

总线频率设置源码

# < board\\vbird\\mini2440\\lowlevel_init.S >

#define BWSCON 0x48000000

/* BWSCON */

#define DW8 (0x0)

#define DW16 (0x1)

#define DW32 (0x2)

#define WAIT (0x1<<2)

#define UBLB (0x1<<3)

#define B1_BWSCON (DW32)

#define B2_BWSCON (DW16)

#define B3_BWSCON (DW16 + WAIT + UBLB)

#define B4_BWSCON (DW16)

#define B5_BWSCON (DW16)

#define B6_BWSCON (DW32)

#define B7_BWSCON (DW32)

/* BANK0CON */

#define B0_Tacs 0x0 /* 0clk */

#define B0_Tcos 0x0 /* 0clk */

#define B0_Tacc 0x7 /* 14clk */

#define B0_Tcoh 0x0 /* 0clk */

#define B0_Tah 0x0 /* 0clk */

#define B0_Tacp 0x0

#define B0_PMC 0x0 /* normal */

/* BANK1CON */

#define B1_Tacs 0x0 /* 0clk */

#define B1_Tcos 0x0 /* 0clk */

#define B1_Tacc 0x7 /* 14clk */

#define B1_Tcoh 0x0 /* 0clk */

#define B1_Tah 0x0 /* 0clk */

#define B1_Tacp 0x0

#define B1_PMC 0x0

#define B2_Tacs 0x0

#define B2_Tcos 0x0

#define B2_Tacc 0x7

#define B2_Tcoh 0x0

#define B2_Tah 0x0

#define B2_Tacp 0x0

#define B2_PMC 0x0

#define B3_Tacs 0x0 /* 0clk */

#define B3_Tcos 0x3 /* 4clk */

#define B3_Tacc 0x7 /* 14clk */

#define B3_Tcoh 0x1 /* 1clk */

#define B3_Tah 0x0 /* 0clk */

#define B3_Tacp 0x3 /* 6clk */

#define B3_PMC 0x0 /* normal */

#define B4_Tacs 0x0 /* 0clk */

#define B4_Tcos 0x0 /* 0clk */

#define B4_Tacc 0x7 /* 14clk */

#define B4_Tcoh 0x0 /* 0clk */

#define B4_Tah 0x0 /* 0clk */

#define B4_Tacp 0x0

#define B4_PMC 0x0 /* normal */

#define B5_Tacs 0x0 /* 0clk */

#define B5_Tcos 0x0 /* 0clk */

#define B5_Tacc 0x7 /* 14clk */

#define B5_Tcoh 0x0 /* 0clk */

#define B5_Tah 0x0 /* 0clk */

#define B5_Tacp 0x0

#define B5_PMC 0x0 /* normal */

#define B6_MT 0x3 /* SDRAM */

#define B6_Trcd 0x1

#define B6_SCAN 0x1 /* 9bit */

#define B7_MT 0x3 /* SDRAM */

#define B7_Trcd 0x1 /* 3clk */

#define B7_SCAN 0x1 /* 9bit */

/* REFRESH parameter */

#define REFEN 0x1 /* Refresh enable */

#define TREFMD 0x0 /* CBR(CAS before RAS)/Auto refresh */

#define Trp 0x0 /* 2clk */

#define Trc 0x3 /* 7clk */

#define Tchr 0x2 /* 3clk */

#define REFCNT 1258 /* period=7.8125us, HCLK=101.25Mhz, (2048+1-7.8125*101.25) */

SMRDATA:

.word (0+(B1_BWSCON<<4)+(B2_BWSCON<<8)+(B3_BWSCON<<12)+(B4_BWSCON<<16)+(B5_BWSCON<<20)+(B6_BWSCON<<24)+(B7_BWSCON<<28))

.word ((B0_Tacs<<13)+(B0_Tcos<<11)+(B0_Tacc<<8)+(B0_Tcoh<<6)+(B0_Tah<<4)+(B0_Tacp<<2)+(B0_PMC))

.word ((B1_Tacs<<13)+(B1_Tcos<<11)+(B1_Tacc<<8)+(B1_Tcoh<<6)+(B1_Tah<<4)+(B1_Tacp<<2)+(B1_PMC))

.word ((B2_Tacs<<13)+(B2_Tcos<<11)+(B2_Tacc<<8)+(B2_Tcoh<<6)+(B2_Tah<<4)+(B2_Tacp<<2)+(B2_PMC))

.word ((B3_Tacs<<13)+(B3_Tcos<<11)+(B3_Tacc<<8)+(B3_Tcoh<<6)+(B3_Tah<<4)+(B3_Tacp<<2)+(B3_PMC))

.word ((B4_Tacs<<13)+(B4_Tcos<<11)+(B4_Tacc<<8)+(B4_Tcoh<<6)+(B4_Tah<<4)+(B4_Tacp<<2)+(B4_PMC))

.word ((B5_Tacs<<13)+(B5_Tcos<<11)+(B5_Tacc<<8)+(B5_Tcoh<<6)+(B5_Tah<<4)+(B5_Tacp<<2)+(B5_PMC))

.word ((B6_MT<<15)+(B6_Trcd<<2)+(B6_SCAN))

.word ((B7_MT<<15)+(B7_Trcd<<2)+(B7_SCAN))

.word ((REFEN<<23)+(TREFMD<<22)+(Trp<<20)+(Trc<<18)+(Tchr<<16)+REFCNT)

.word 0x32

.word 0x30

.word 0x30

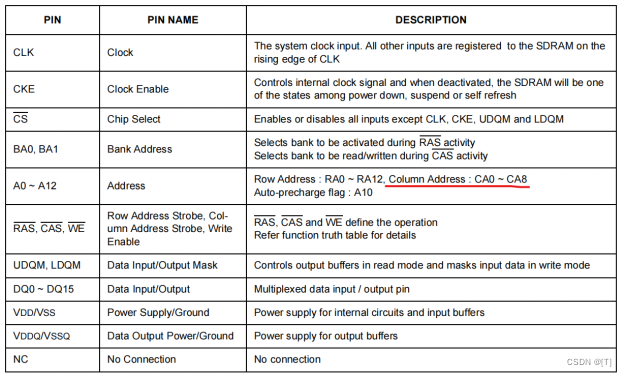

总线介绍

总线有8个Bank,每块128M(128M*8 = 1G)

0-5是ROM、SRAM等类型存储器;6-7是ROM、SRAM、SDRAM等存储器Bank

6-7两个大小可编程 (起始地址为0x30000000)

源码详解

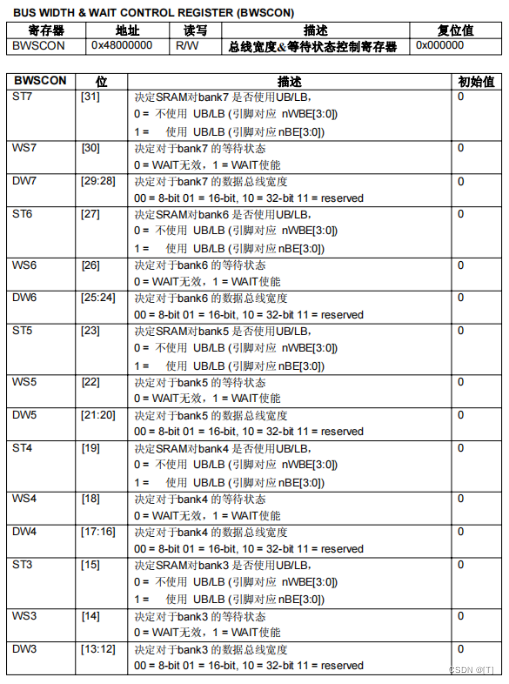

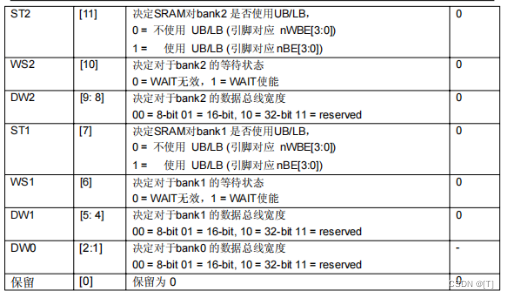

总线控制器设置

说明:主要设置Bank0-7的位宽(默认8bit)、使能WAIT(默认无效)、使能UB/LB(默认不使用)

B1_BWSCON ===》 32bit

B2_BWSCON ===》 16bit

B3_BWSCON ===》 16bit+WAIT+UBLB (DM9000 网卡)

B4_BWSCON ===》 16bit

B5_BWSCON ===》 16bit

B6_BWSCON ===》 32bit

B7_BWSCON ===》 32bit

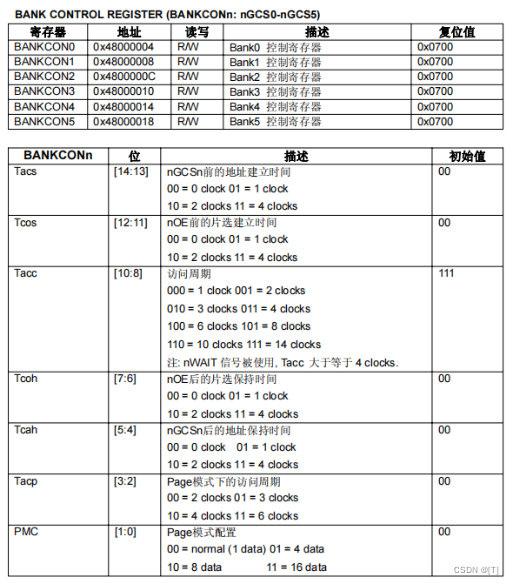

片选0-5设置

说明:Bank3为网卡DM9000,其余Bank未使用,保持默认值

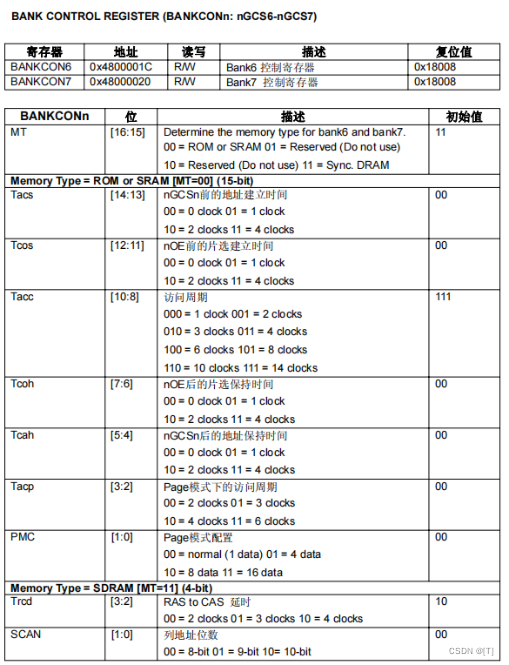

片选6-7设置

说明:Bank6-7接入了SDRAM

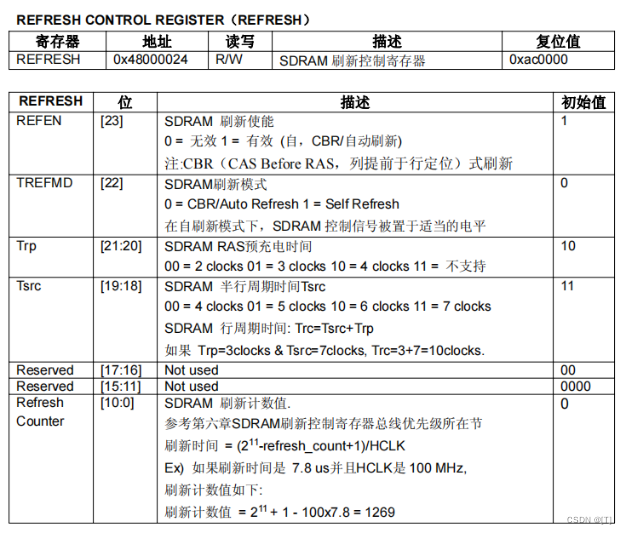

刷新控制寄存器

#define REFEN 0x1 /* Refresh enable */

#define TREFMD 0x0 /* CBR(CAS before RAS)/Auto refresh */

#define Trp 0x0 /* 2clk */

#define Trc 0x3 /* 7clk */

#define Tchr 0x2 /* 3clk */

#define REFCNT 1258 /* period=7.8125us, HCLK=101.25Mhz, (2048+1-7.8125*101.25) */

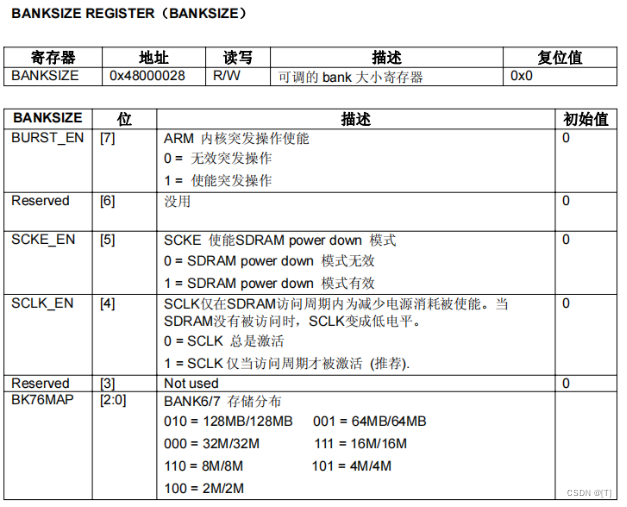

BankSize寄存器

说明:只要比实际大就行(实际为:32MB/32MB),因为bootloader和linux内核都可以检测可用空间的

0x32

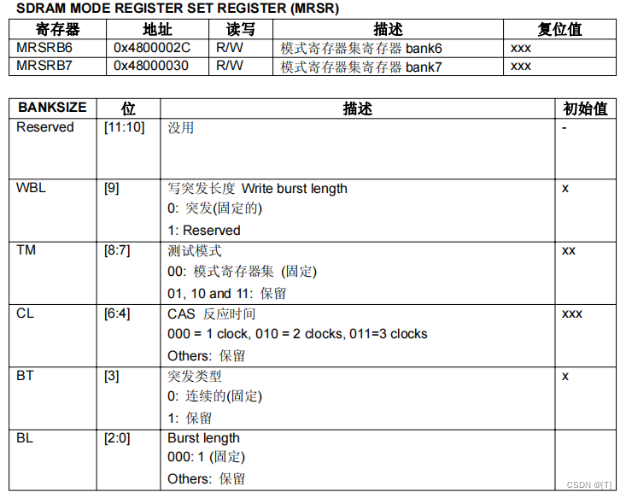

SDRAM模式寄存器

0x30