一种vivado联合vcs仿真以及verdi查看波形的方法

上一篇中提到vivado仿真xilinx官方的axi vip耗时过长、且每次缩放波形时加载慢的问题。后来用了正点原子的AXI DDR例程,将AXI DDR换成了AXI RAM进行读写测试,用以学习了解AXI的工作方式。详见此文读写AXI4接口RAM的简单示例_给米PHY的博客-CSDN博客。

在掌握了基本的AXI读写功能的情况下,感觉上文的AXI读写测试较为简单,若想要深入则必须吃透xilinx官方给的AXI VIP的例子。鉴于vivado仿真慢的问题,结合公司自带vcs和verdi软件,利用vcs进行编译、仿真,利用verdi进行波形查看,以下是本人在试错过程中得到的经验。

Xilinx官方AXI VIP的操作可参见此处:Xilinx Customer Community

前提:

在自己的home下,.cshrc中添加module add synopsys,module load synopsys,并source .cshrc,之后再在此终端中打开vivado。不进行这一步的话vivado不知道VCS的环境变量以及路径。

步骤1:生成示例工程

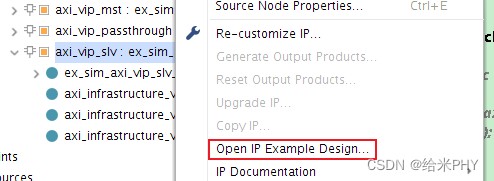

在vivado中打开AXI VIP,右键AXI VIP,点击“Open IP Example Design”,生成示例工程。

步骤2:加入波形dump语句

在“Simulation Source”中的顶层文件中加入波形dump语句。例如下图中该仿真文件激活(active),在该仿真文件中加入dump语句。

步骤3:设置仿真工具

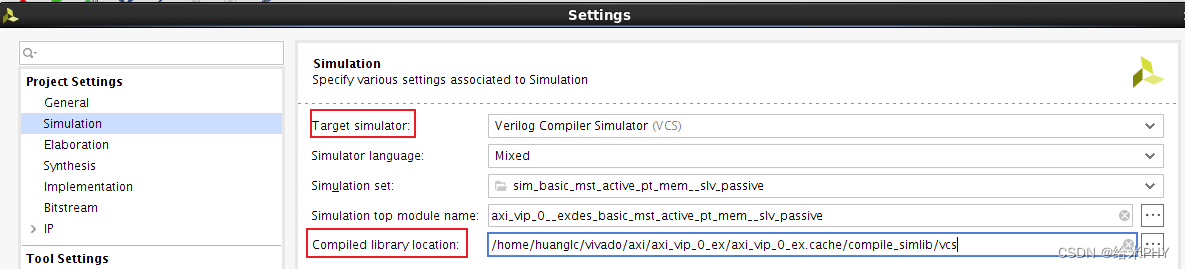

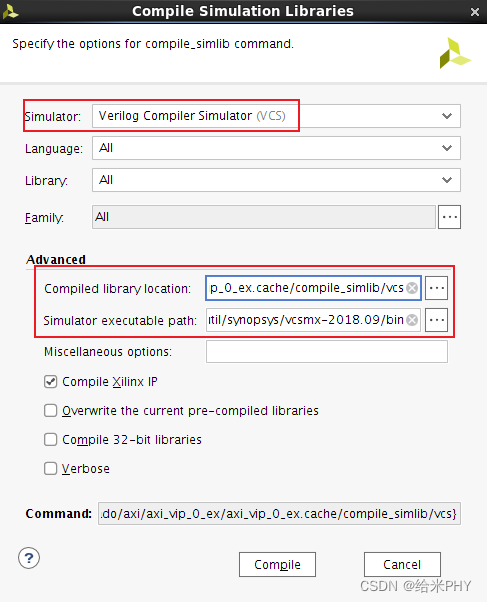

在vivado中的菜单栏点击Tool > Simulation,Target simulator点击VCS,编译库位置选择如下。

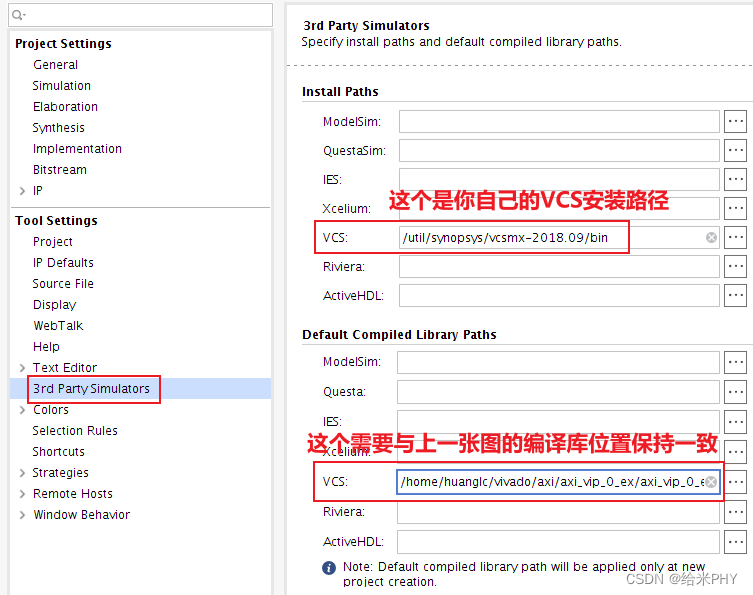

在3rd Party Simulator中设置VCS的路径,以及上一步的编译库路径。

步骤4:编译

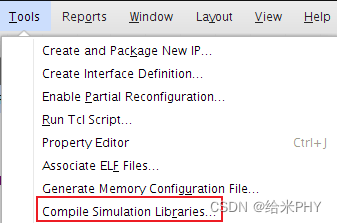

在Tool中点击Compile Simulation Libraries。

之后出来的图片如下所示,步骤3设置的路径会在此处体现。之后点击compile。

步骤5:导出simulation

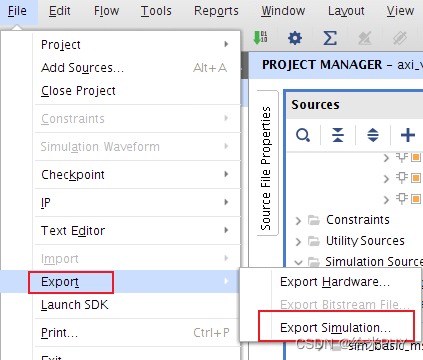

在File中,点击Export,再点击Export Simulation。

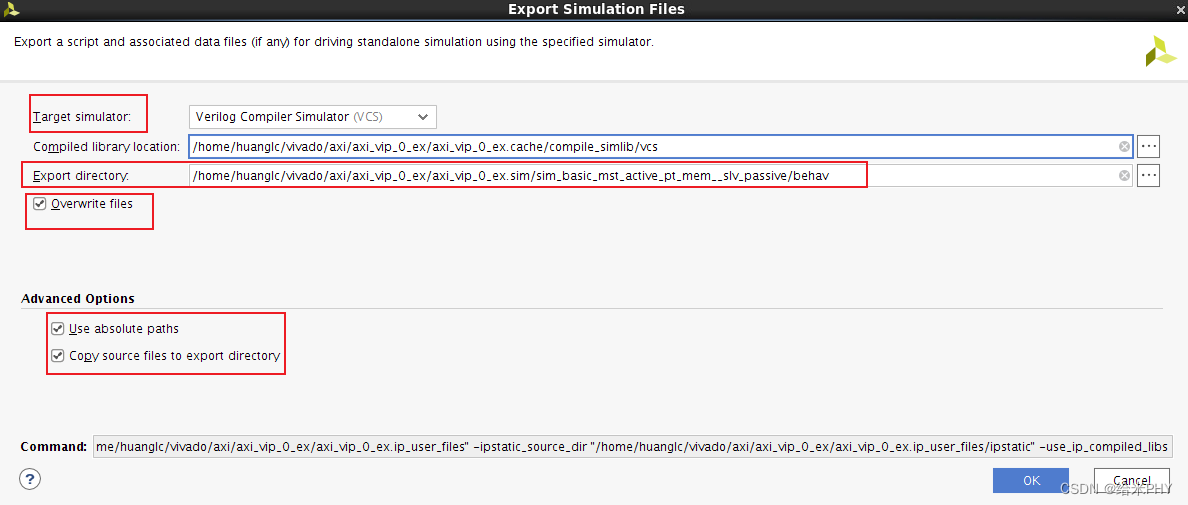

选择仿真器为VCS,编译的路径与步骤3一样, 导出的路径可以为任何地方,但是最好是在各自的仿真文件夹之下,此处我设置的如下。注意,默认的导出目录并不是我设置的目录,故需要勾选“Use absolute paths(使用绝对路径)”,以方便文件加载。

同时,由于verdi所需,故将源文件也导出。当然,Overwrite file选项可以勾选,也可以不勾选。

步骤6:运行导出的shell文件

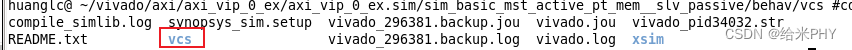

进入步骤5中的导出文件夹,该文件夹下有一个vcs目录,进入该目录。

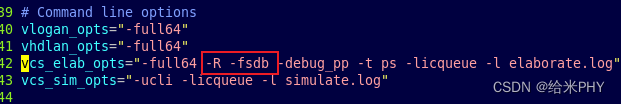

修改导出的shell文件,如下,在vcs_elab_opts中加入“-R -fsdb”选项:

保存后,在终端里键入命令 ./xxx.sh,例如我导出的是axi_vip_0__exdes_basic_mst_active_pt_mem__slv_passive.sh,直接键入命令:

./axi_vip_0__exdes_basic_mst_active_pt_mem__slv_passive.sh即可运行。运行后生成了很多文件,其中有fsdb文件以及vf文件,vf文件中是包含fsdb文件的。

步骤7:生成filelist文件

由于在步骤5中导出了源文件到vcs目录,利用python脚本将源文件的路径读出并生成filelist文件,我生成的是verdi.f文件。python脚本出自此处:用Python遍历指定文件夹下所有文件 - 知乎

之后运行该脚本,键入如下命令。

python3 xxx.py > verdi.f步骤8:用verdi查看波形

一路走下来,应该是很顺利的,那就直接键入verdi命令即可打开波形。

verdi -f verdi.f -ssf *.vf &