【从零开始学习 UVM】11.5、UVM Register Layer —— 后门访问 实战项目(RAL实战,交通灯为例)

文章目录

-

- 后门访问是什么?

- 定义后门 HDL 路径

- 示例

- sequence中的后门访问示例

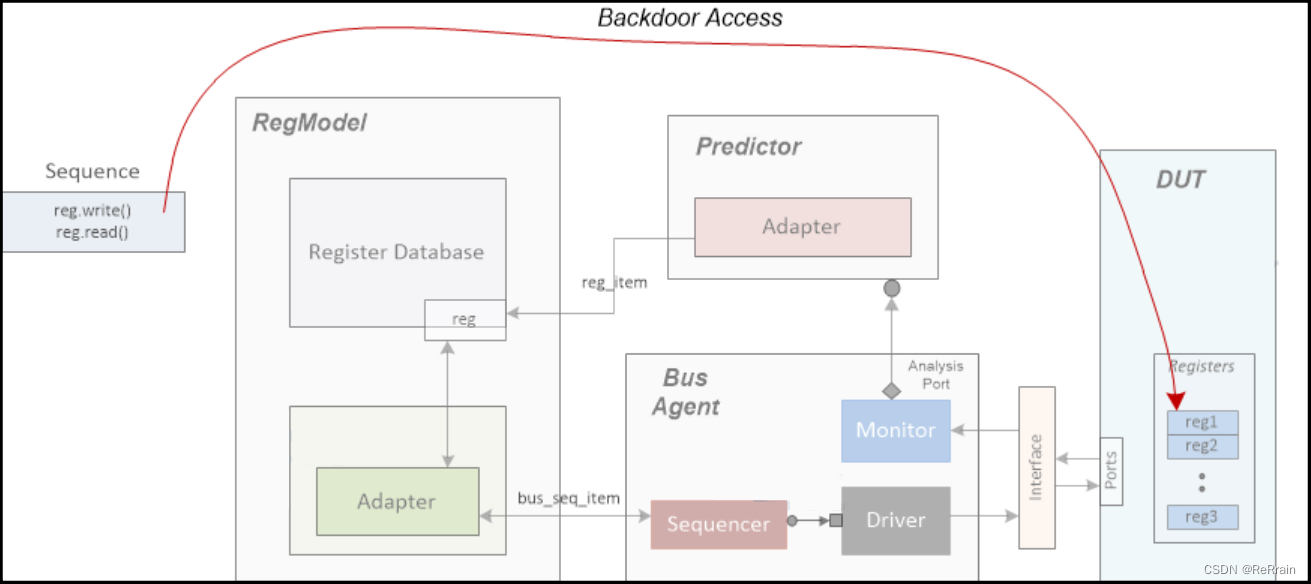

UVM寄存器模型允许使用前门访问DUT寄存器,就像我们之前在寄存器环境中看到的那样。

这意味着环境中的所有寄存器读写操作都会转换为总线事务,并驱动到设计的总线接口,就像典型系统中的任何其他硬件组件一样。由于这些访问被发送为有效的总线事务,因此它消耗了总线周期。这是验证任何设计中寄存器最推荐的方式,因为它与系统中发生的情况非常相似。

后门访问是什么?

UVM还允许使用后门访问,该方法使用仿真数据库直接访问DUT内的信号。写操作将一个值存储到信号中,读操作从寄存器信号中采样当前值。

由于寄存器是数字系统中的叶节点,在任何设计转换的中间位置存放新值不应该引起任何问题。然而,在典型总线写操作期间激活的控制逻辑将不会被激活,因此连接到它的任何逻辑可能无法按预期工作。

后门访问不需要仿真时间,因为可以直接访问HDL值而不消耗总线事务。这并非在任何设计中验证寄存器访问的推