【从零开始学习 UVM】3.11、UVM TestBench架构 —— UVM Virtual Sequencer

文章目录

-

- Virtual Sequencer 介绍

- Virtual Sequencer Example

- 完整代码

Virtual Sequencer 介绍

简单来说,Virtual Sequencer是一个包含其他seqeuncers句柄的UVM seqeuncer。

为什么我们需要这个?因为我们计划使用virtual sequence,并希望从一个中心位置控制所有sequencer。这里不需要请求类型(request type),因为该sequencer是通用的,不限于处理特定数据类型。

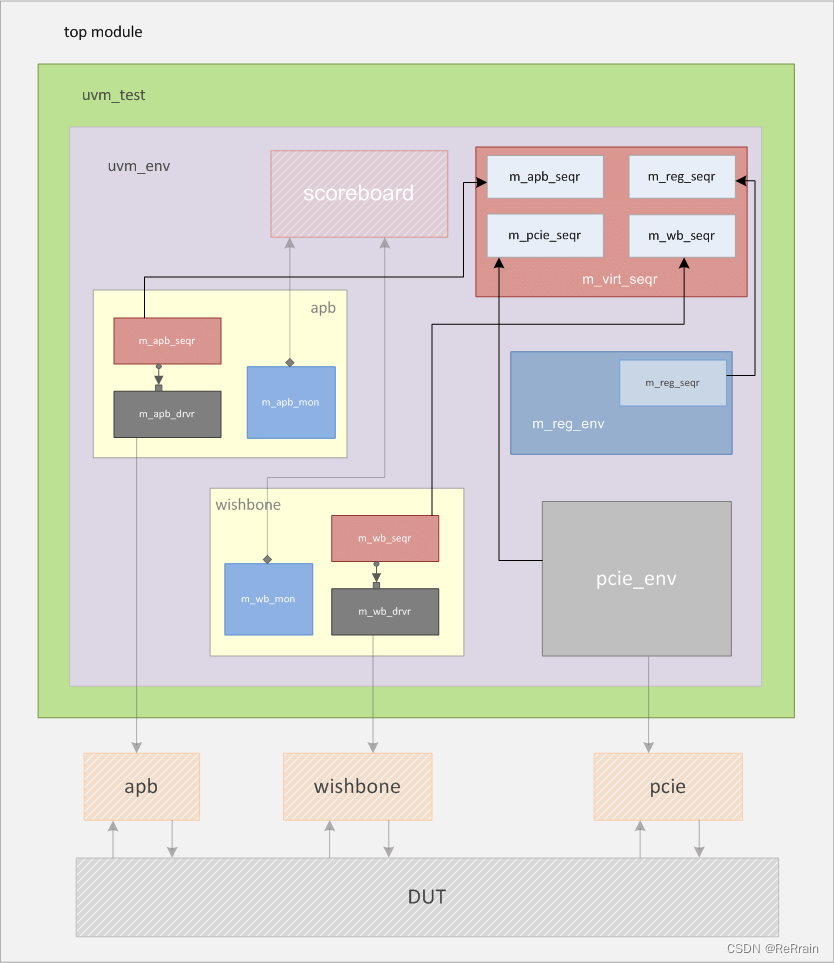

上面展示的环境具有APB代理,Wishbone代理,PCIE环境和寄存器层环境。每个组件都有自己的sequences以及它们启动的sequencer。实例化了一个名为m_virt_seqr的virtual sequencer来保存对每个单独sequencer的引用。因此,在这个virtual sequencer上执行的virtual sequence将可以访问TestBench中所有的sequencers。