I2C和SPI总线以及通信

通讯属性 概括

- Serial/parallel 串行/并行

- Synchronous/asynchronous 同步/异步

- Point-to-point / bus 点对点 总线

- Half-duplex/full-duplex 半双工/全双工

- Master-slave/ equal partners 主从/对等

- single-ending / differential 单端/差分

点对点和总线

- 点对点通讯

只有两个通讯点 only two comunication partners

没有地址请求 no addressing required - 总线通讯

若干个通信点 several communication partners

地址请求 addressing required

同步(Synchronous)和异步(Asynchronous)

- 同步

时钟接收者和时钟发送者共享一个时钟。 Clock of receiver is linker to clock of sender

快速通信。Fast communication - 异步

约定好通信速率 进行通讯。independent clocks for sender and receiver

Receiver knows the transmission speed in advance

Requires packet frame with start/stop bit

Normally an over-samping scheme is required

Communication is slower

Half duplex 半双工和Full duplex 全双工

- 半双工

只有一个通信通道。需要进行发送和接收的时候占用通道。不用的时候,应当释放信道。你发我听, 我发你听。 - 全双工

双方都可以通信。

对等(Equal partners)和 主从(Master-slave)方式

- 对等

any node may transmit if medium(媒介) is free。

Arbitration(仲裁) is required 需要仲裁 - 主从

主从设备之间没有对等的权利

只有主设备可以开始通信。Only master can start a communication.

Slave get permission to communicate form master.

e.g. USB鼠标和PC的主从通信。PC作为通信的host,USB作为通信的device。鼠标和PC的通讯时,PC按照一定的频率去读取鼠标的中断方式的通讯信息。

通信信号区分

- Single-ended 单端信号

以单线的电平高低判断信号 - differential 差分信号

用两根双绞线传递这两个差模(差分)的信号。承载差模信号的数字信号0或者1的判断,是以两根线的信号的差值来判断。

iic简介

IIC(Inter-Integrated Circuit)总线是两线式串行总线,用于连接MCU和外设。由数据线SDA和时钟线SCL构成串行总线,可发送和接受数据。高速IIC总线速率可达400Kbps以上。

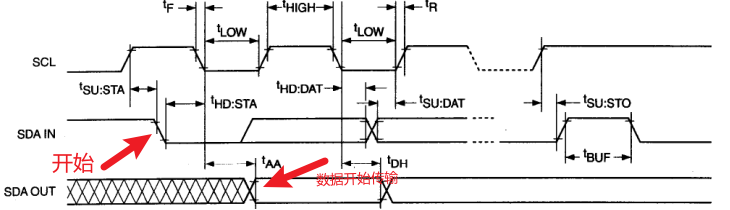

I2C总线在传送数据过程中分三种类型信号

| 信号 | SCL | SDA | |

|---|---|---|---|

| 开始信号 | 高 | 由高变低 | 开始传送数据 |

| 结束信号 | 高 | 由低变高 | 结束传送数据,可不要 |

| 应答信号 | 接收ic向发送ic发出特定的低电平,表示己收到数据 |

IIC总线时序图

spi简介

SPI(Seial Peripheral interface)串行外围设备接口。SPI(Serial Peripheral Interface) 同步串行通讯方式,适用于短距离通讯。

可用接各种外设和芯片。e.g. ADC/RTC/LCD/ROM/DAC/Sensor。

SPI是一种高速的,全双工、同步的通信总线。

spi是4线同步串行通讯接口。实现SPI的主从设备还要第5根线GND。

SPI的特点

- 串行接口 Serial Interface

- 同步 Synchronous

- 主从配置 Master-slave configuration

- 数据交换-DMA/PIO Date Exchange

- 全双工 Full duplex operation(一主)

- 灵活的时钟极性/相位格式 Flexible clock polarity/phase format

- 4到16位的可变字节帧

- 总线竞争保护

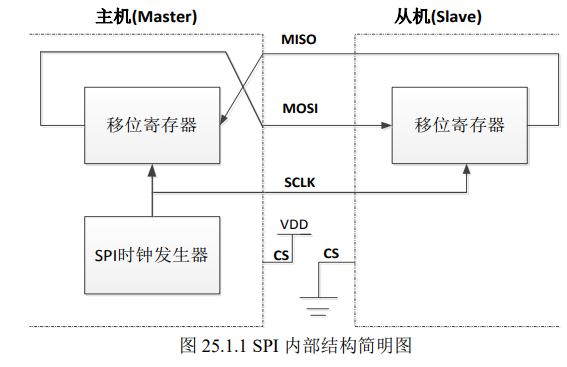

spi内部简明图

从上图看,SPI有4个线通信

| 引脚 | 描述 |

|---|---|

| MOSI(Master Out Slave In) | 主出从入,主设备发送到从设备的信号 |

| MISO(Master IN slave OUT) | 主入从出。从设备发送到主设备的信号 |

| SCK | serial clock,由主设备控制产生的SPI工作时钟,每个SCK周期完成一个bit的传输。SCK信号必须干净,有毛刺会带来严重的干扰 |

| SS/CS | Slave/Chip Select,从设备选择端,当从设备收到该段为低电平时,设备有效;对于主设备,该端平时为高电平,可以用于在有效传输周期内给出低电平选通。 |

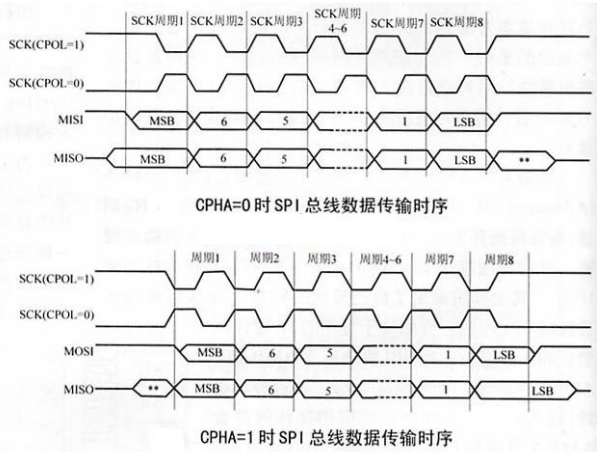

spi工作方式

spi模块要与外设进行数据交互,需要配置串行同步时钟极性和相位在相同的工作模式。

CPOL时钟极性

| CPOL | 描述 |

|---|---|

| 0 | 串行同步时钟的空闲状态为低电平 |

| 1 | 串行同步时钟的空闲状态为高电平 |

CPHA时钟相位可选择2种传输协议

| CPHA | 描述 |

|---|---|

| 0 | 在串行同步时钟的第一个跳变沿(上升或下降)数据被采样 |

| 1 | 在串行同步时钟的第二个跳变沿(上升或下降)数据被采样 |

工作流程

SS片选信号拉低(或拉高)–> 主从机双方准备传递信息,MISO MOSI引脚开始把数据准备好 --> 当时钟的第一个边沿出现时(上升沿或下降沿),开始观察各自的输入引脚进行bit采样 --> 当时钟出现第二边沿时,主从机驱动自己的输出引脚准备发送第二个bit。

传输时序

主模式

- 控制整个传输过程

- 通过SS信号选择对应的通信从节点

- 决定SCK波特率,相位,极性

- 产生SCK时钟信号

- 驱动MOSI信号

- 采用MISO信号

- CPU通过向SPIx_D写入数据来启动一次传输过程

从模式 Slave mode

- 响应主节点的信号

- 当SS信号被选通时才激活

- 根据预先约定的相位/极性来检测SCK

- 按照主机的通信速度驱动MISO信号

- 采样MOSI信号

注意点 Point to notice

- 通常,SPI是点对点结构的

- 必须预先约定SCK时钟的相位/极性和数据帧位数

- 从节点的CPU需要在数据帧开始前 将待发数据准备好并写入SPIx_D

- SCK信号必须干净不能有毛刺 SCK保证主从机都能接收的范围