【lwIP(第一章)】lwIP入门

lwIP是一个小型开源的TCP/IP协议栈(阉割的TCP/IP协议)

lwIP适用于:云台接入、无线网关、远程模块、工控控制器、嵌入式NAT无线路由器、网络摄像头………

目录

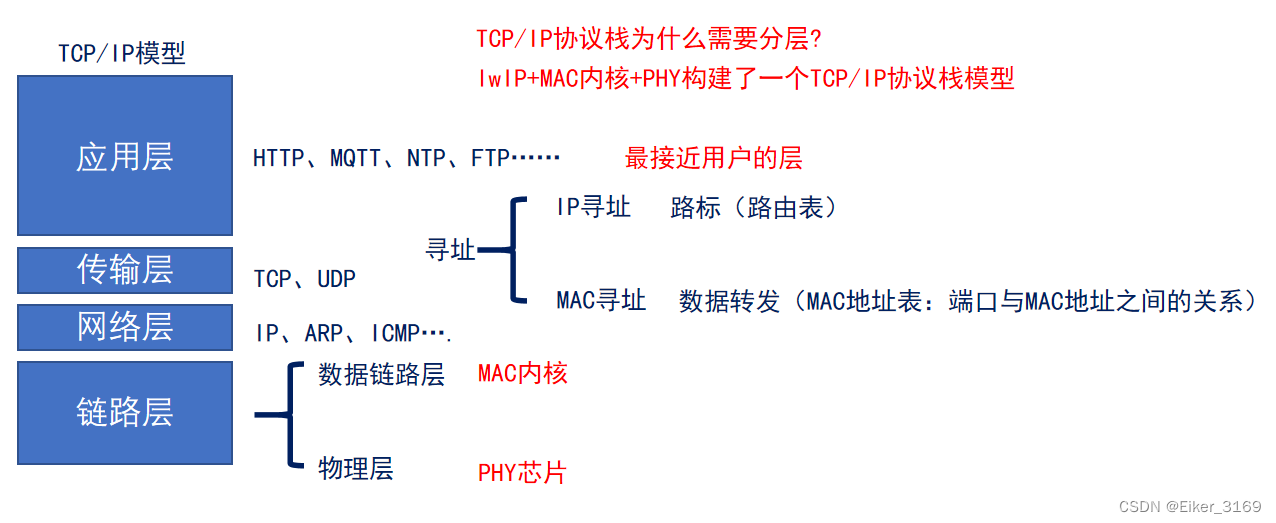

一、TCP/IP协议栈

1. TCP/IP协议栈结构体

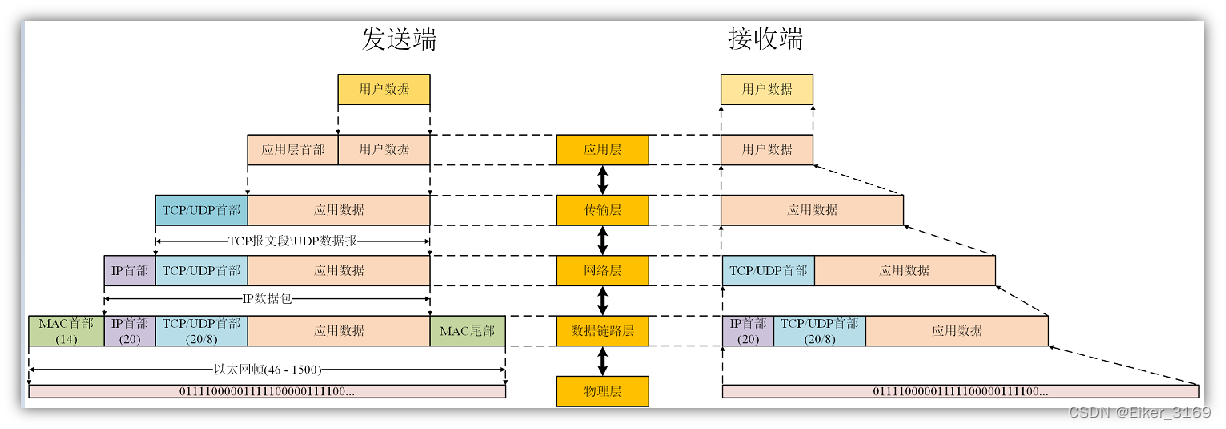

2. TCP/IP协议栈的数据封装与解封装

封装:数据添加各层协议的首部;解封装:在各层间除去自层的首部

二、lwIP结构

三、MAC简介

1. MAC内核的特性:

① 传输速率:支持外部PHY接口实现10/100Mbit/s数据传输速率

② 协议标准:符合IEEE802.3/3u的MII和RMII接口与快速以太网PHY通信

③ 工作模式:支持全双工和半双工操作

④ 站管理接口:支持通过MDIO接口配置和管理PHY设备

⑤ 其他特性

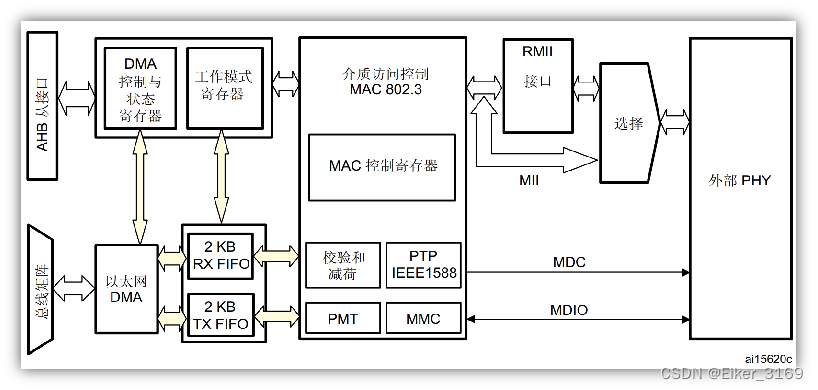

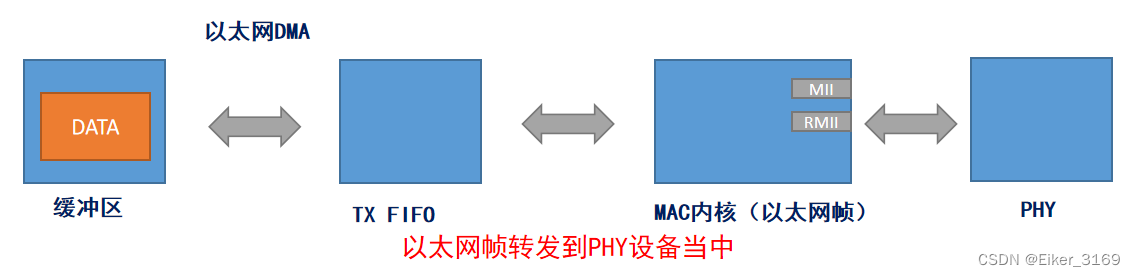

2. ST的ETH框架

STM32自带有10/100Mbit/s的以太网MAC内核,它提供地址及媒体访问的控制方式

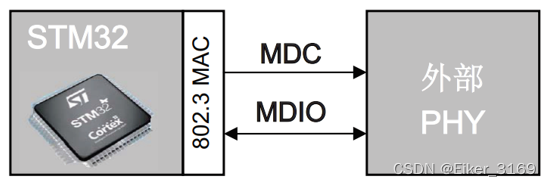

2.1 SMI站管理接口

允许应用程序通过时钟线和数据线访问任意PHY寄存器,最多支持32个PHY访问

● MDC:周期时钟引脚(最大频率为:2.5MHz)

● MDIO:数据输入/输出比特流

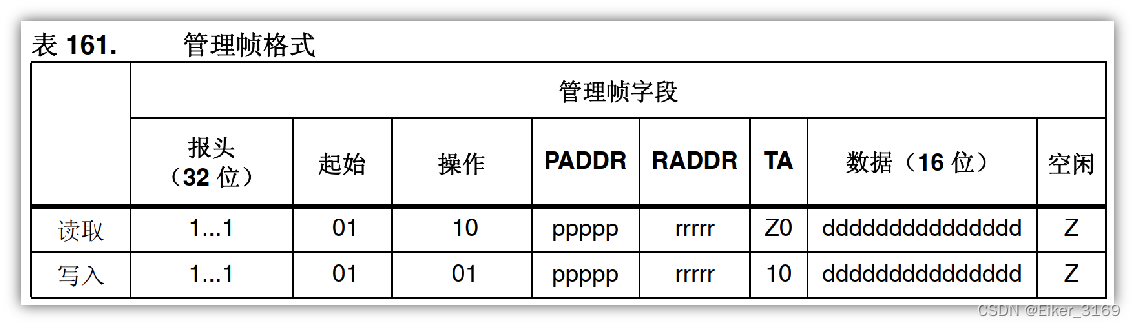

2.1.1 SMI帧格式

● PADDR:PHY地址(00_1F)

● RADDR:寄存器地址(00_1F)

● 数据位:16位数据位(PHY寄存器都是16位的)

2.2 介质接口MII、RMII

用于MAC与外接的PHY互联,支持10/100Mbit/s数据传输模式

2.2.1 MII、RMII比较

● 相同的特性:

① 支持外部PHY接口实现10/100Mbit/s数据传输速率

② 符合IEEE802.3协议标准

● 不同的特性:

① 引脚数量

② 参考时钟

③ 发送的位宽

2.2.2 MII、RMII引脚

● 介质MII接口所需要引脚数量为16个,而RMII接口所需要的引脚数量为9个

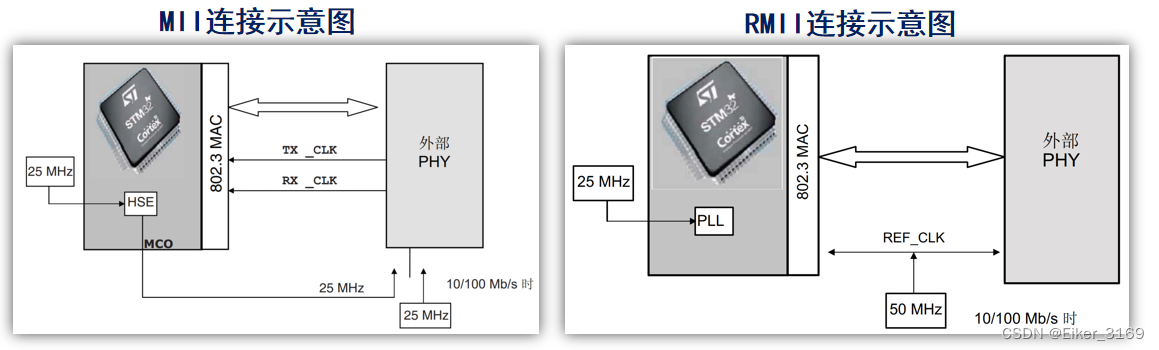

● MII介质接口的TX_CLK和RX_CLK由PHY芯片提供,它们会让MAC内核以这个时钟采集收发数据

● RMII介质接口的REF_CLK, MAC内核以这个时钟采集收发数据

注意:RX_ER和RX_DV是用来检测以太网帧是否有效性,而CRS和COL以及CRS_DV在全双工模式下无效

2.2.3 MII、RMII参考时钟

● 介质MII的参考时钟来源有两个:MCO输出25MHz以及外部晶振输出25MHz

● 介质RMII的参考时钟来源有两个:MCO经过倍频PLL输出50MHz以及外部晶振输出50MHz(必须同时提供PHY和MAC)

注意:MII接口中的TX_CLK和RX_CLK时钟是根据数据传输速率挂钩,10Mbit/s:2.5MHz;100Mbit/s:25MHz

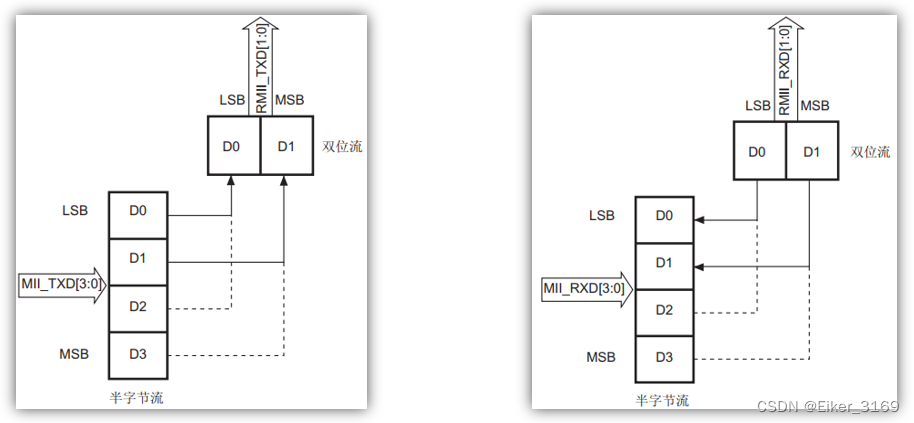

2.2.4 MII、RMII介质接口收发位宽

介质MII接口一个周期收发位宽为4位数据,而接口一个周期RMII收发位宽为2位数据