MIPI摄像头工程=7系列FPGA + OV5640(MIPI) + 15 分钟 + VITIS

项目使用东西

-

硬件

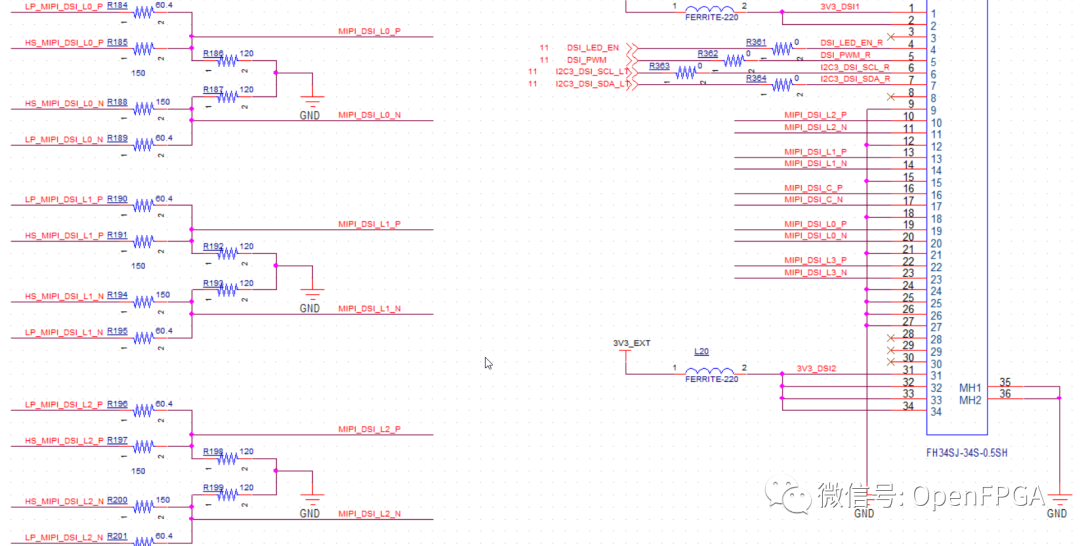

Spartan-7 SP701 FPGA 7系列FPGA+电阻网络实现的MIPI接口

OV5640 MIPI接口

-

软件

AMD Vivado 2020 版本以上

AMD Vitis 2020

介绍

MIPI 接口现在非常流行,国产FPGA目前基本都带MIPI接口,而AMD-Xilinx是从U+系列开始支持MIPI电平,从国内使用情况来看,7系列FPGA是使用最广的器件,所以这次使用的FPGA是7系列FPGA使用电阻网络实现MIPI电平的例子,具体硬件方案可以查看:

《Xilinx FPGA MIPI 接口简单说明》

搭建工程

本次使用的Vivado尽量使用2020版本以上的,MIPI的IP开始免费。

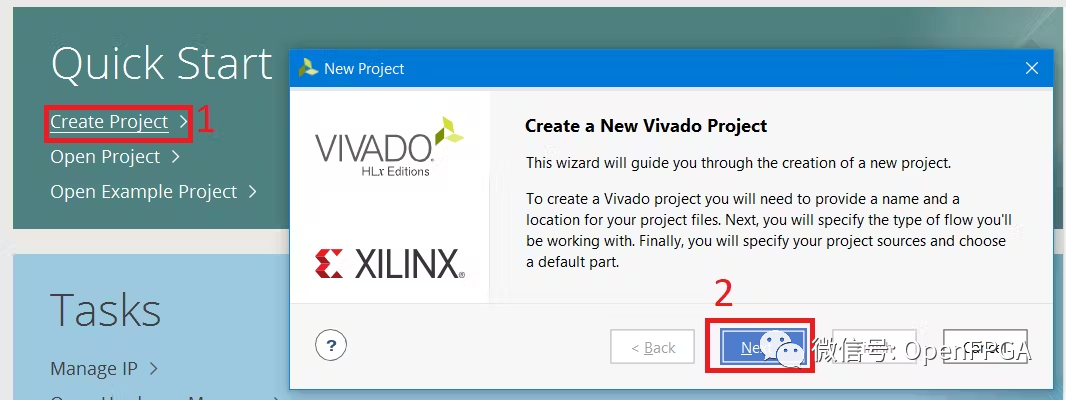

第 1 步:创建 Vivado 工程

运行 Vivado

(1)“Create project创建项目” --> (2)按“Next下一步”

指定(1) “Project name项目名称” --> (2)Specify projects directory项目目录 --> (3)设置复选框 --> (4)按“Next下一步”

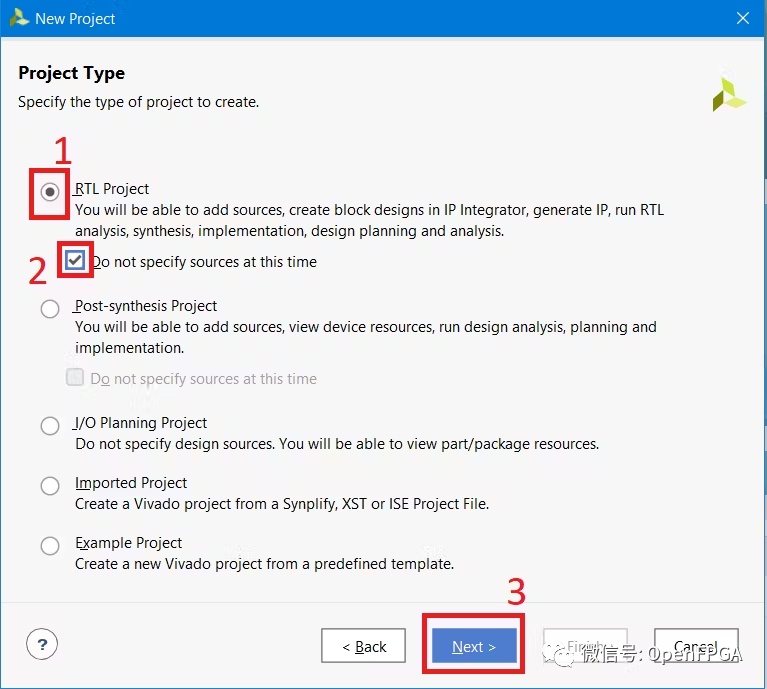

(1)选择项目类型 --> (2)设置复选框 --> (3)按“Next下一步”

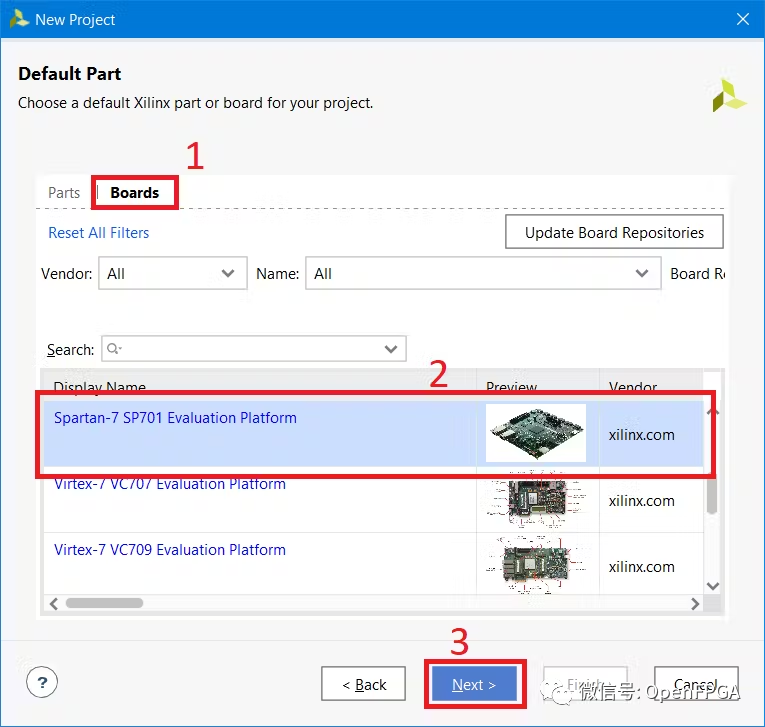

(1)选择“Boards电路板”选项卡 --> (2)查找并选择 SP701 --> (3)按“Next下一步”

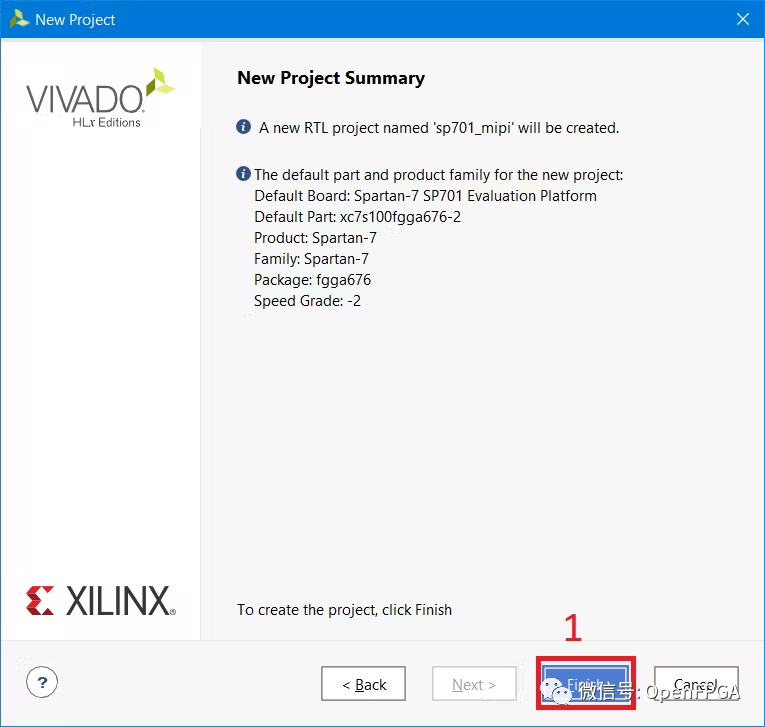

(1)按“Finish完成”

第 2 步:生成示例设计

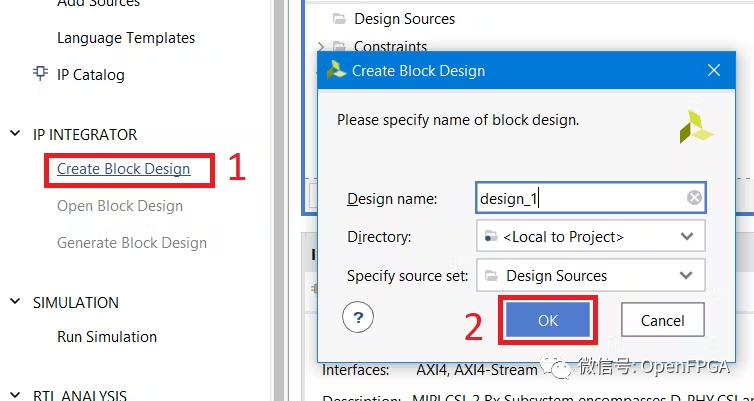

在 Vivado 中(1)“Create block design” --> (2)按“OK”

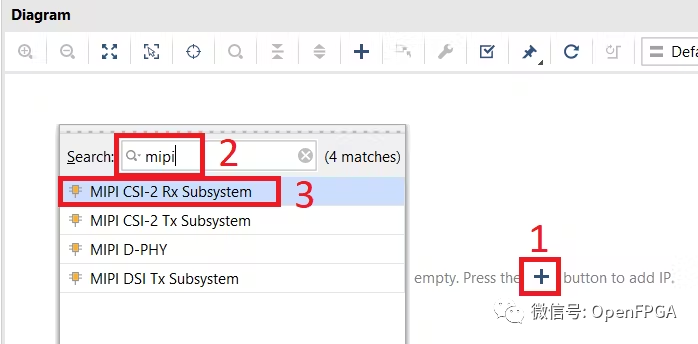

(1)按“+”或“ctrl+I” --> (2)在“Search”中键入“mipi” --> (3)双击“MIPI CSI-2 Rx 子系统”IP 核

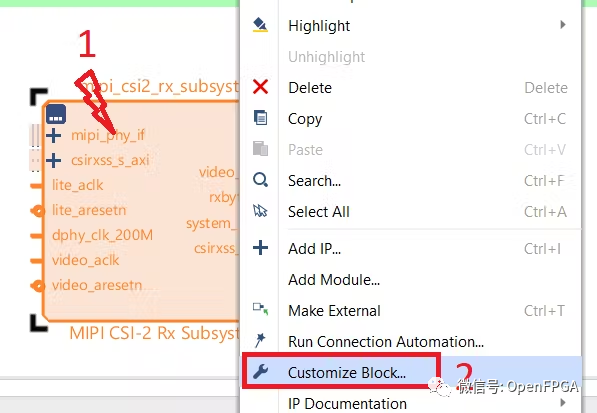

(1)右键单击 IP --> (2)选择“Customize Block”

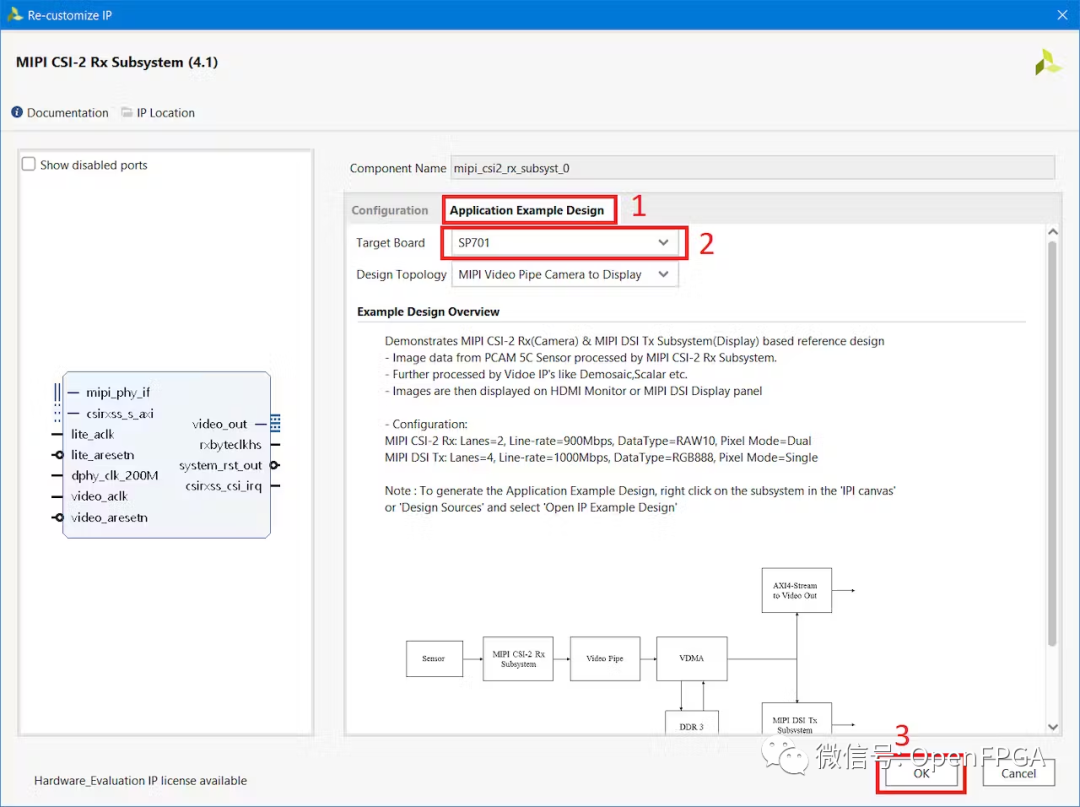

(1)打开“Application Example Design”选项卡 --> (2)选择“SP701” --> (3)按“OK”

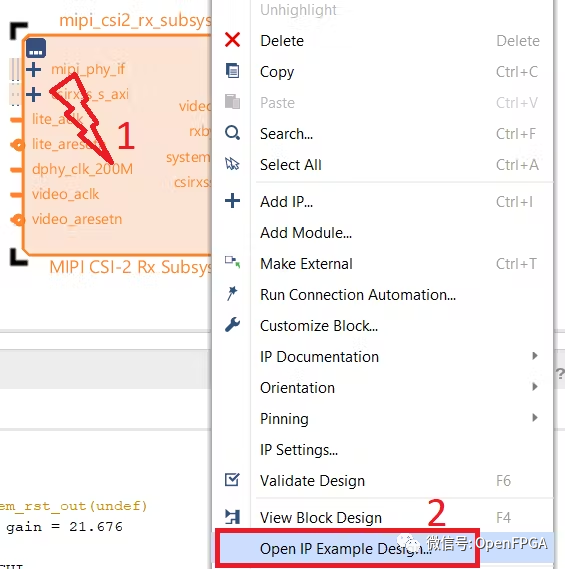

(1)右键单击 IP --> (2)选择“Open Example Design”

按“OK”保存设计更改

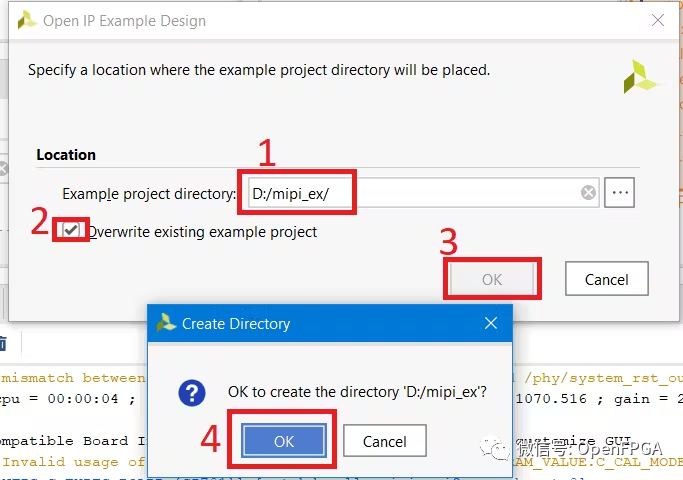

(1)指定示例项目的目录(注意:Windows 上的路径必须尽可能短) --> (2) 设置复选框 --> (3)按“OK” --> (4)按“OK”

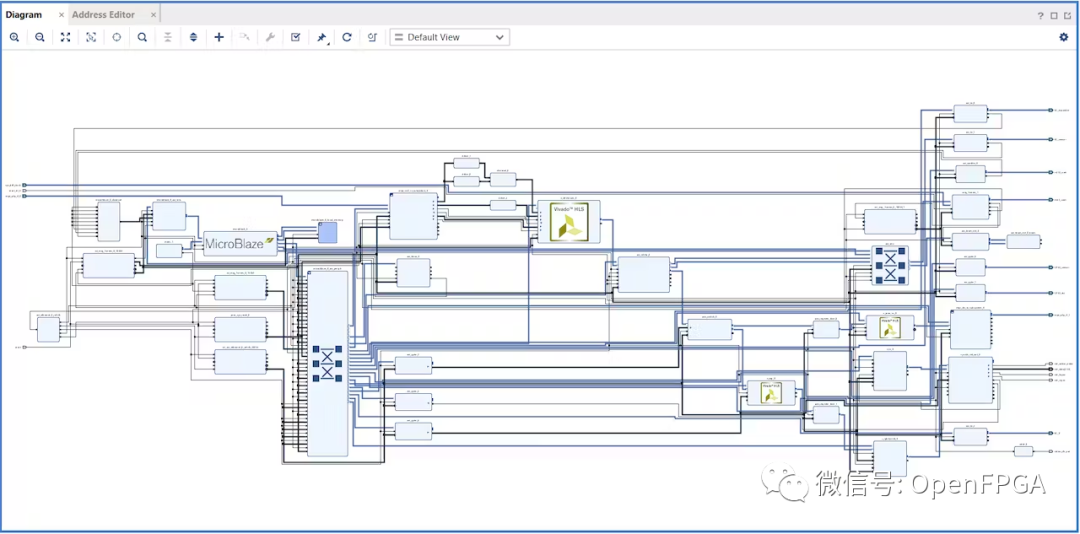

示例项目将在新的 Vivado 窗口中打开。等待几分钟完成项目的构建

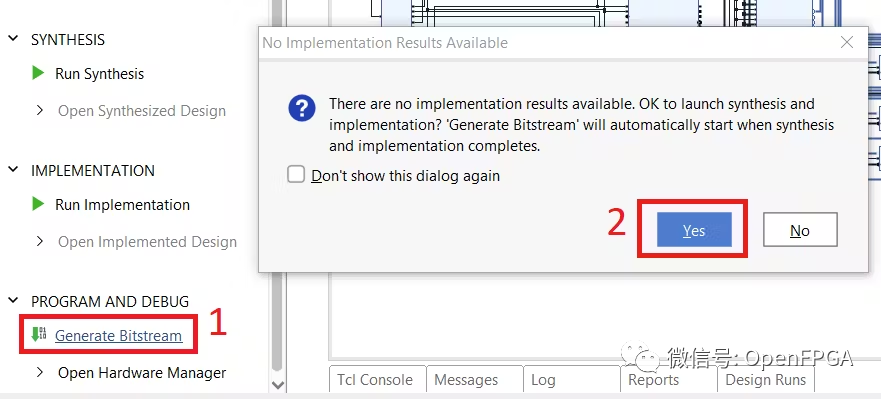

在示例项目 Vivado 中(1)“Generate bitstream” --> (2)按“YES”

等待比特流生成

第 3 步:硬件测试

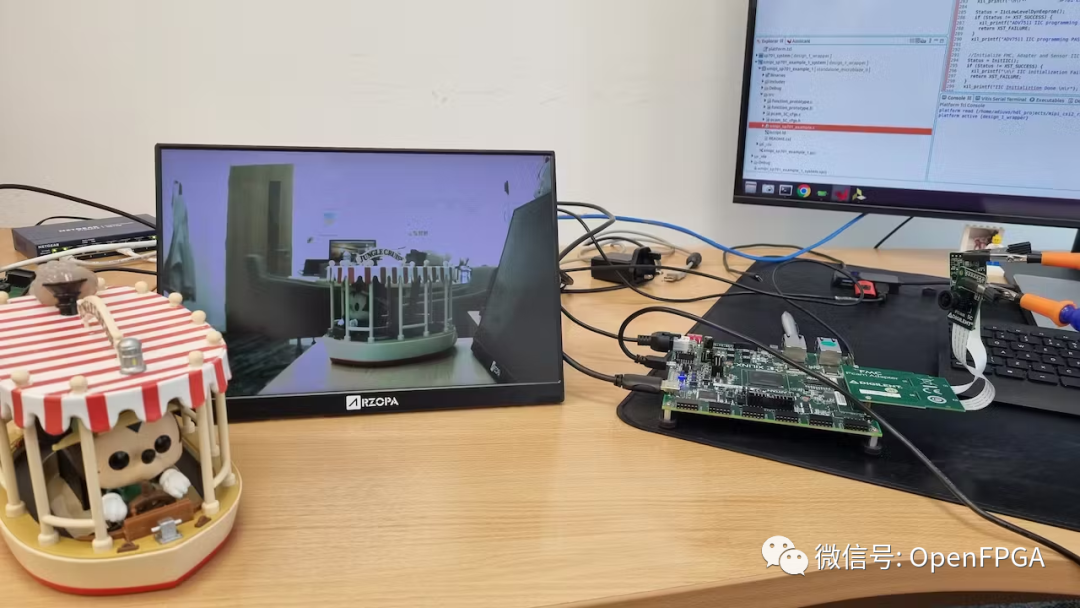

将 OV5640 sensor连接到 FPGA 板上的 MIPI CSI接口上。将 HDMI 显示器或 MIPI 显示屏连接到开发板上。

第 4 步:运行调试

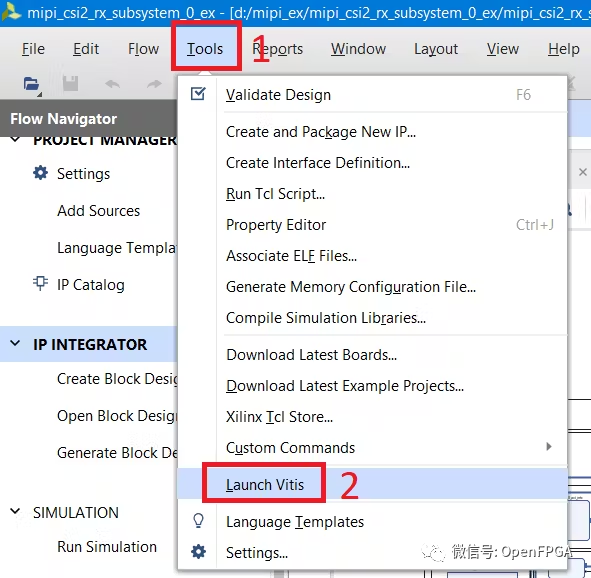

从 Vivado 打开 VITIS 软件。(1)“Tools” --> (2)“Launch VITIS”

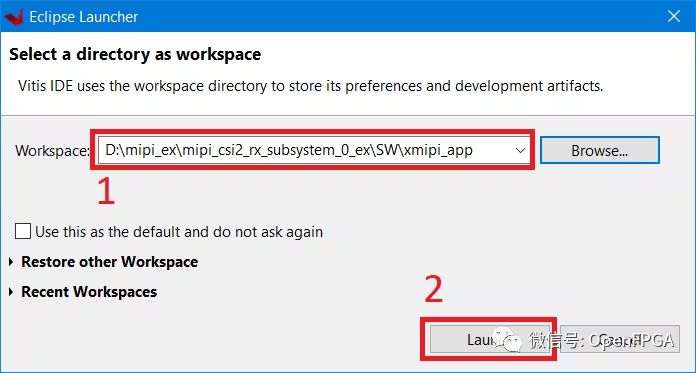

(1)指定工作区(选择历程自带的 mipi_csi2_rx_subsystem_0_ex :: SW :: xmipi_app )--> (2)“Launch”

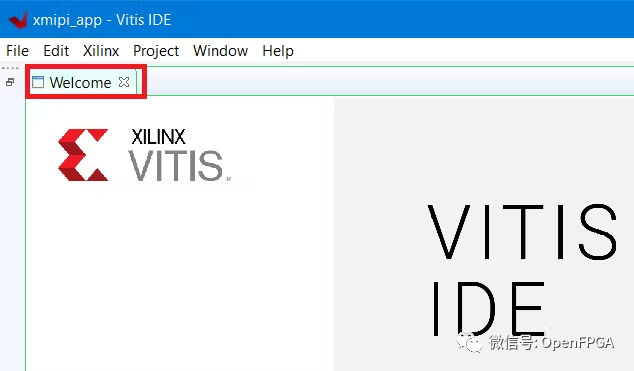

关闭 VITIS “Welcome”选项卡

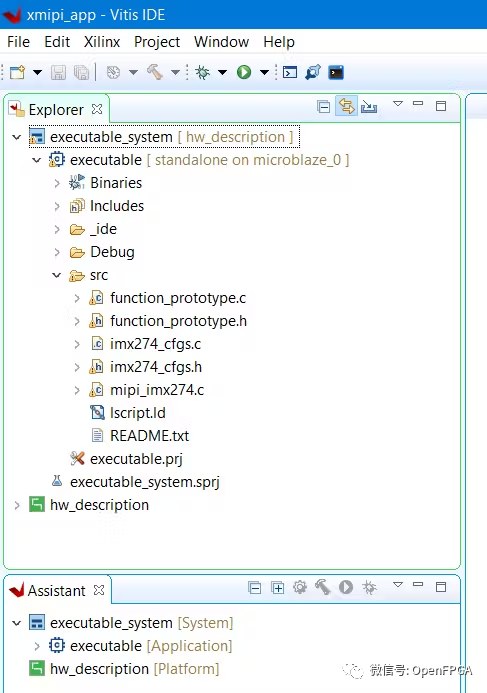

现在将看到项目的软件部分。MicroBlaze 软处理器的代码。

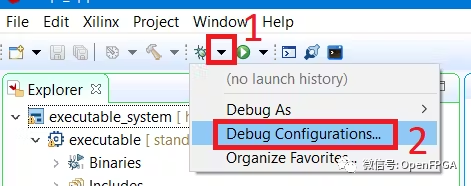

(1)按照箭头 --> (2)按“Debug Configurations”

(1) 双击“Single Application Debug (GDB)” --> (2)选择“Debugger Executable” --> (3) 指定 由 Vivado 生成bitsream.bit 文件 --> (4)设置复选框 --> (5)按“Debug”

按运行按钮并按照 串口 终端上的消息进行操作

结论

从 Vivado 为 FPGA 板上的 MIPI 接口生成示例工程非常简单。

❝

https://www.xilinx.com/products/boards-and-kits/sp701.html#resources

❞