【数字 IC / FPGA】 有关建立/保持时间计算的思考

引言

最近准备一些数字IC的机试,刷到了一些有关静态时序分析的题目。有一些比较经典的题目,在这里整理分享一下。

有什么疑问可以在评论区交流~互相进步

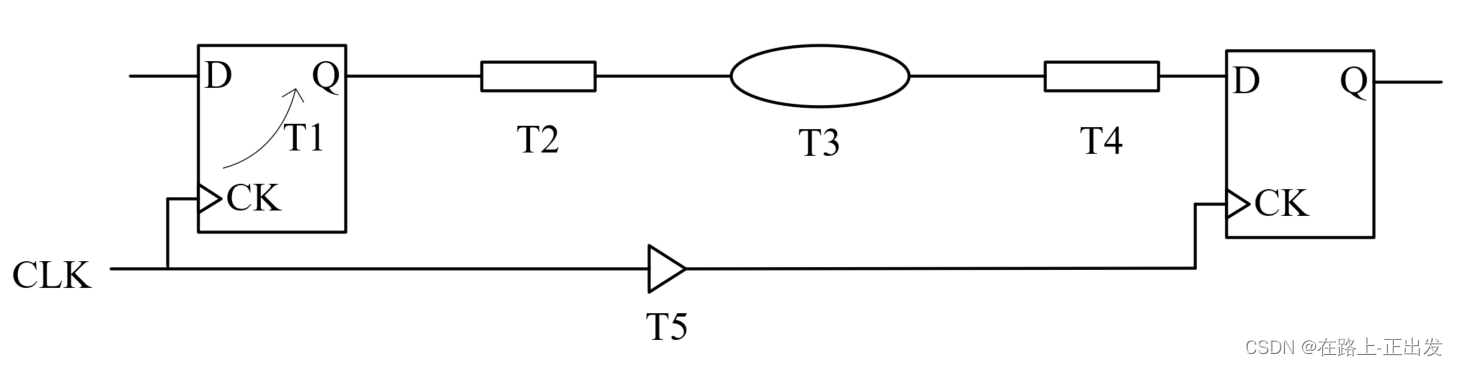

双D触发器典型电路

假设时钟周期为Tcycle,Tsetup,Thold分别为触发器建立保持时间,为保证时需满足要求,需要满足什么样的时序关系?(T1~T5分别为各部分延迟值)

这种双触发器的电路最为经典,前一个触发器发起数据,后一个触发器捕获数据。

电路中的时序路径:第一个触发器的CK端到其Q端,再经过3个组合延迟到达第二个触发器的D端。这是一条完整的时序路径。

对于建立时间而言,在捕获触发器有效边沿来临之前的Tsetup时间之前,其D端数据就应该保持稳定。即,T1+T2+T3+T4 <= Tcycle + T5 - Tsetup

对于保持时间而言,保持时间一般指的都是寄存器本身的时序关系,不涉及与其他寄存器的时序关系,触发器的D端数据在CK端时钟沿之后需要保持稳定的时间。以本图中的捕获触发器为例,需要满足:T1+T2+T3+T4+Tcycle >= Tcycle + T5 + Thold,即T1+T2+T3+T4 >= T5 + Thold

由此可见,相邻触发器之间的组合逻辑延迟越大对保持时间越向好,但是对建立时间越糟糕。二者是一对矛盾。

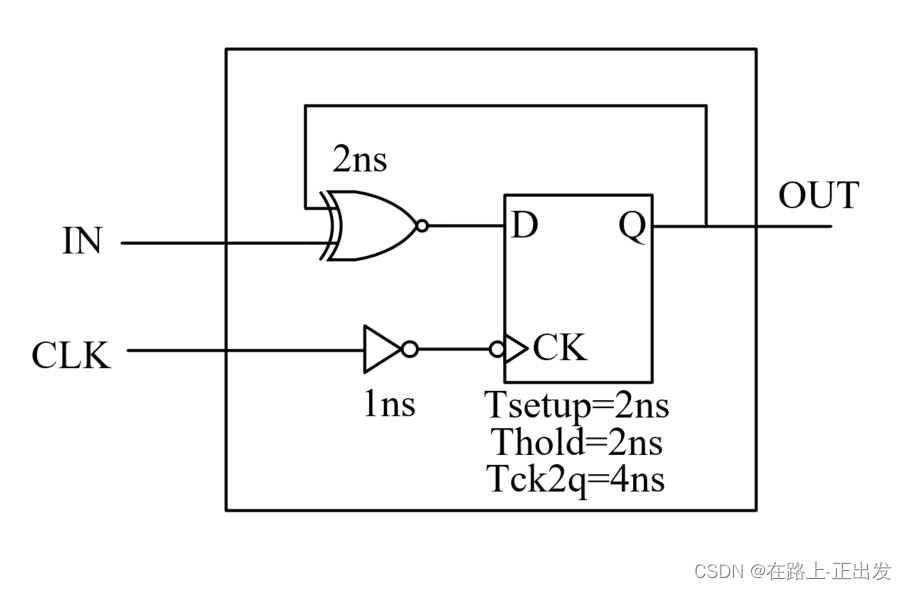

单触发器电路

将整个方框内部的电路视作一个寄存器,求其等效/有效的建立/保持时间?

这个题目理解起来是有点难度的,总的来说,就是根据方框内部触发器的建立保持时间要求反推整个电路的建立保持时间要求。

对于建立时间而言,对内部的D触发器,在CK端时钟有效边沿到来之前的2ns(Tsetup),D端的数据就应该保持稳定。在不考虑时钟延迟的情况下,由于输入数据路径存在2ns延迟,那么对于IN端口来说,就要在时钟有效边沿到来之前的2+2=4ns,IN端口的数据就要保持稳定。然后接着考虑时钟延迟的影响,由于时钟存在1ns延迟,所以在CLK端口时钟边沿到来前4-1=3ns,IN端口的数据保持稳定,就可以满足建立时间需求。所以整个电路块的有效/等效建立时间为:

Tvalid_setup = Tsetup + 2 - 1 = 3ns

对于保持时间而言,对于内部D触发器,在CK端时钟有效边沿之后2ns(Thold),D端的数据仍需要保持稳定。在不考虑时钟延迟的情况下,由于输入数据路径存在2ns延迟,那么对于IN端口来说,就要在时钟有效边沿到来之后的2-2=0ns,IN端口的数据要保持稳定。然后接着考虑时钟延迟的影响,由于时钟存在1ns延迟,所以在CLK端口时钟边沿到来后1ns,IN端口的数据要保持稳定,就可以满足保持时间需求。所以整个电路块的有效/等效保持时间为:

Tvalid_hold = Thold - 2 + 1 = 1ns

改电路块的最小时钟周期 = Tsetup + Tclk2q + 2ns = 8ns,最快的时钟频率 = 125MHz