FPGA设计实战演练.高级技巧篇-----读书笔记

第一章 从PCB开始研究FPGA设计问题

一、PCB布线

1、要求

·对所有器件进行电源滤波,均匀分配电源,降低系统噪声。

·匹配信号线,减小信号反射。

·降低并行走线之间的串扰。

·减小地反弹效应。

·进行阻抗匹配。

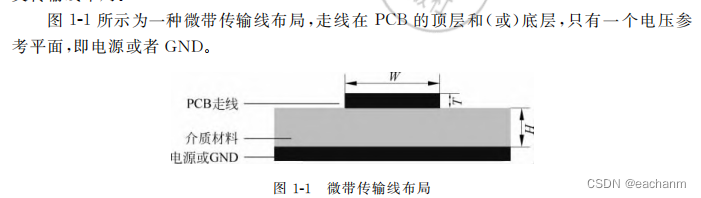

2、微带传输布局,走线在PCB的顶层或底层,只有一个参考平面

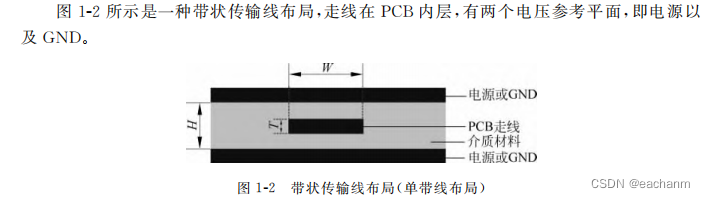

3、带状传输线布局,走线在PCB内层,有两个电压参考平面

4、阻抗控制原则:单端走线控制阻抗为50Ω;差分走线控制阻抗为100Ω。生产厂家阻抗控制的偏差范围一般为正负5%左右。

5、减小微带线或带状线布局串扰的方法是:

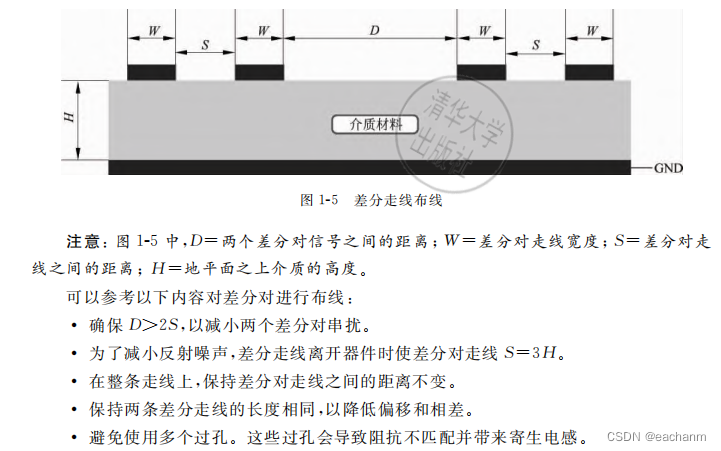

·在布线要求允许的范围内,尽可能地加宽信号线之间的距离。走线之间尽量不要靠

近,距离保持在介质高度的3倍以上。

·传输线设计要使导体尽可能靠近地平面。这一方法使得传输线能够与地平面紧耦

合,有助于和邻近信号去耦合。

·尽可能使用差分布线方法,特别是关键网络(例如匹配长度以及每条走线串通回

转等)。

·如果存在明显的耦合,应在不同层之间布设互相垂直的单端信号。

·减小单端信号之间并行走线的长度,以较短的并行走线布线,以减小网络之间的长

耦合走线。

6、差分走线

二、FPGA供电

1、单调性(或线性)要求,是指在上电过程中,电源轨是单调爬升而不会掉头往下掉(也称

单调非负特性)。也就是说,电源必须始终具有正斜率(或零斜率)。

2、给电源供电设计加入电压上电顺序和电源跟踪。这来源于FPGA的I/O电压必需要在核心电压上电以后才能上电的基本规律。

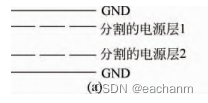

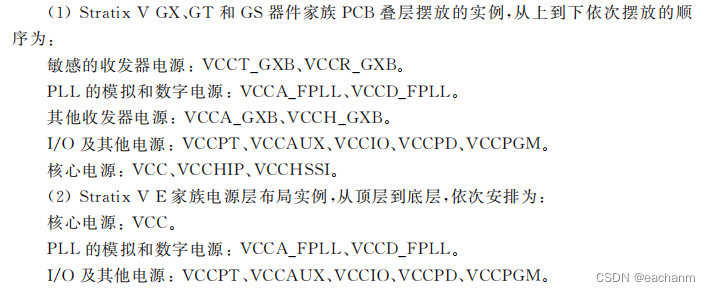

3、电源和地叠层分布

三、退耦电容

1、退耦电容可以在电源轨波动时为其提供少量的瞬态能量。

2、为何需要退耦电容?

可以将一个退耦电容看做是一组电阻(R)、电感(L)和电容(C)的串联组合,根据真实的RLC模型可知,电容也将在某个频率点上容抗和感抗分量彼此有效抵消。所以说,一个真实的电容将会在某个频点时阻抗最小,这个阻抗最小的点被称为电容的谐振频率,在这个点上退耦电容可以提供最佳的滤除供电干扰的能力。