【Verilog】——赋值语句、结构语句、块语句

在文理百科知识的世界里,Verilog的赋值语句像是一场双人舞,阻塞和非阻塞赋值就像是舞伴,各有各的舞步和场合。想让电路综合时不出错,就得明白啥时候该用谁。比如,时序逻辑就像是跳华尔兹,非阻塞赋值才是它的最佳拍档,因为它不会阻塞后续的动作,让整个舞蹈流畅起来。而组合逻辑更像是街舞,需要立刻完成一系列动作,这时候阻塞赋值就像是一位果断的领舞者,一步一个脚印,不容拖延。

那么,问题来了:为啥不能随便混用呢?举个例子,假设你用阻塞赋值处理时序逻辑,就像让华尔兹跳得像街舞一样生硬,这会让综合器一头雾水,搞不明白你的意图,最后可能跳出个四不像的电路,害人又害己。

再想想,如果在组合逻辑里用了非阻塞赋值,就像让街舞跳得像华尔兹一样拖沓,整个逻辑会变得混乱,甚至死锁。这可不是你想要的场景吧?

所以,记住这个口诀:时序用非阻,组合用阻塞,电路才能顺畅无阻!

目录

1.常用语句

2.块语句

1.顺序块

2.并行块

3.结构语句

1.always

2.initial

4.赋值语句

1.非阻塞赋值

2.阻塞赋值

3.非阻塞赋值和阻塞赋值的区别

4.深入理解阻塞赋值和非阻塞赋值

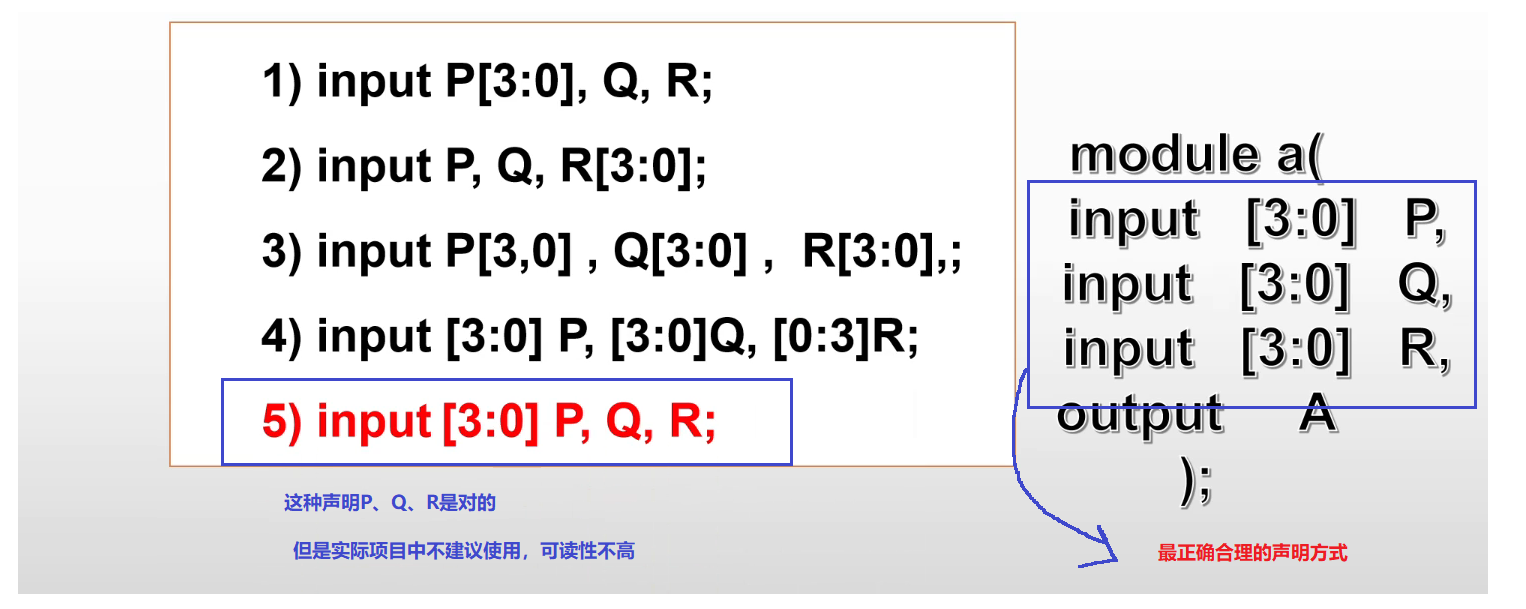

声明信号的时候统一大数在高位,小数在低位

比如:reg [3:0 ] ain这是是最规范的

reg [0:3 ] ain reg [4:2 ] ain 这些都是不规范的

1.常用语句

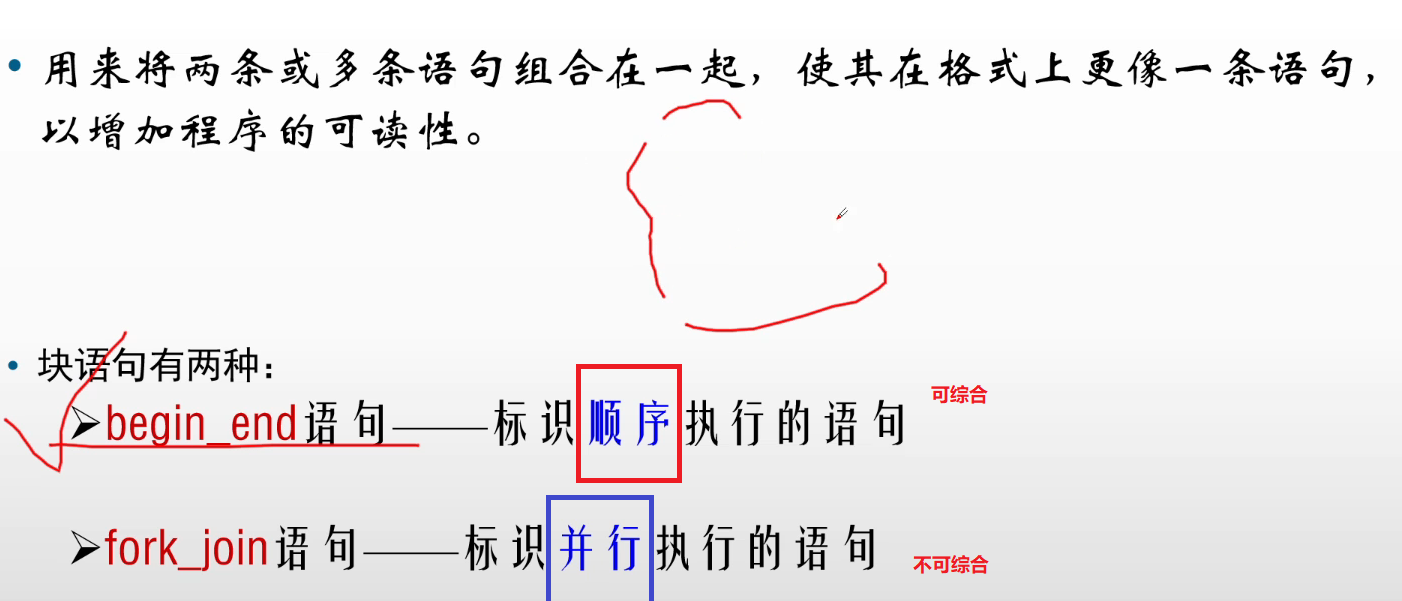

2.块语句

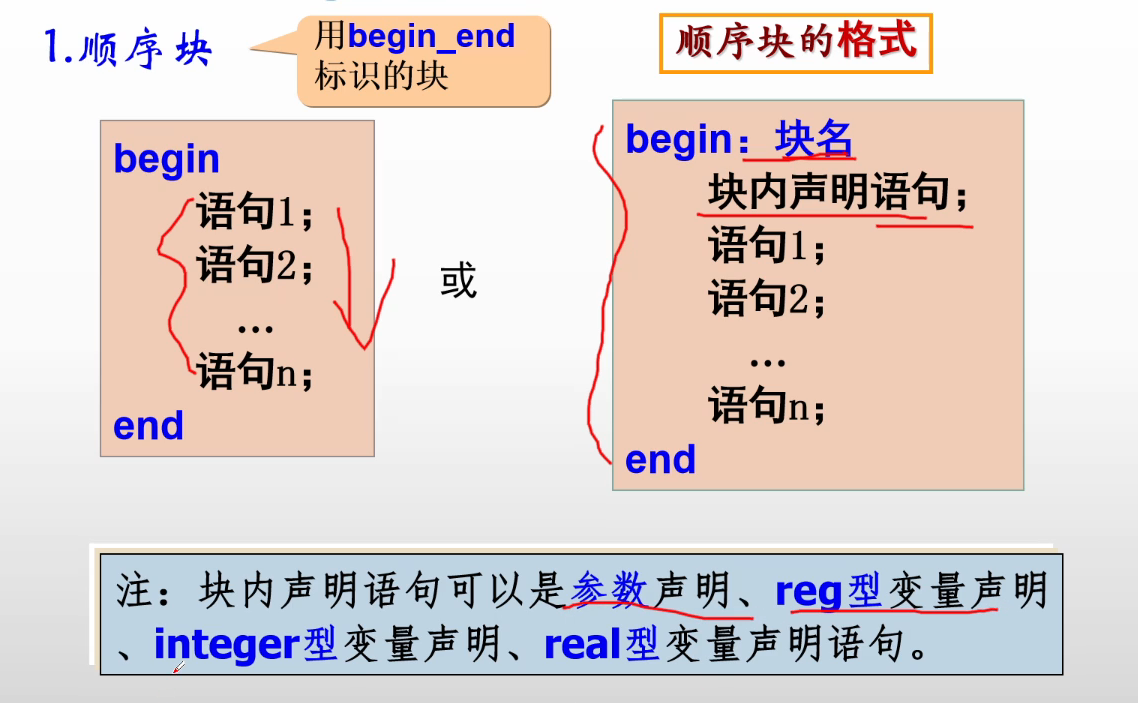

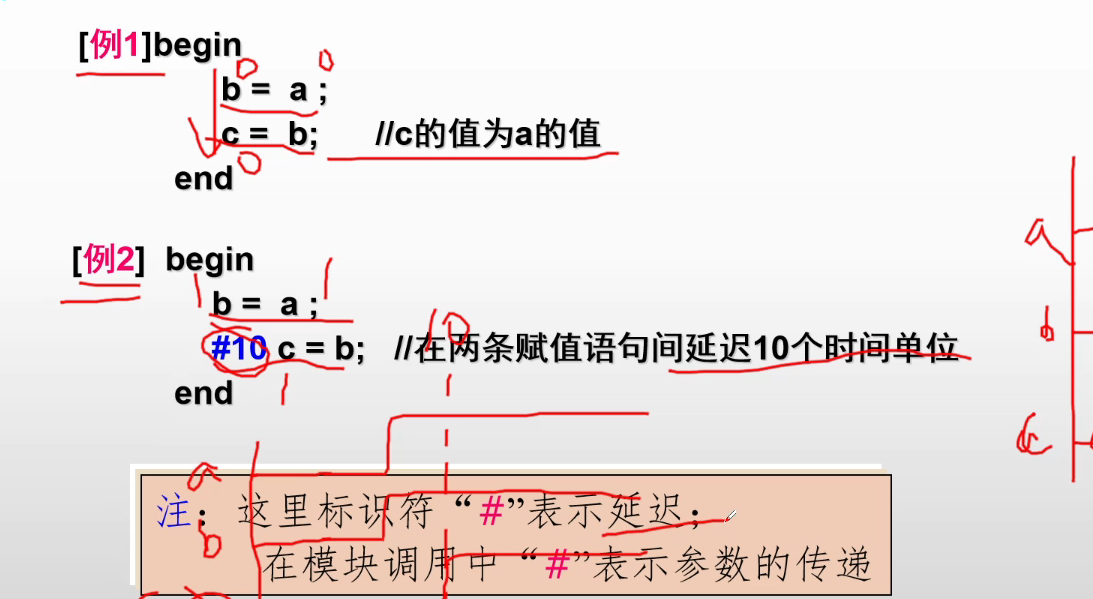

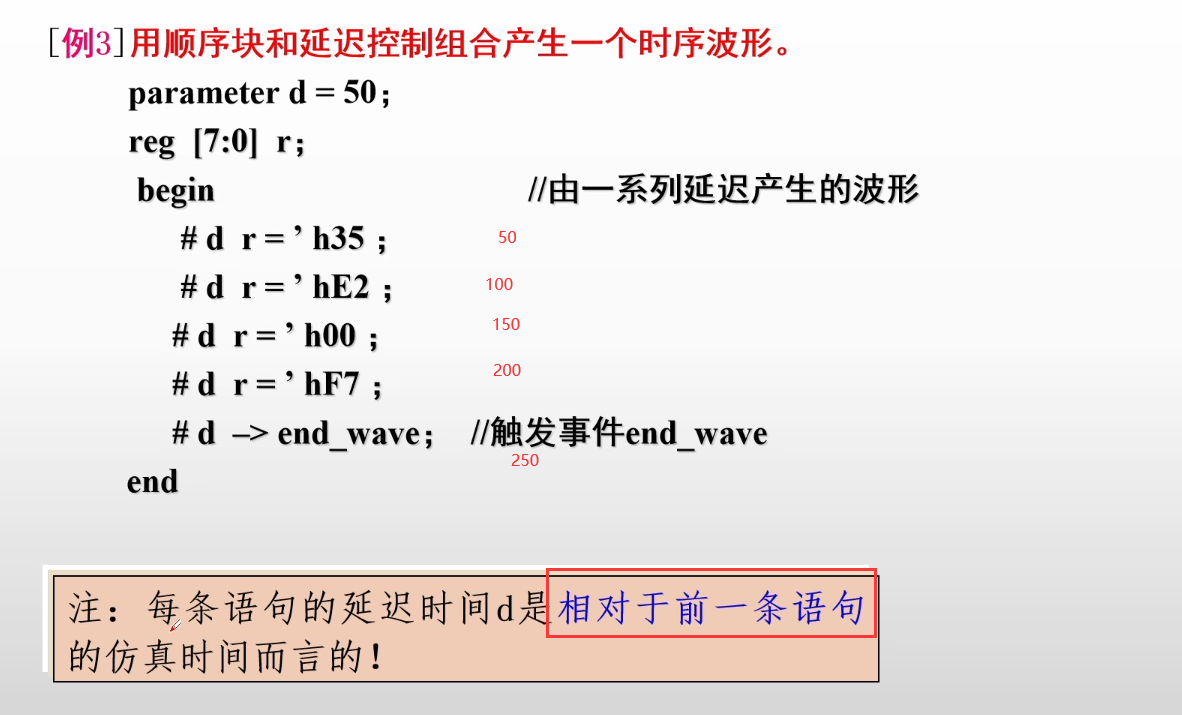

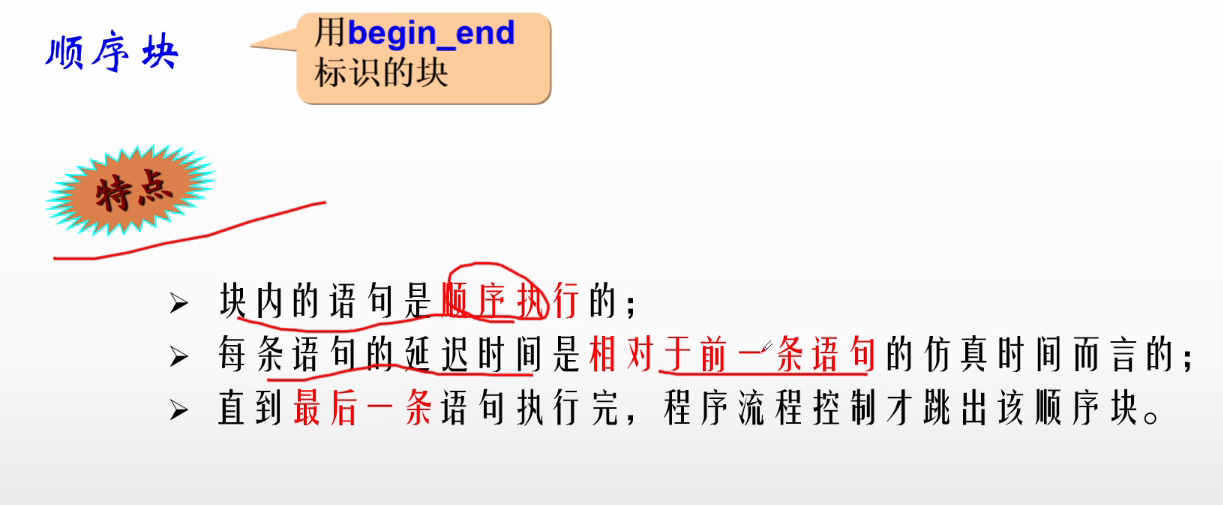

1.顺序块

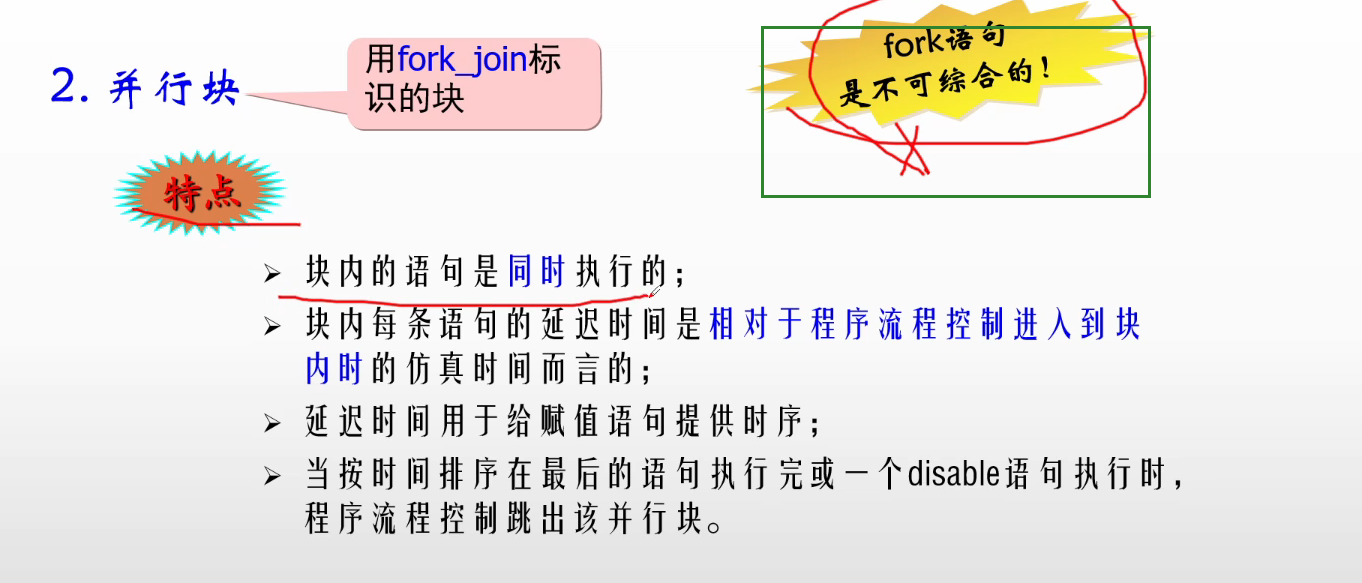

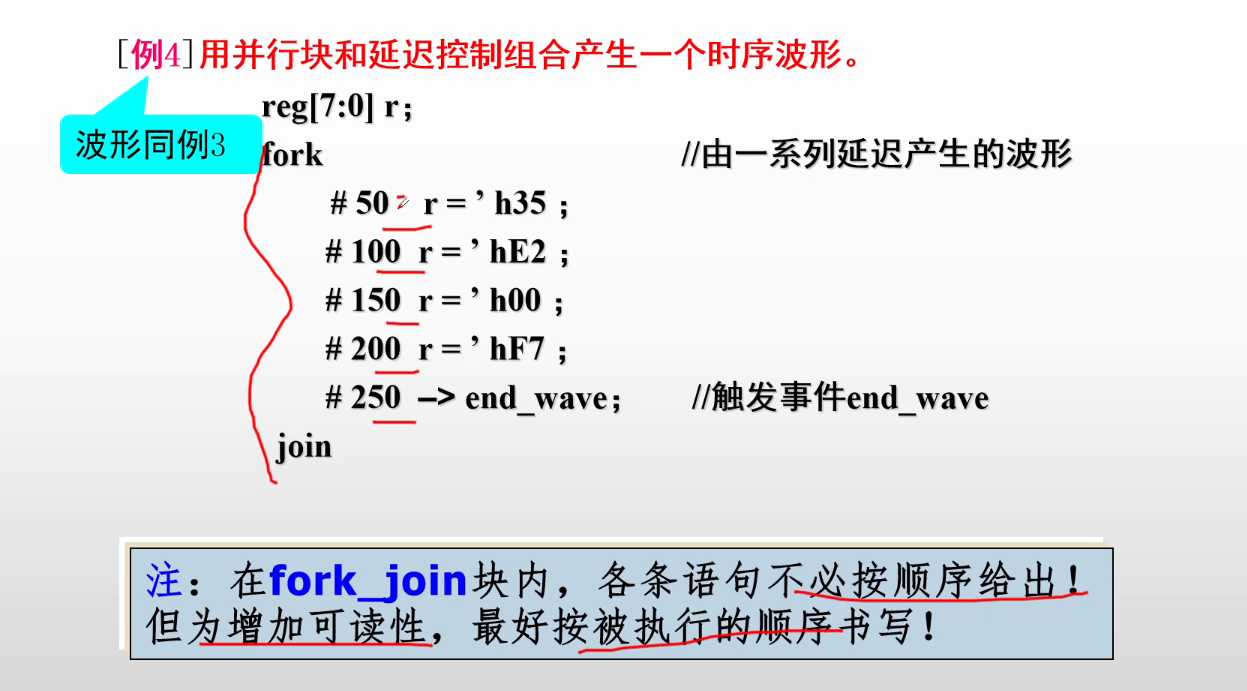

2.并行块

3.结构语句

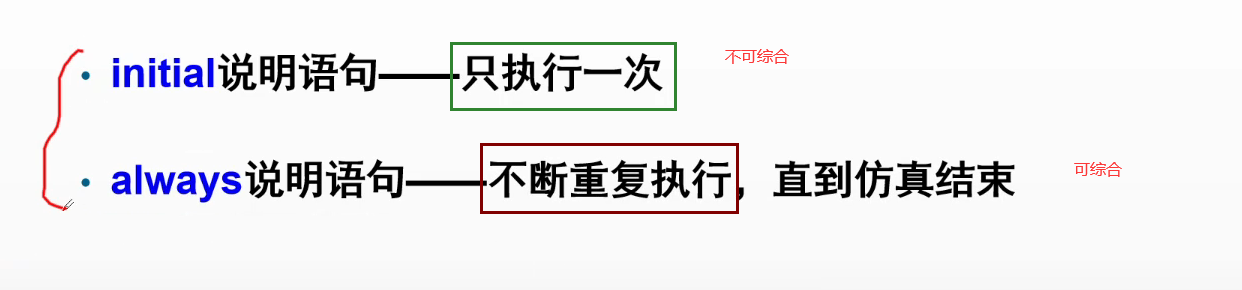

3.结构语句

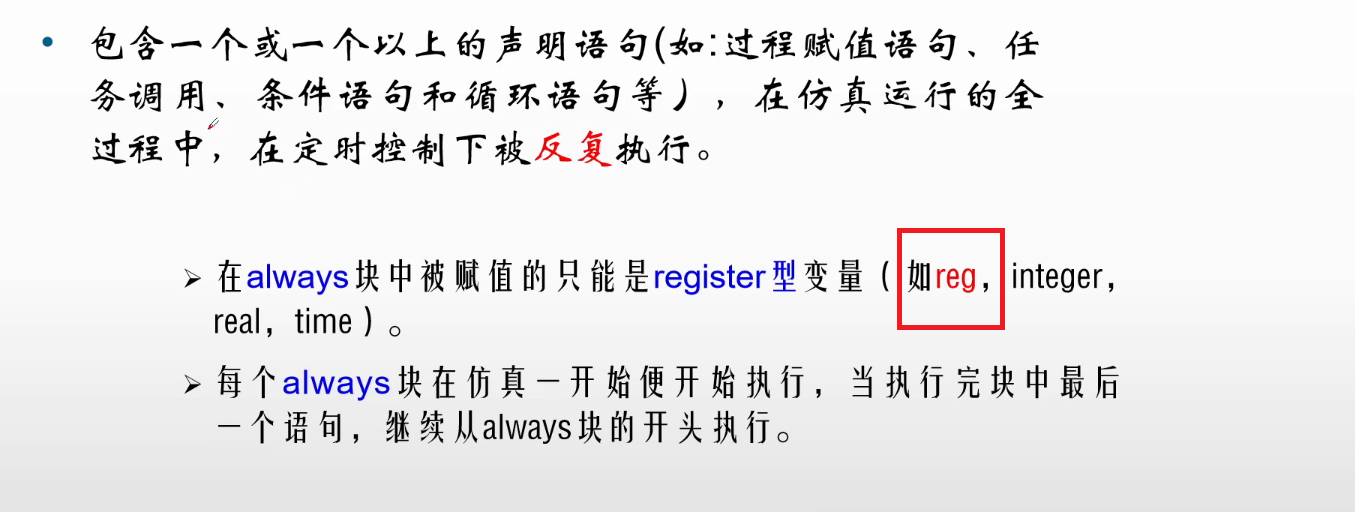

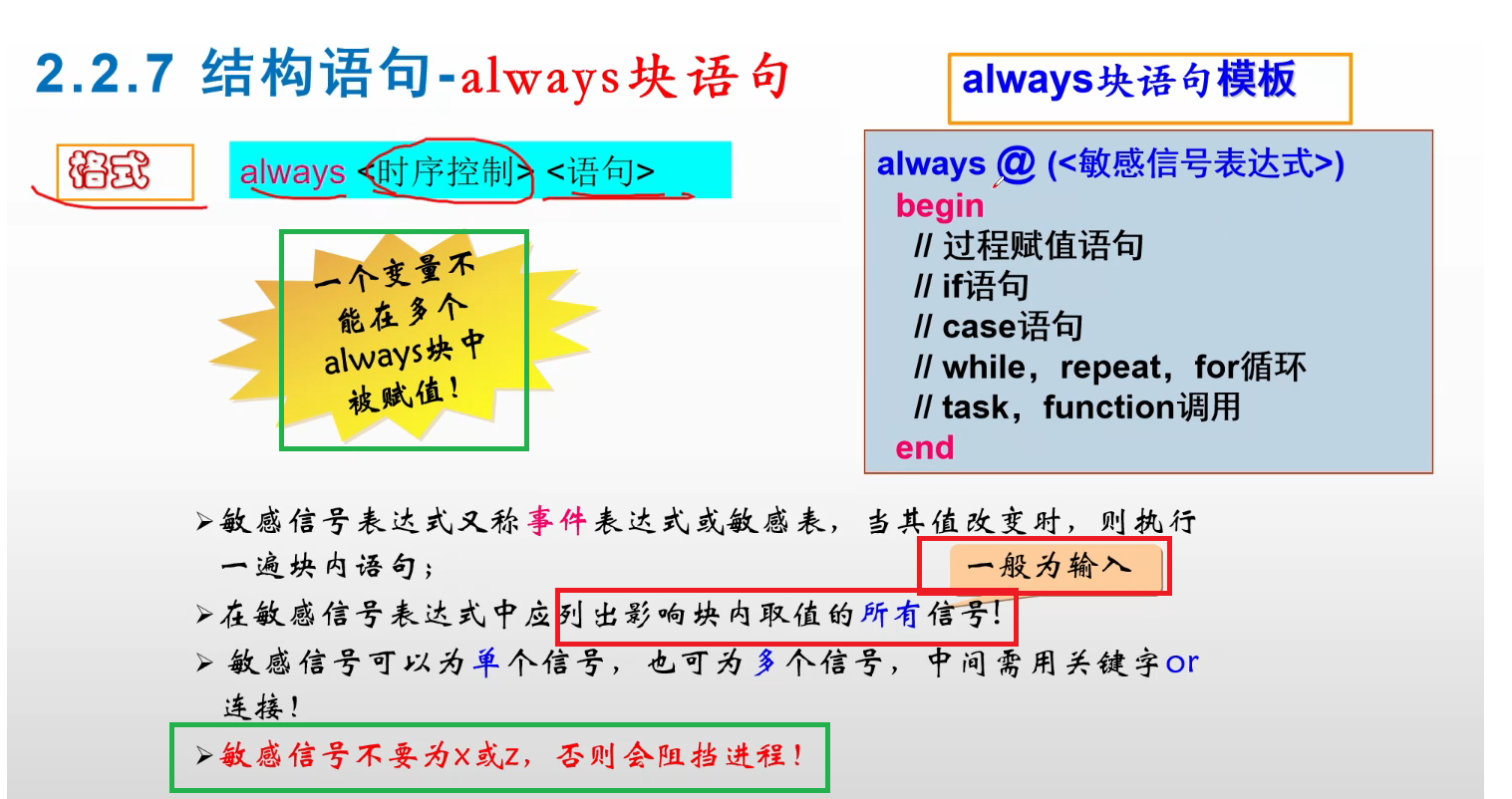

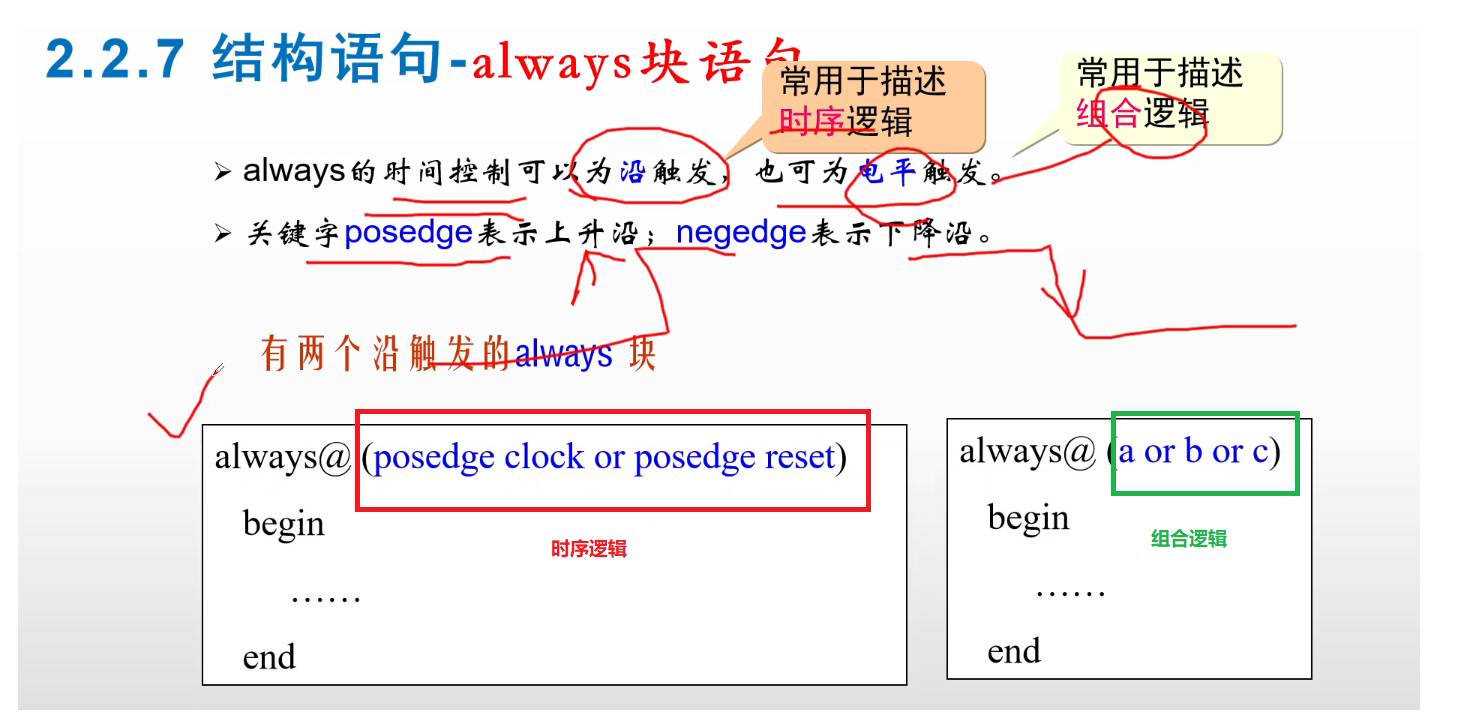

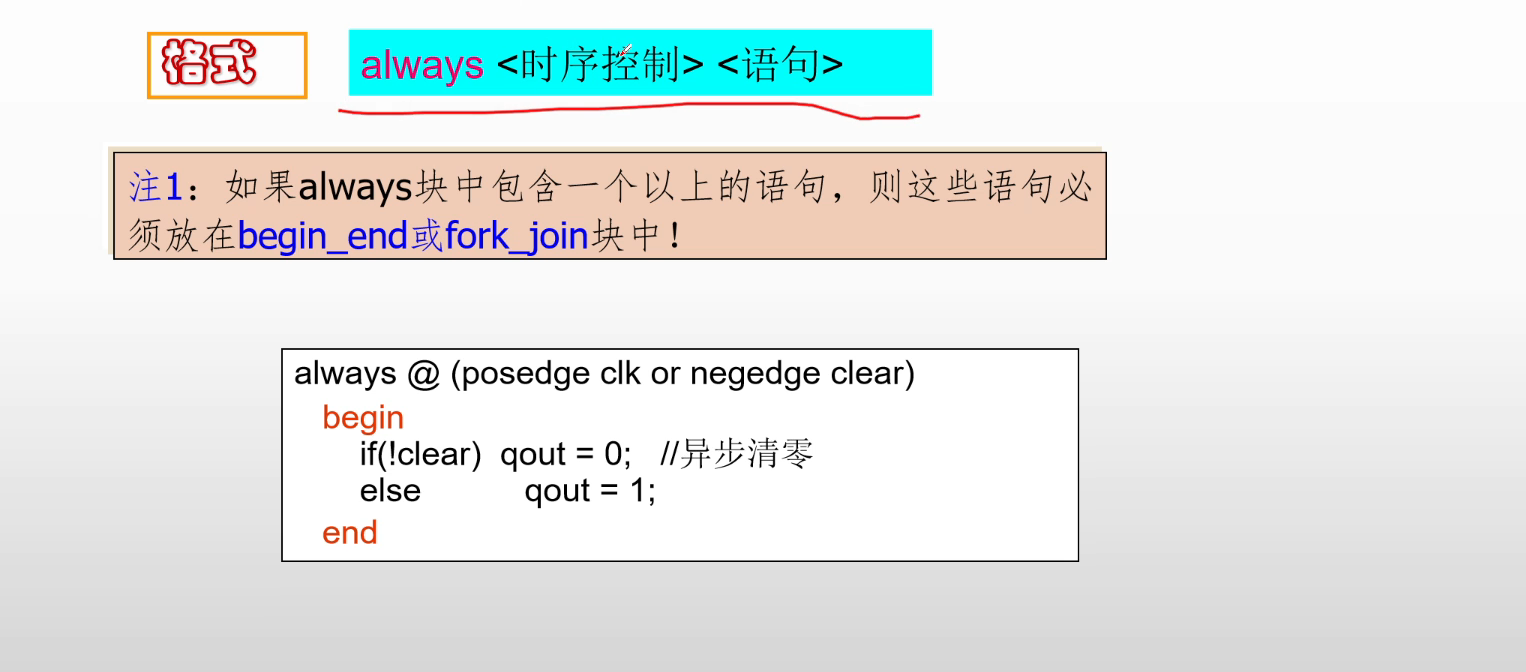

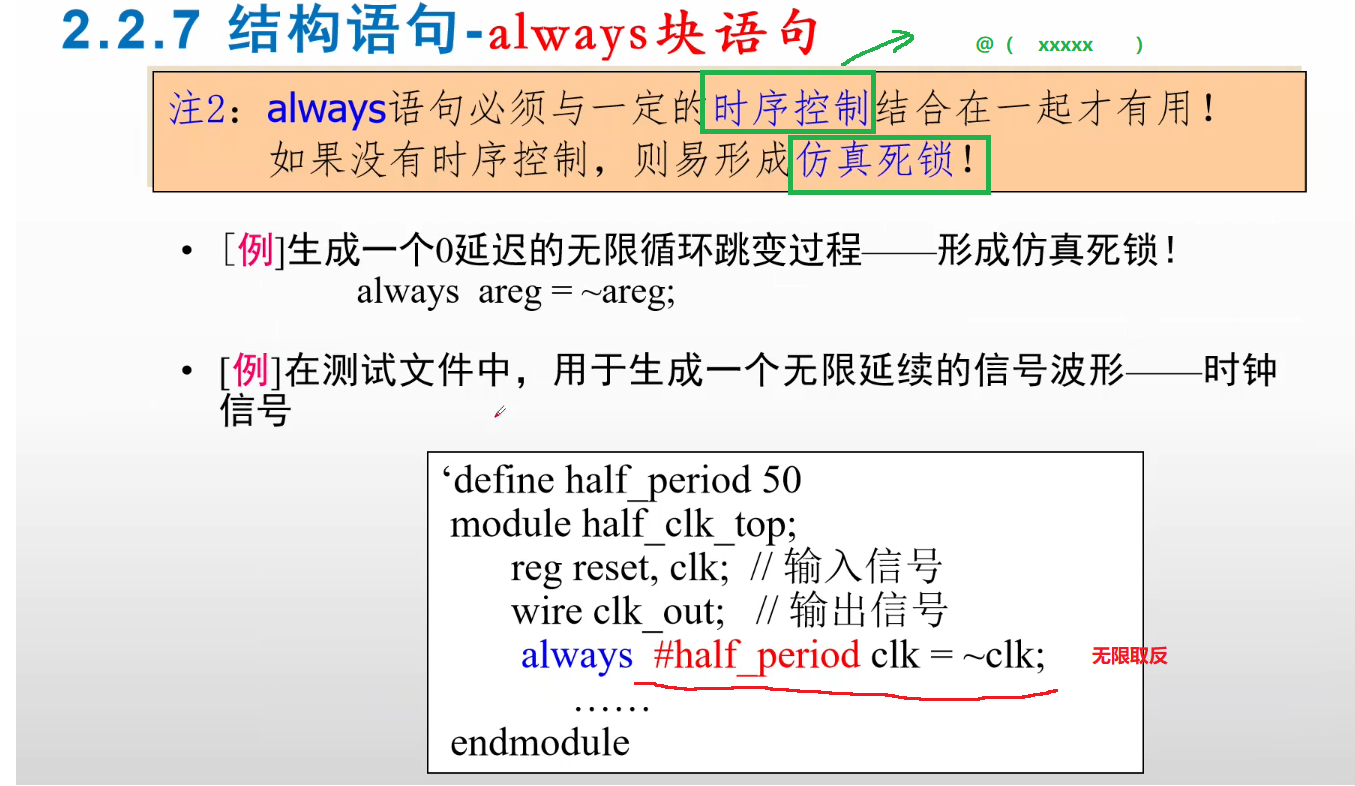

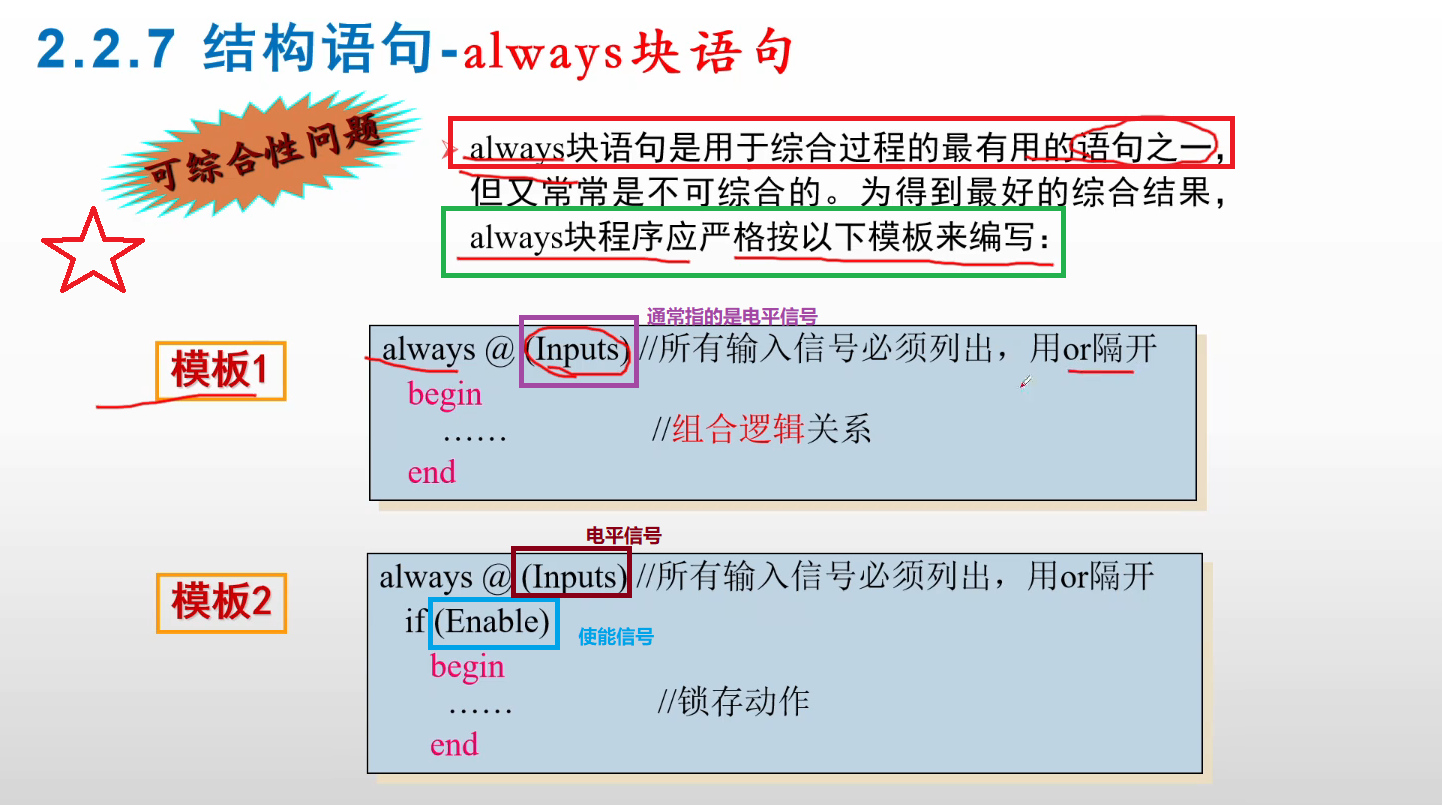

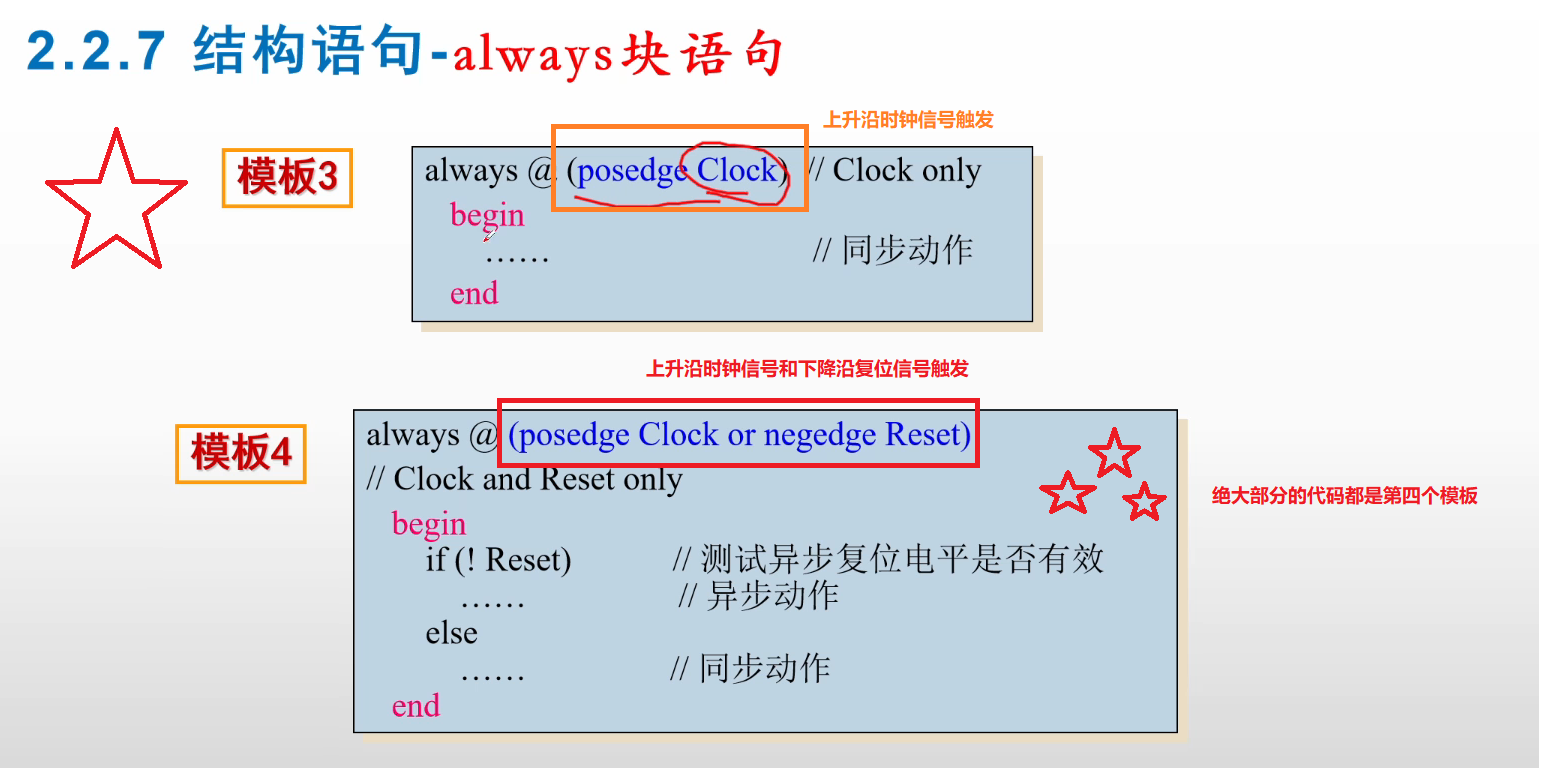

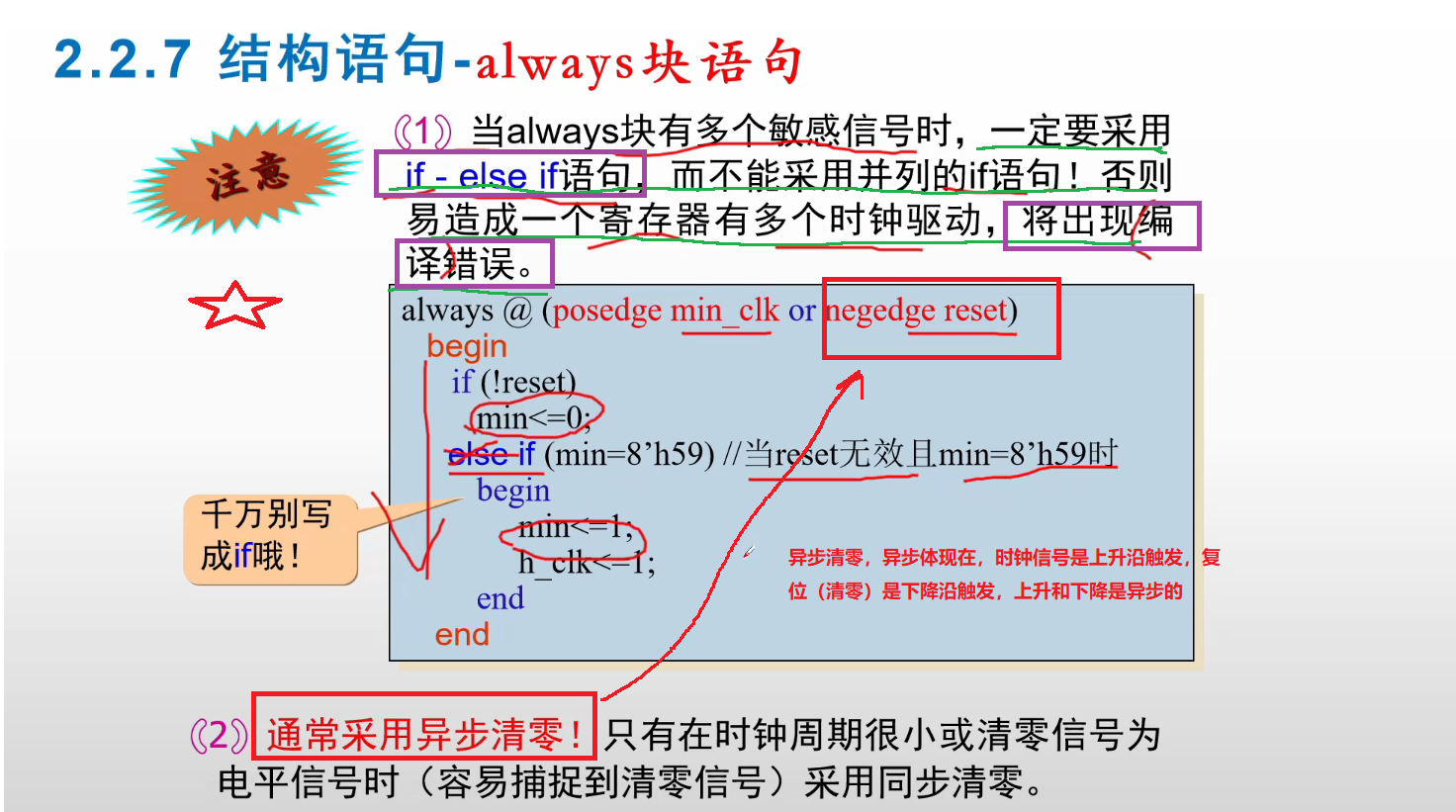

1.always

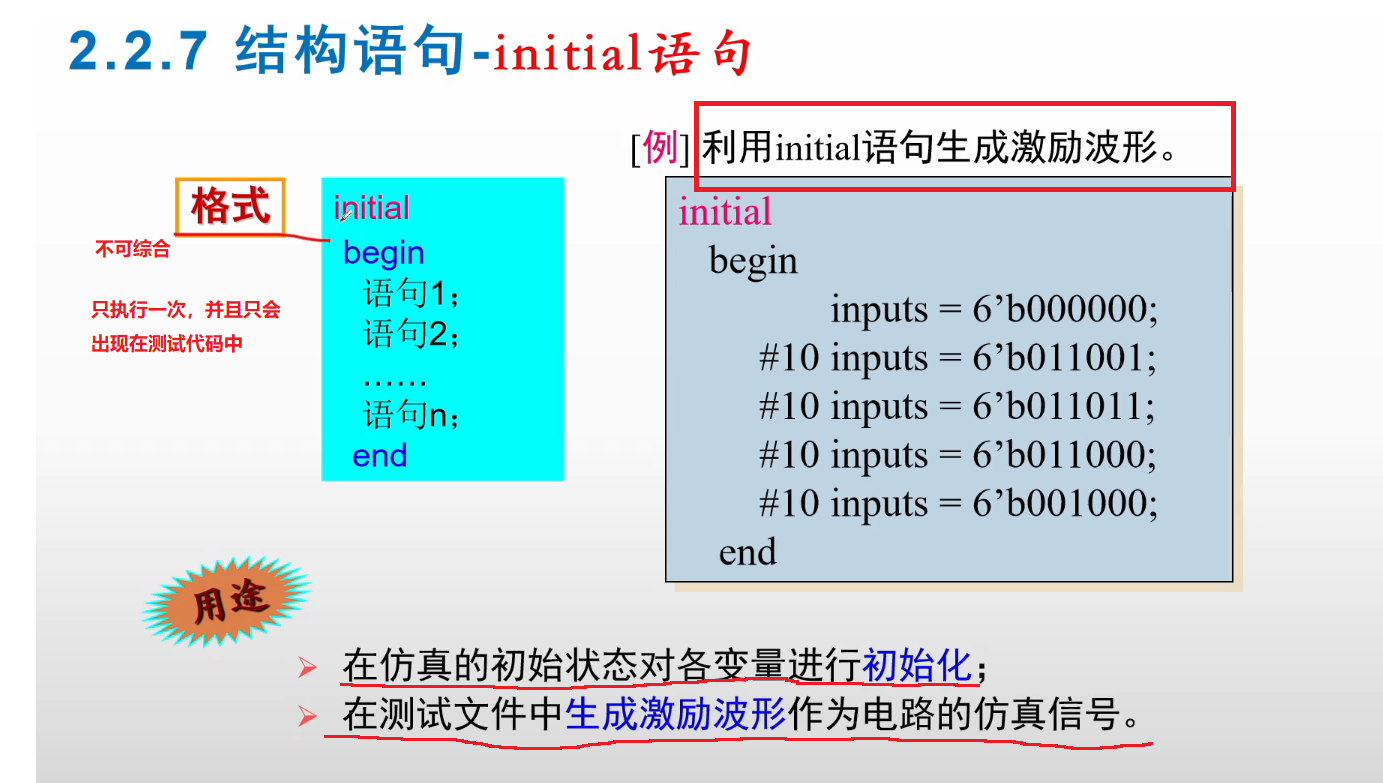

2.initial

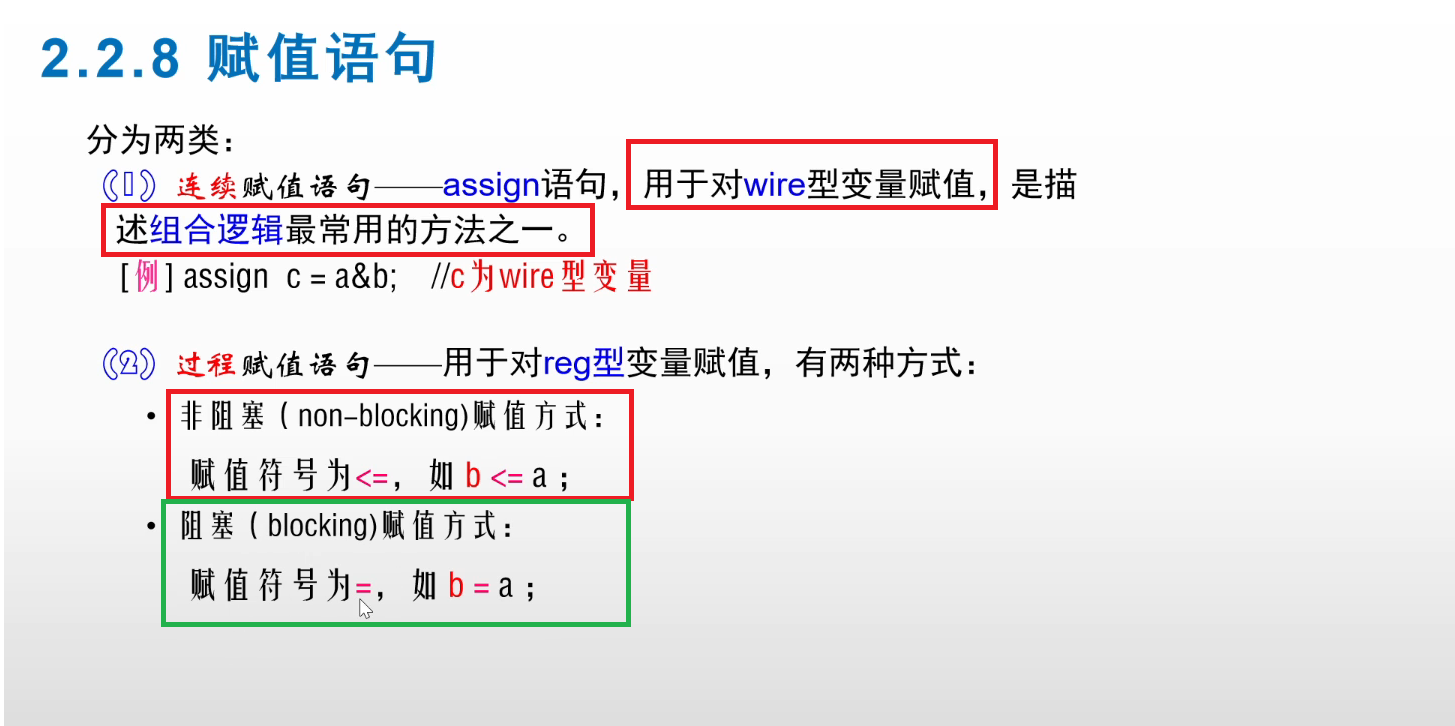

4.赋值语句

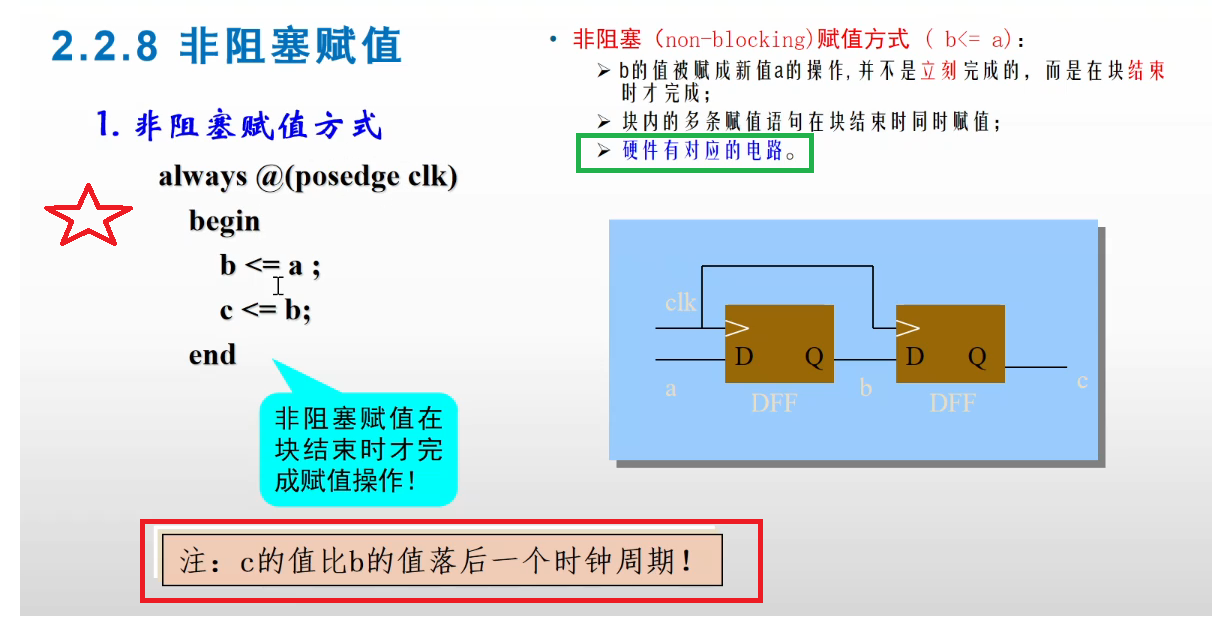

1.非阻塞赋值

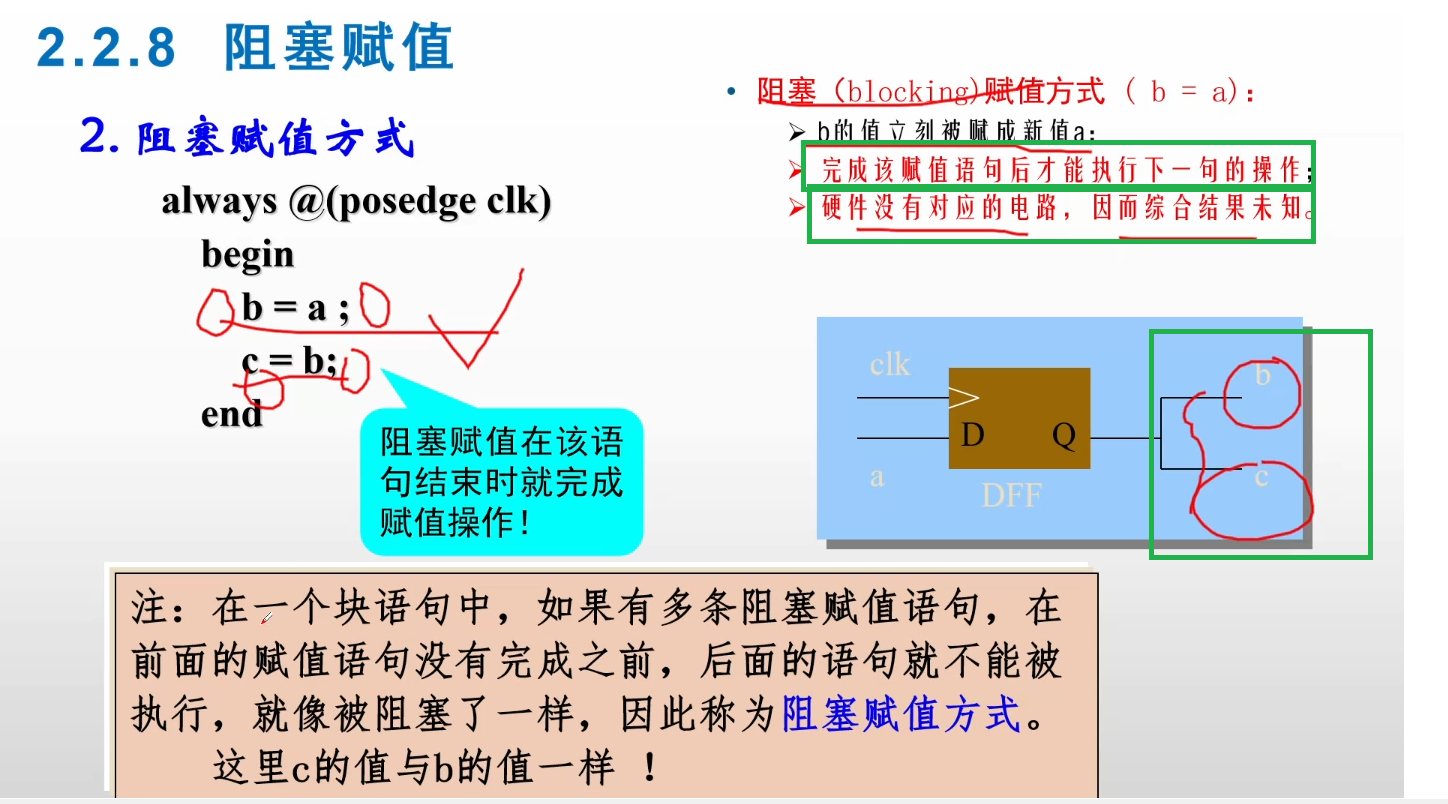

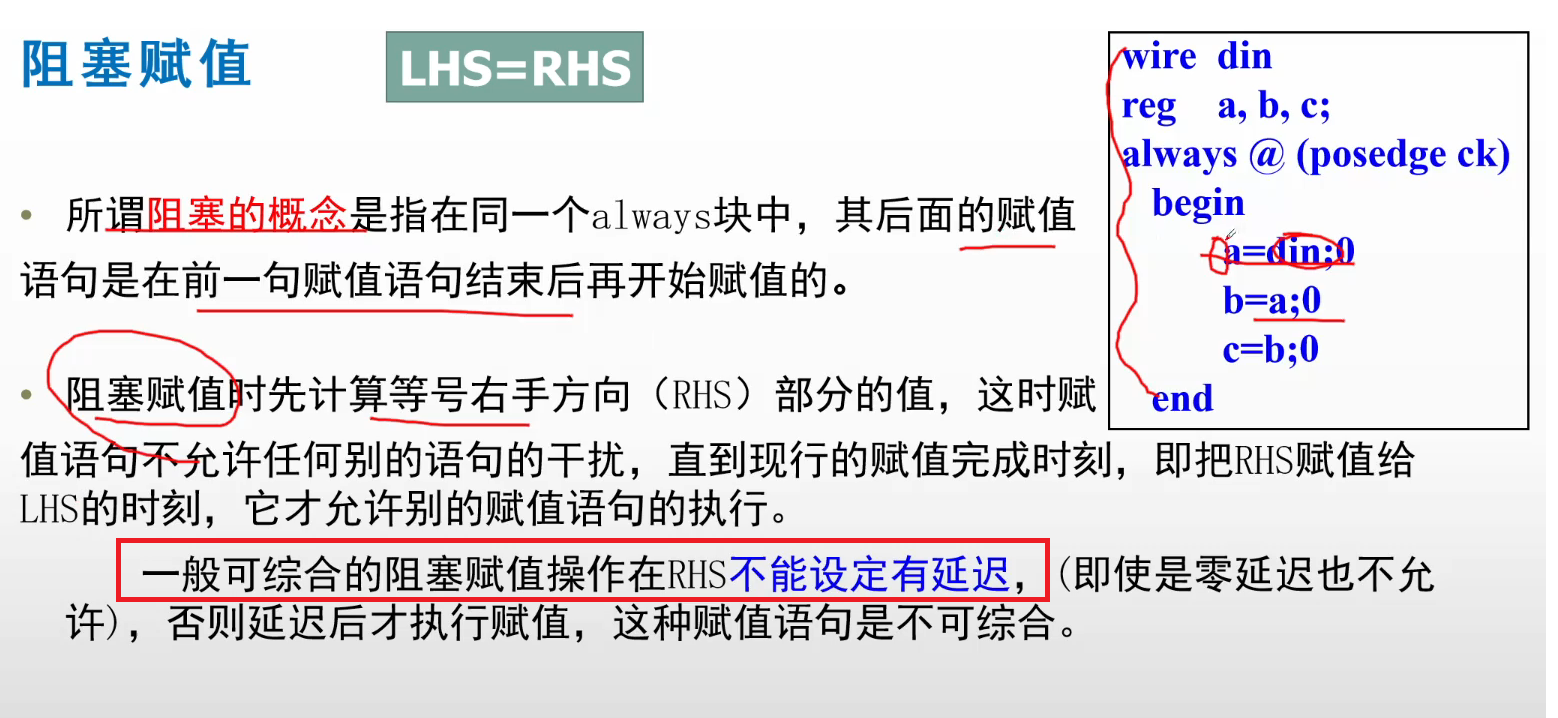

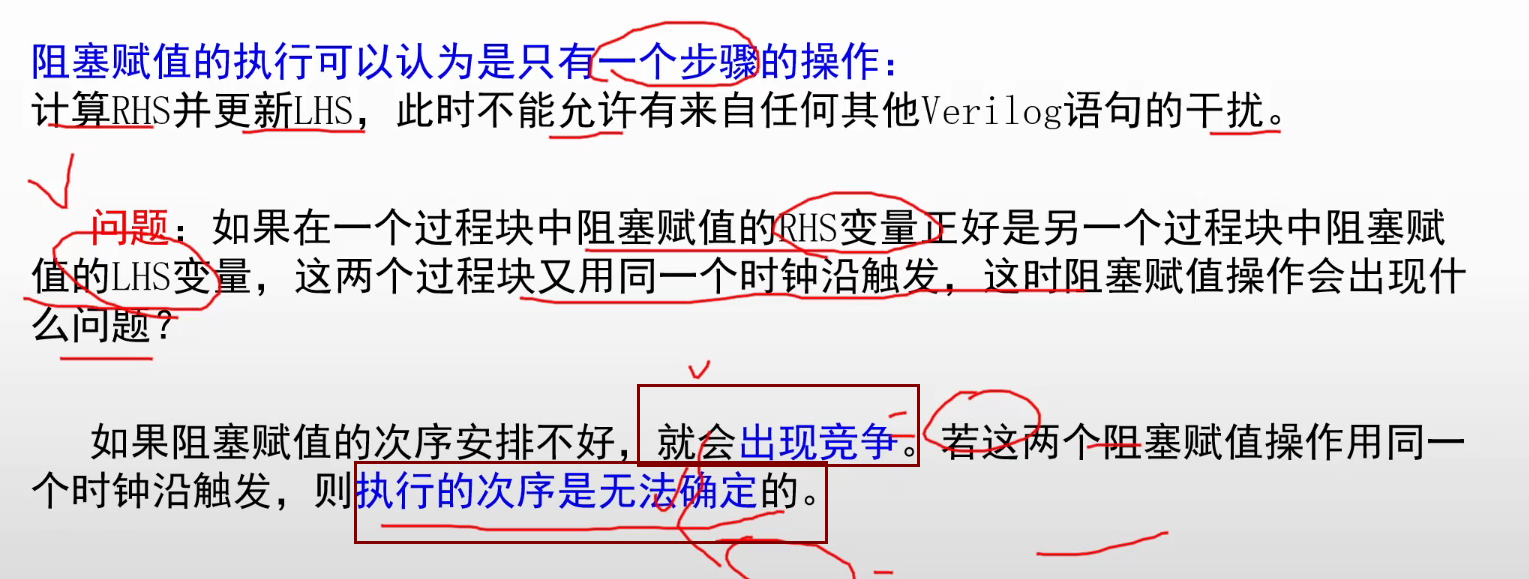

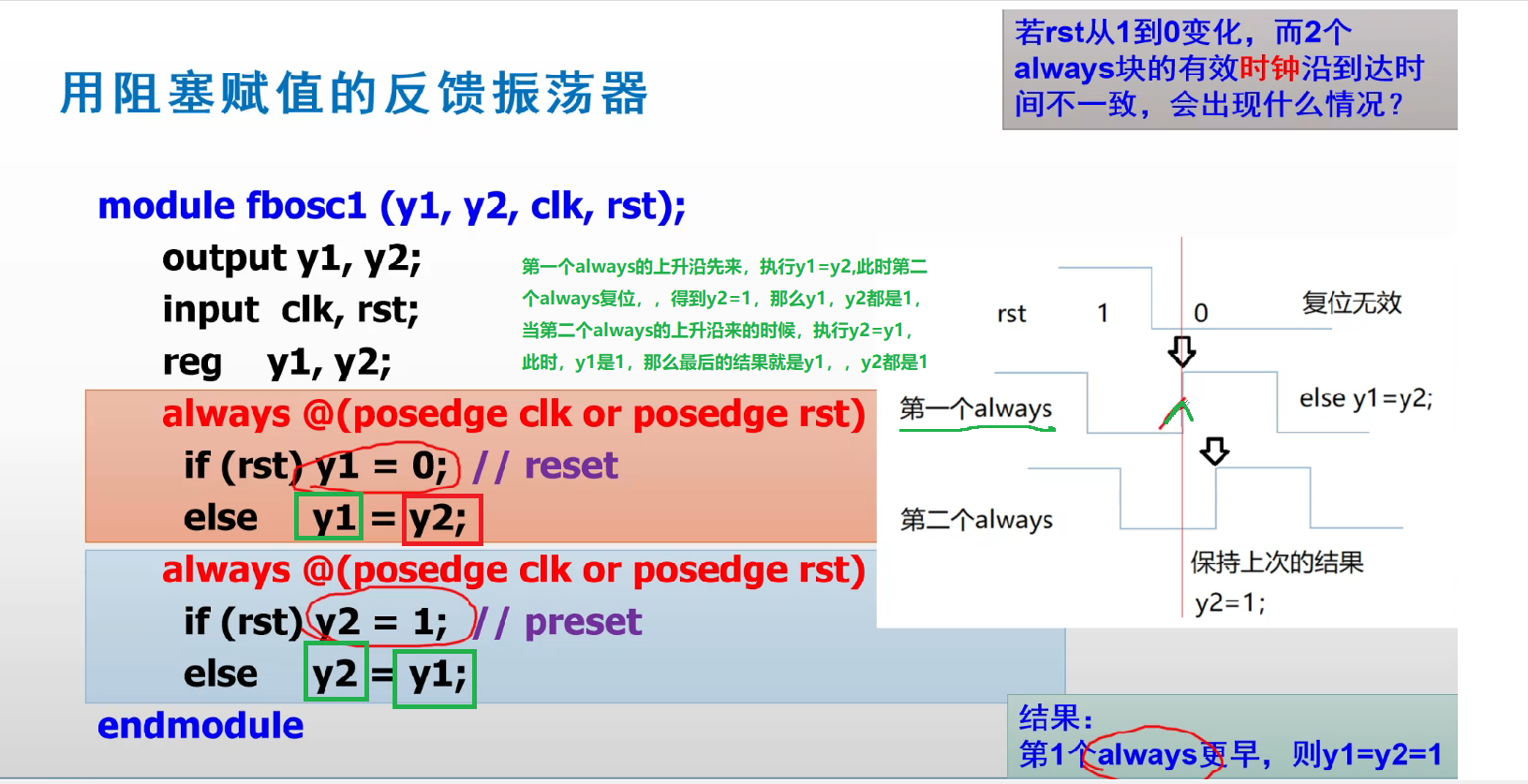

2.阻塞赋值

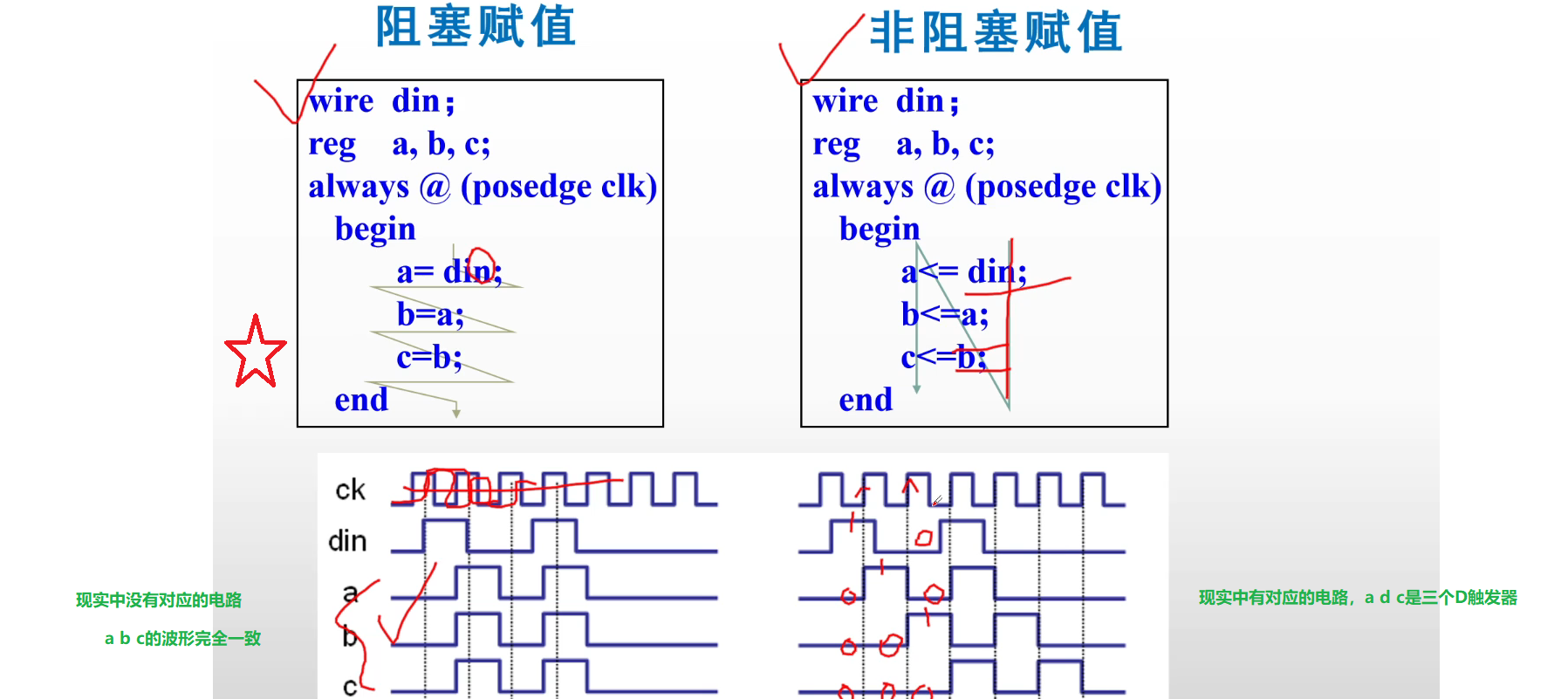

3.非阻塞赋值和阻塞赋值的区别

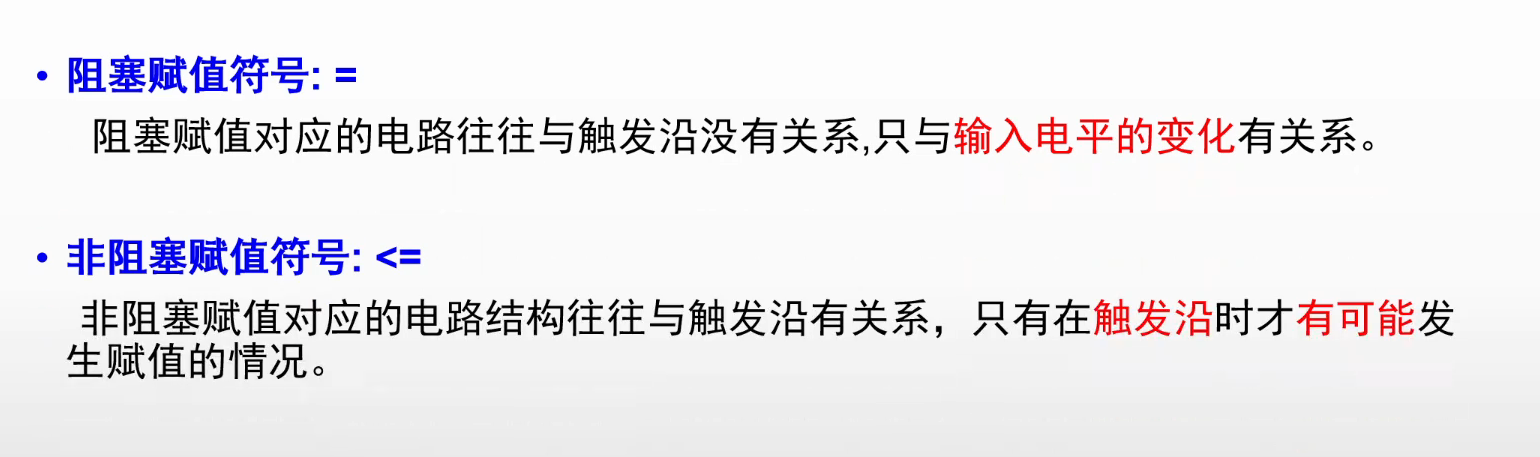

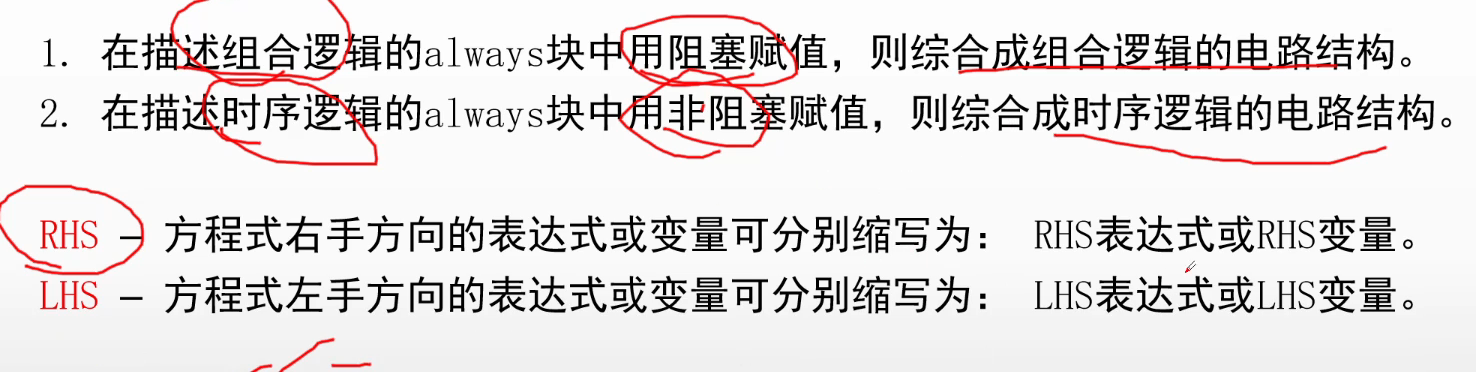

如果是时序逻辑的话,必须用非阻塞赋值

如果是组合逻辑的话,必须用阻塞赋值

这样才能综合

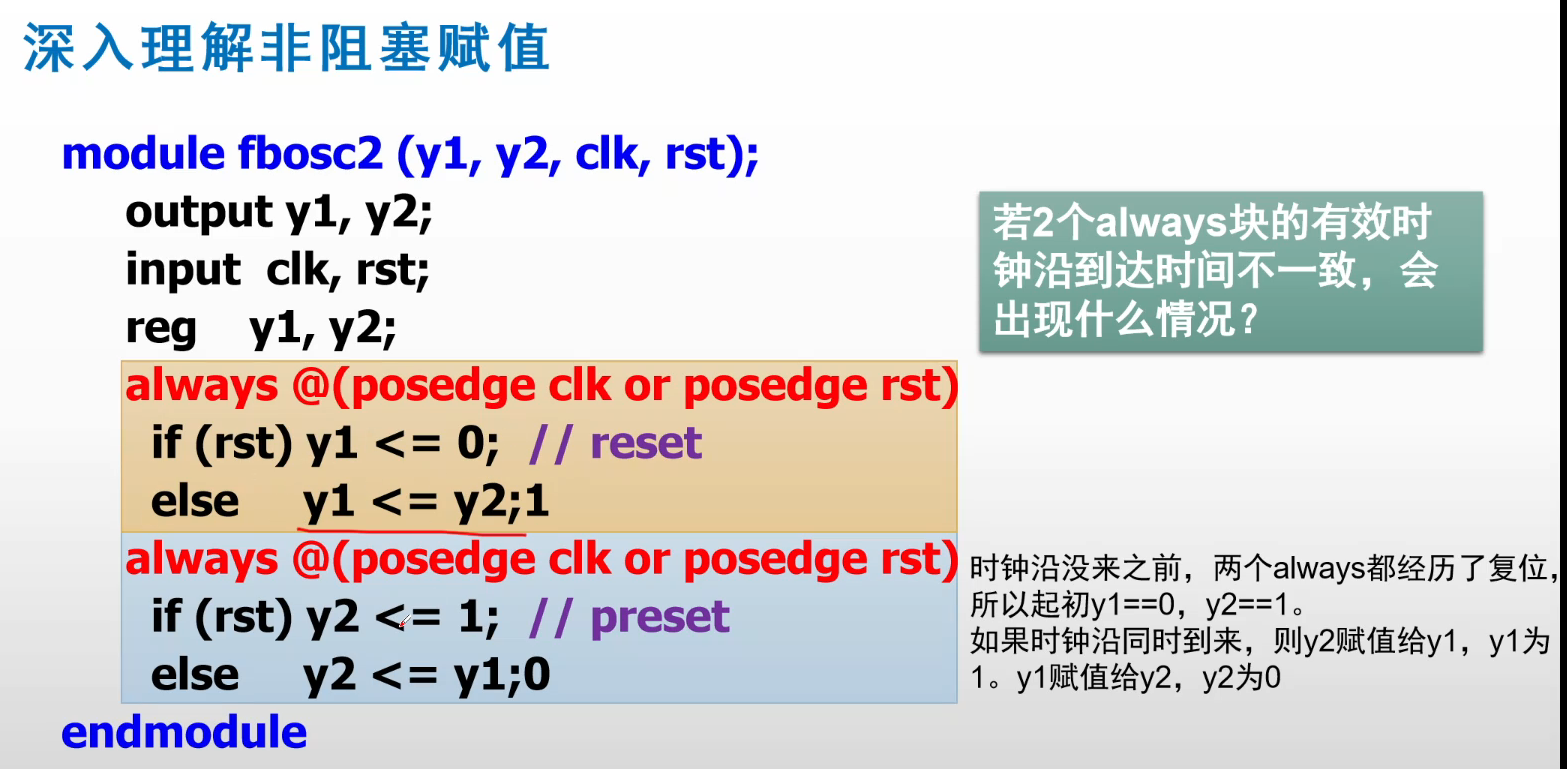

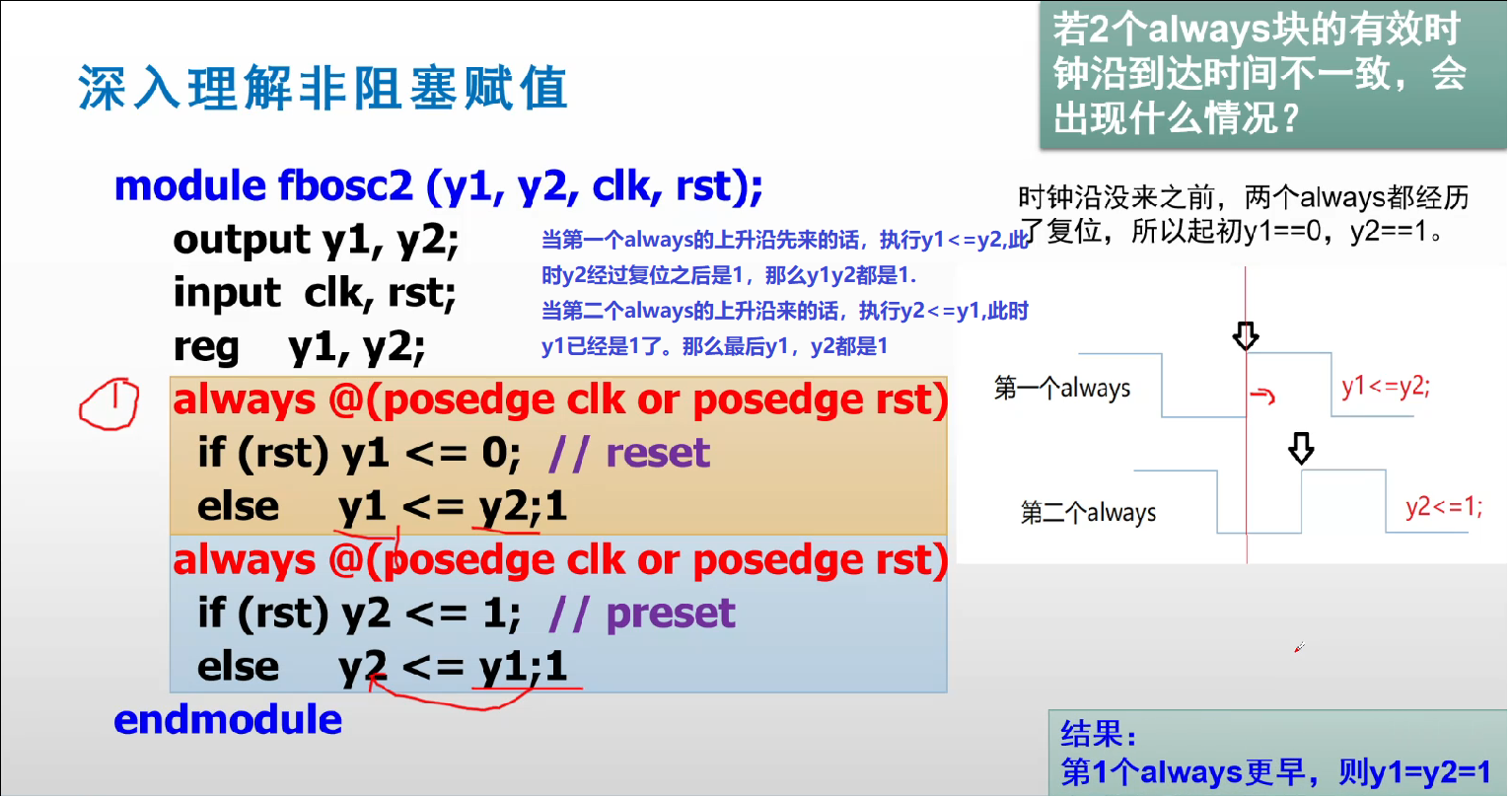

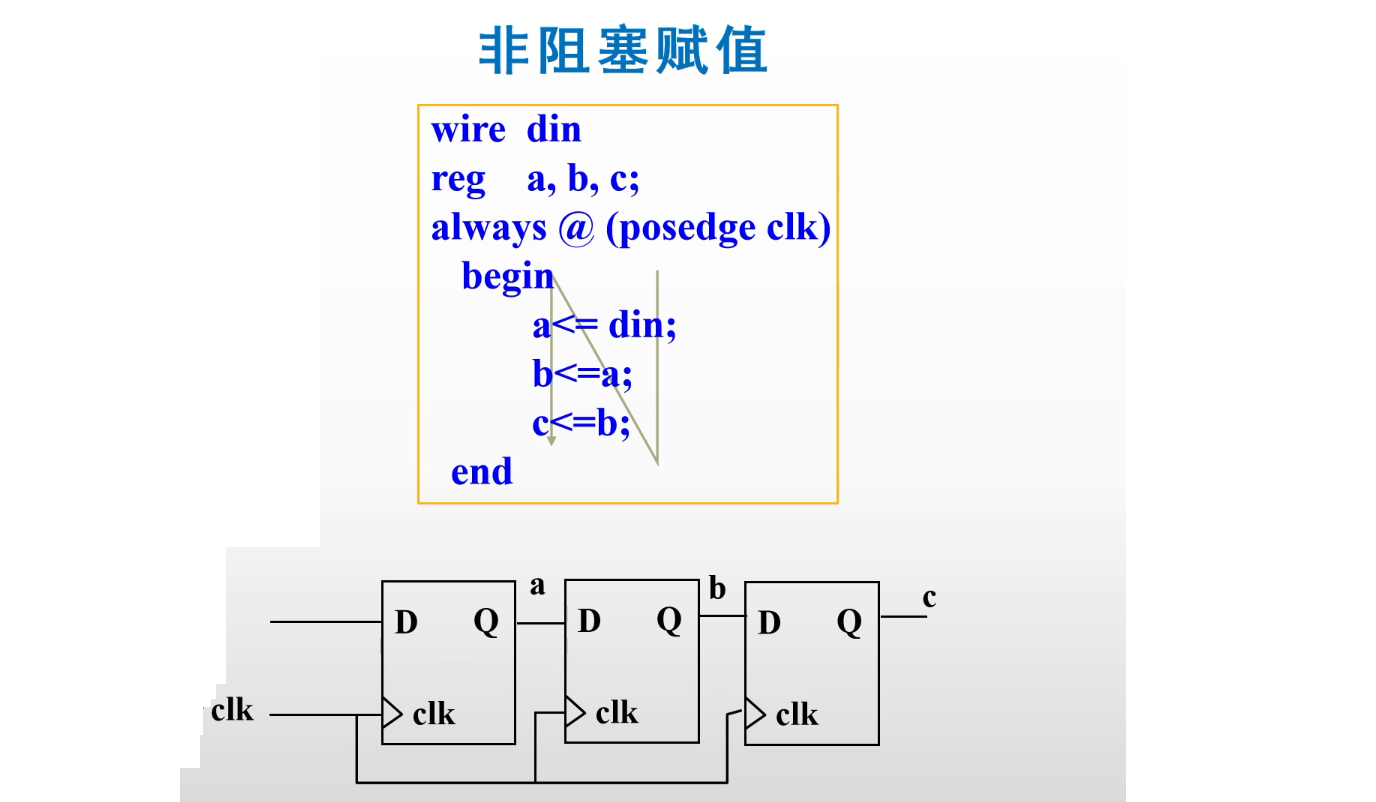

4.深入理解阻塞赋值和非阻塞赋值

PS:

组合逻辑用阻塞赋值!!!!!

时序逻辑用非阻塞赋值!!!!

这样的电路才能够综合!!!!