MIPI 打怪升级之DBI篇

目录

-

- 1 Overview

- 2 Display Architectures

-

- 2.1 Type 1 Display Architecture Block Diagram

- 2.2 Type 2 Display Architecture Block Diagram

- 2.3 Type 3 Display Architecture Block Diagram

- 2.4 Type 4 Display Architecture Block Diagram

- 3 Interface Signal Description

-

- 3.1 Type A Interface Block Diagram

- 3.2 Type B Interface Block Diagram

- 3.3 Type C Interface Block Diagram

- 3.4 Power Supply Signals

- 4 Interface Functional

-

- 4.1 Type A Interface Write and Read Cycles

-

- 4.1.1 Type A Interface - Example Fixed E Mode RW Sequence

- 4.1.2 Type A Interface - Example Clocked E Mode RW Sequence

- 4.2 Type B Interface Write and Read Cycles

-

- 4.2.1 Type B Interface Example RW Sequence

- 4.3 Type C Interface Write and Read Cycles

-

- 4.3.1 Type C Interface RW Sequence - Option 1

- 4.3.2 Type C Interface RW Sequence - Option 2

- 4.3.3 Type C Interface RW Sequence - Option 3

- 4.4 Note

- 5 Tearing Effect

- 6 ColorCoding

-

- 6.1 3-bit Interface

-

- 6.1.1 3-bits/pixel (R 1-bit, G 1-bit, B 1-bit), Eight Colors - Option1

- 6.1.2 3-bits/pixel (R 1-bit, G 1-bit, B 1-bit), Eight Colors - Option2

- 6.2 8-bit Interface

-

- 6.2.1 8-bits/pixel (R 3-bit, G 3-bit, B 2-bit), 256 Colors

- 6.2.2 12-bits/pixel (R 4-bit, G 4-bit, B 4-bit), 4,096 Colors

- 6.2.3 16-bits/pixel (R 5-bit, G 6-bit, B 5-bit), 65,536 Colors

- 6.2.4 18-bits/pixel (R 6-bit, G 6-bit, B 6-bit), 262,144 Colors

- 6.2.5 24-bits/pixel (R 8-bit, G 8-bit, B 8-bit), 16,777,216 Colors

- 6.3 9-bit interface

-

- 6.3.1 18-bits/pixel (R 6-bit, G 6-bit, B 6-bit), 262,144 Colors

- 6.4 16-bit Interface

-

- 6.4.1 8-bits/pixel (R 3-bit, G 3-bit, B 2-bit), 256 Colors

- 6.4.2 12-bits/pixel (R 4-bit, G 4-bit, B 4-bit), 4,096 Colors

- 6.4.3 16-bits/pixel (R 5-bit, G 6-bit, B 5-bit), 65,536 Colors

- 6.4.4 18-bits/pixel (R 6-bit, G 6-bit, B 6-bit), 262,144 Colors - Option 1

- 6.4.5 18-bits/pixel (R 6-bit, G 6-bit, B 6-bit), 262,144 Colors - Option 2

- 6.4.6 24-bits/pixel (R 8-bit, G 8-bit, B 8-bit), 16,777,216 Colors - Option 1

- 6.4.7 24-bits/pixel (R 8-bit, G 8-bit, B 8-bit), 16,777,216 Colors - Option 2

1 Overview

DBI全称Display Bus Interface, 是用于主机到显示设备的的一种数据传输标准,与之前《06_MIPI打怪升级之DPI》提到的DPI对应。均是由MIPI联盟退出的多媒体相关协议。DBI特点在于需要显示设备内置帧缓冲buffer,一般称之为GRAM,而通过DBI发送一帧数据之后,主机与DBI就可以停止了,显示设备可以根据自行设置的帧率去GRAM中取数据。

参考文档:《MIPI Alliance Standard for Display Bus Interface v2.0》

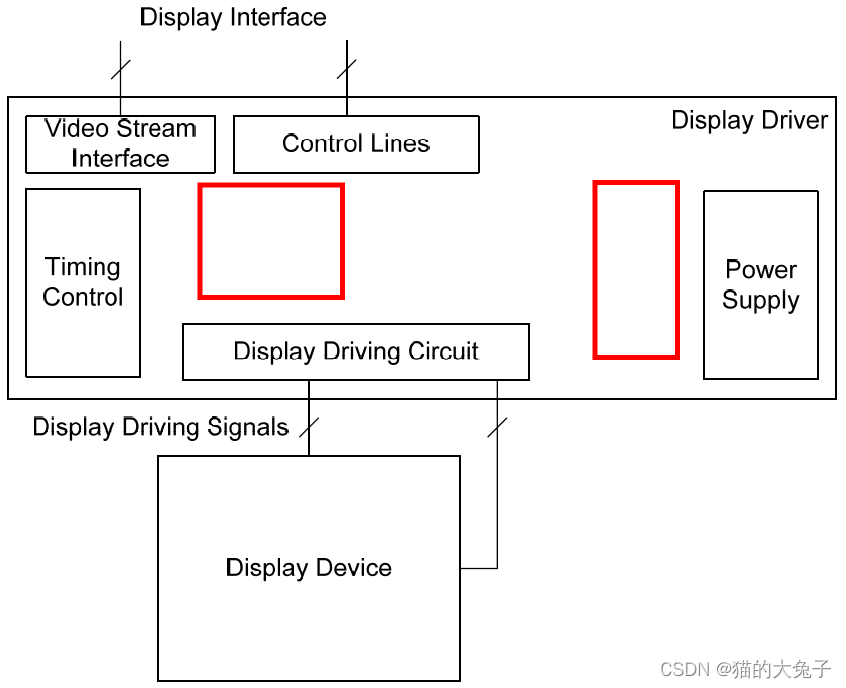

2 Display Architectures

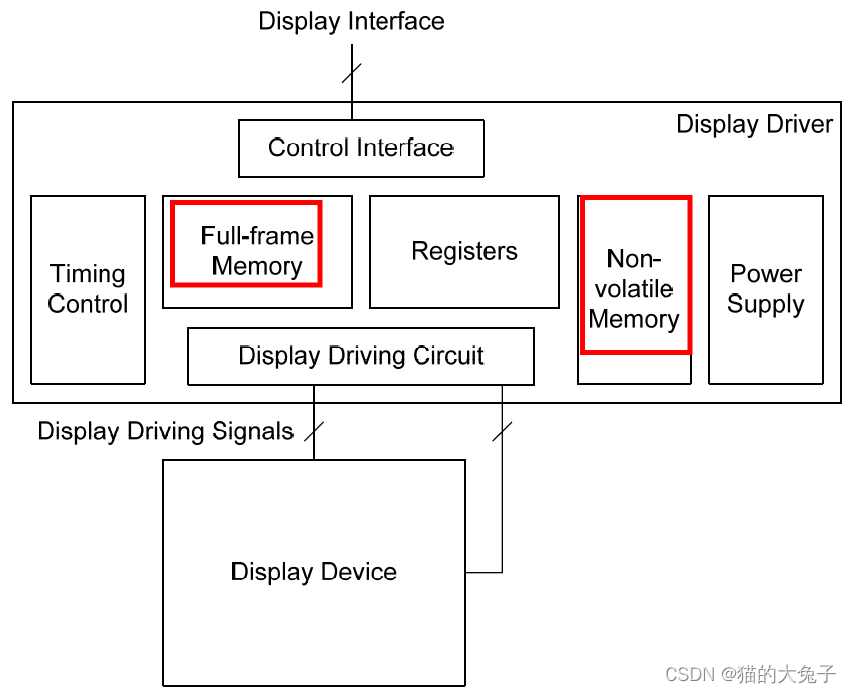

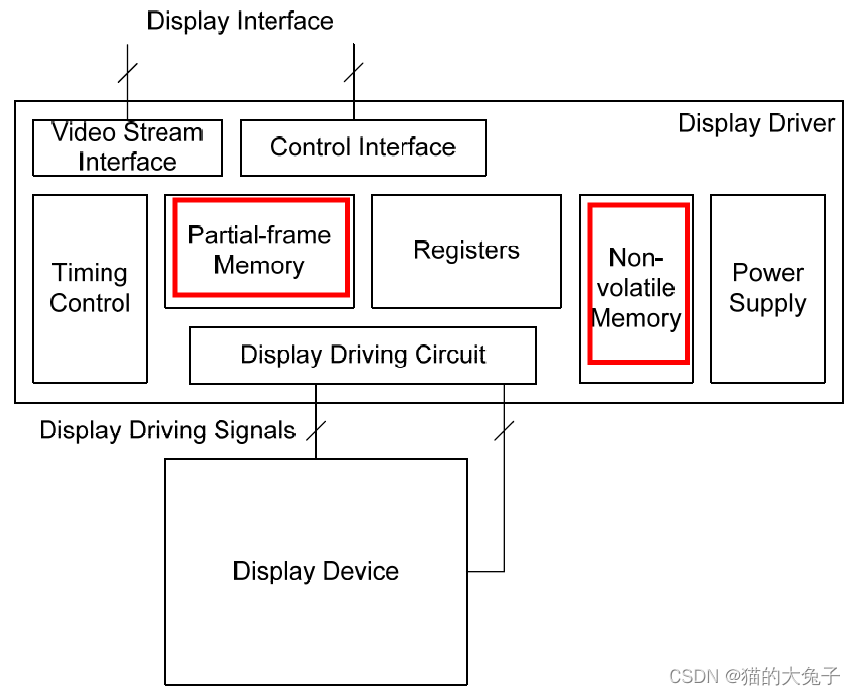

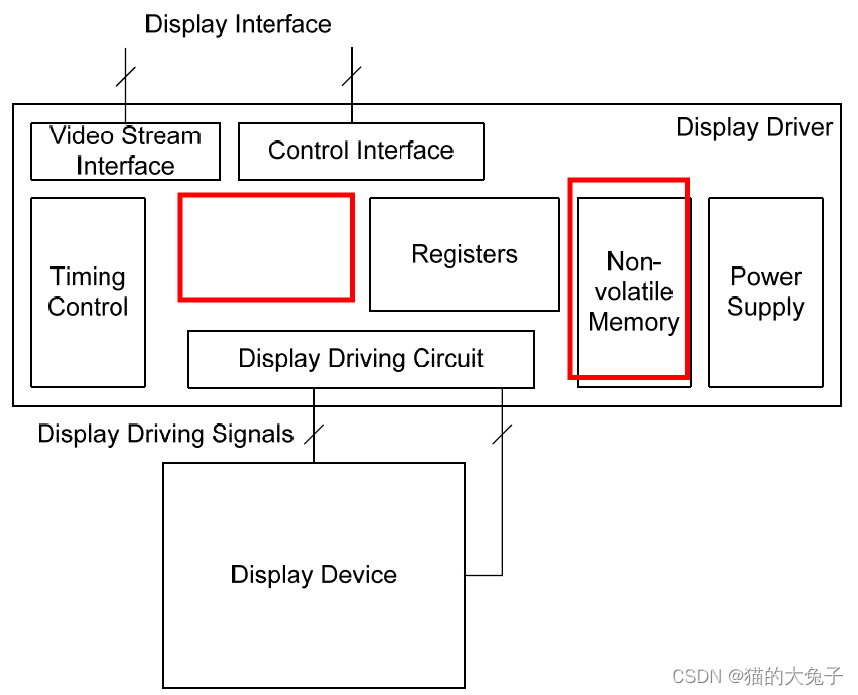

显示模块应基于如下4种显示架构:

根据是否有帧缓存buffer与寄存器配置存储进行区分

- The Type 1 Display Architecture:

- The Type 2 Display Architecture:

- The Type 3 Display Architecture:

- The Type 4 Display Architecture:

2.1 Type 1 Display Architecture Block Diagram

2.2 Type 2 Display Architecture Block Diagram

2.3 Type 3 Display Architecture Block Diagram

2.4 Type 4 Display Architecture Block Diagram

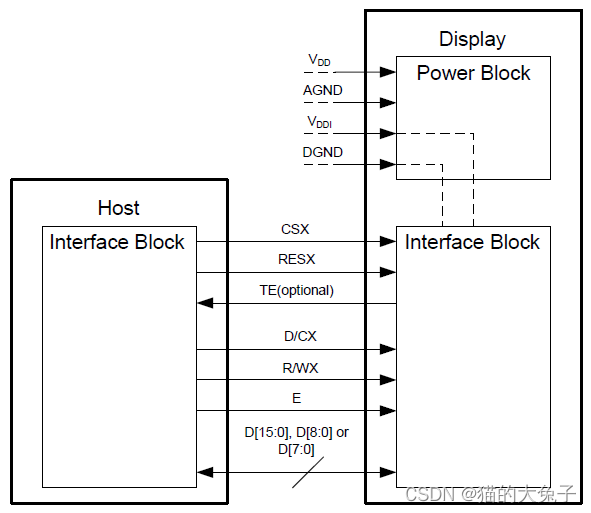

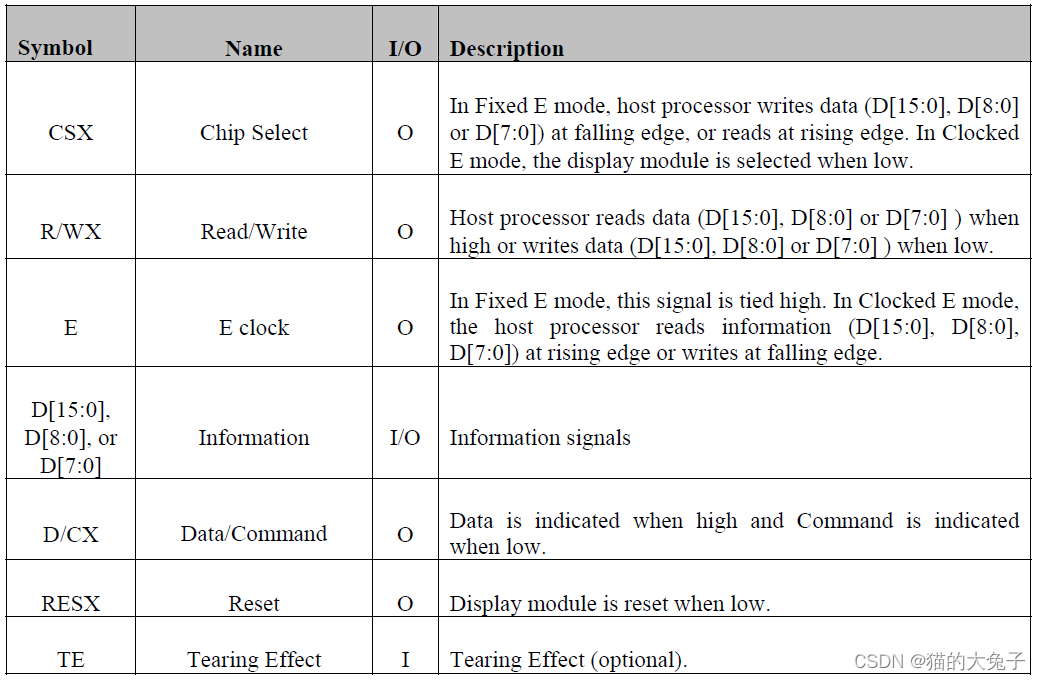

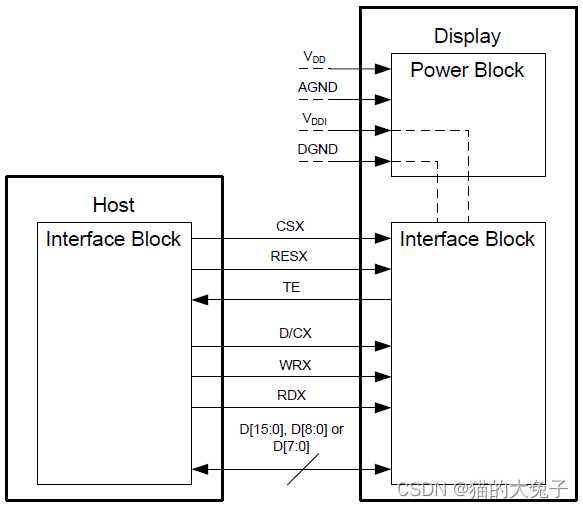

3 Interface Signal Description

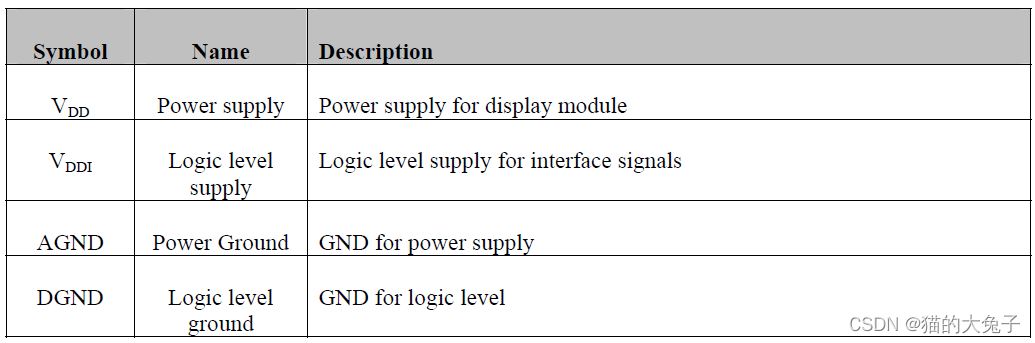

在主处理器和显示模块之间有两种类型的信号连接:

- 电源信号。 电源由主处理器或由主处理器控制的电源管理单元提供。

- 接口信号。 使用接口信号在主处理器和显示模块之间传输像素数据、命令和控制信息。

存在三种类型的 DBI 实现,命名为 A、B 和 C,其差异在于Interface Signals,而Power Supply Signals一致。

3.1 Type A Interface Block Diagram

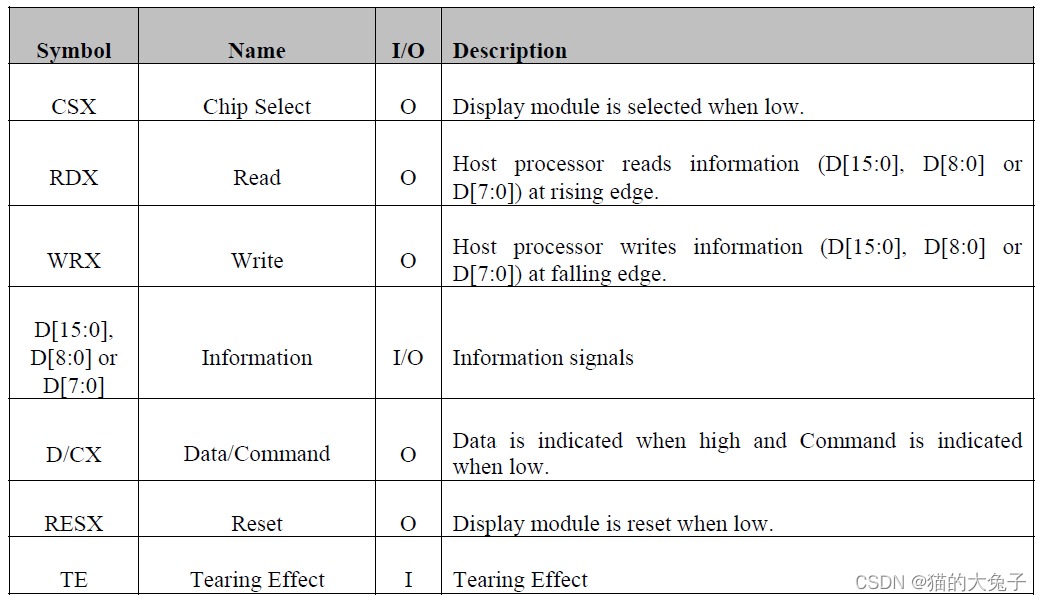

3.2 Type B Interface Block Diagram

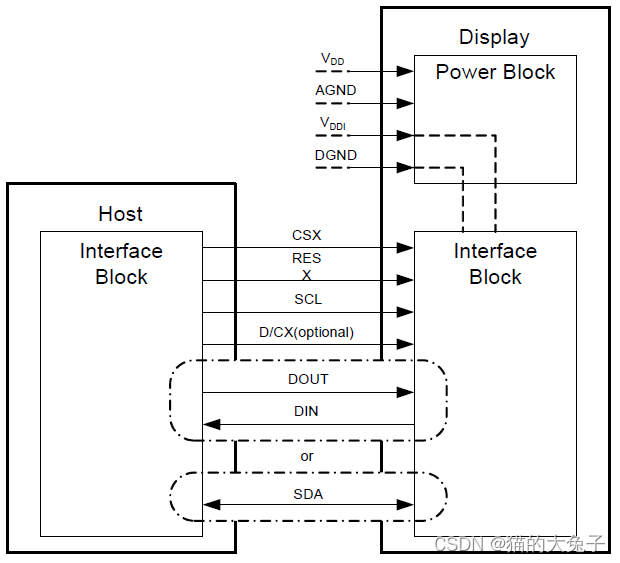

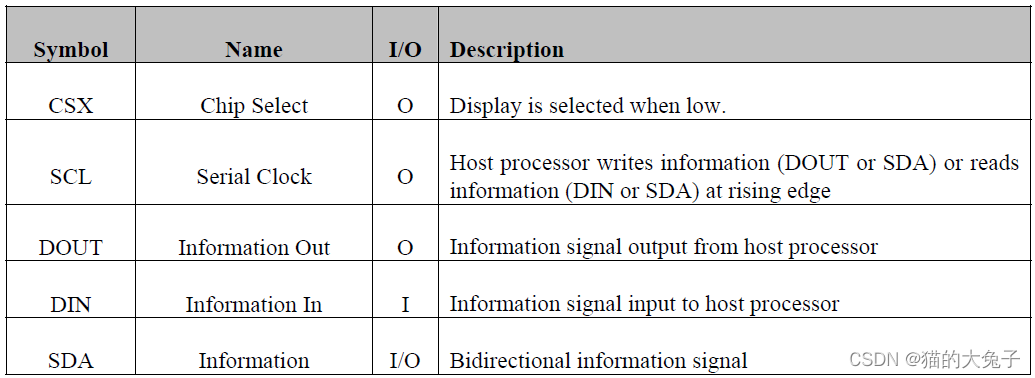

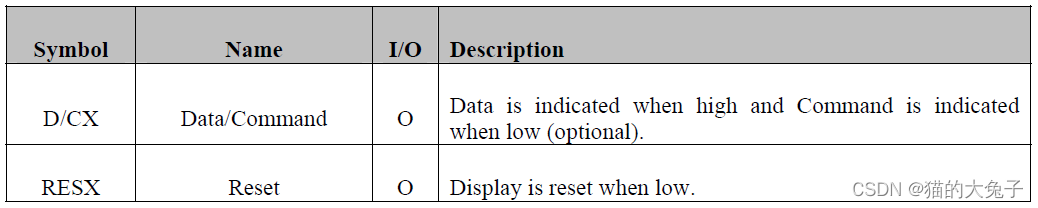

3.3 Type C Interface Block Diagram

3.4 Power Supply Signals

4 Interface Functional

4.1 Type A Interface Write and Read Cycles

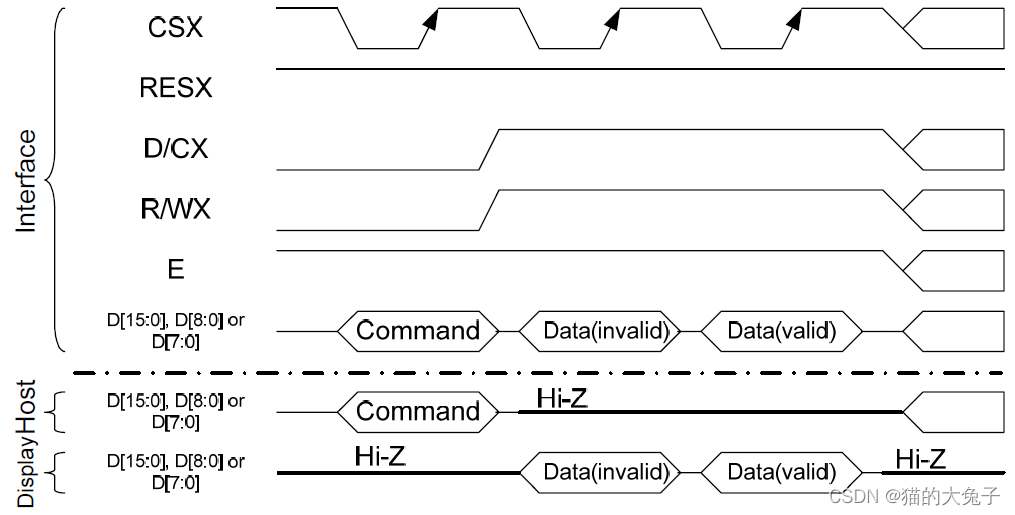

在写周期期间,主机处理器通过接口将命令或数据写入显示模块。A 类接口支持两种模式:Fixed E 和Clocked E。两种模式都使用 CSX、D/CX、R/WX 和 E 信号以及 所有八个 (D[7:0])、九个 (D[8:0]) 或十六个 (D[15:0]) 信息信号。 当接口上存在命令时,D/CX 被驱动为低电平,当接口上存在数据时,D/CX 被拉高。

在读取周期期间,主机处理器通过接口从显示模块读取数据。 A 型接口支持两种模式:Fixed E 和 Clocked E。两种模式都使用 CSX、D/CX、R/WX 和 E 信号以及所有 8 个 (D[7:0])、9 个 (D[8:0] ) 或十六个 (D[15:0]) 信息信号。 D/CX 在整个读取周期内被驱动为低电平。

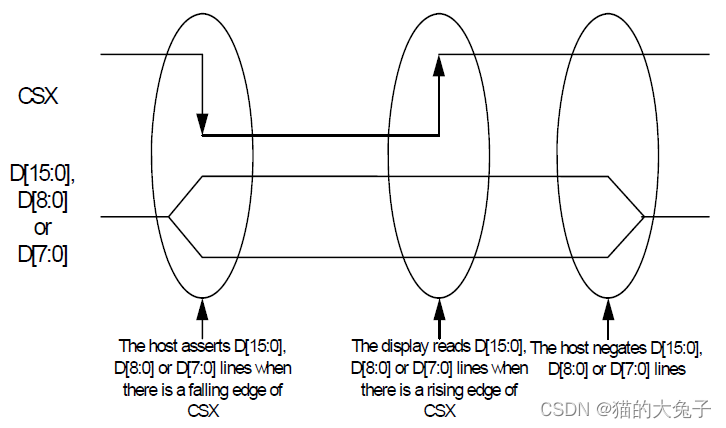

Type A Interface - Fixed E Mode Write Cycle:

- CSX 是非同步信号; 它可以停止。

- E 信号在Fixed E 模式下连接高电平。

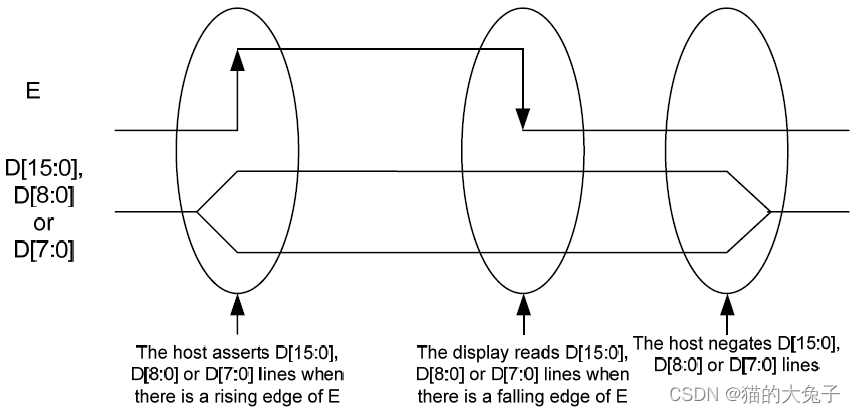

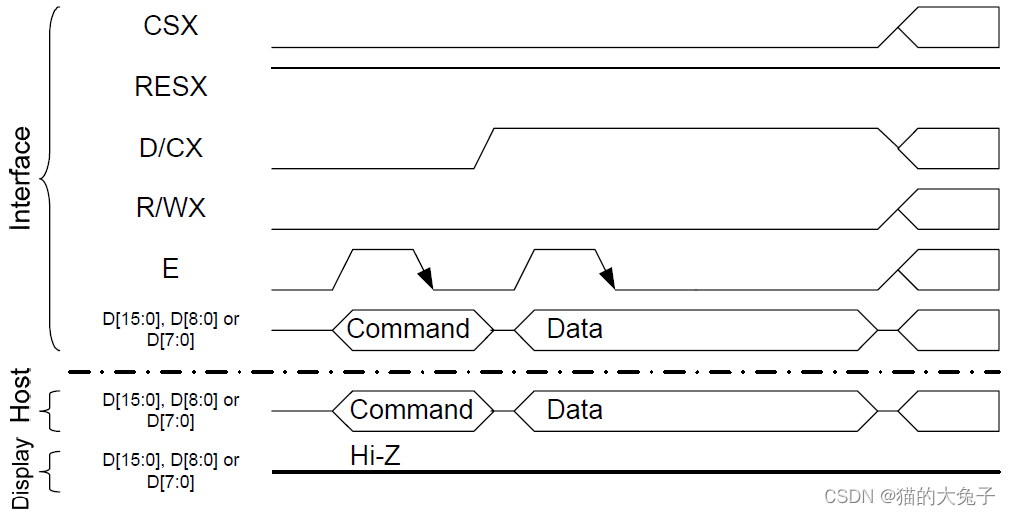

Type A Interface - Clocked E Mode Write Cycle:

- E是非同步信号; 它可以停止

- CSX 被断言(拉低)的持续时间与信息信号相同

4.1.1 Type A Interface - Example Fixed E Mode RW Sequence

Type A Interface - Example Fixed E Mode Write Sequence:

Type A Interface - Example Fixed E Mode Read Sequence:

4.1.2 Type A Interface - Example Clocked E Mode RW Sequence

Type A Interface - Example Clocked E Mode Write Sequence:

Type A Interface - Example Clocked E Mode Read Sequence:

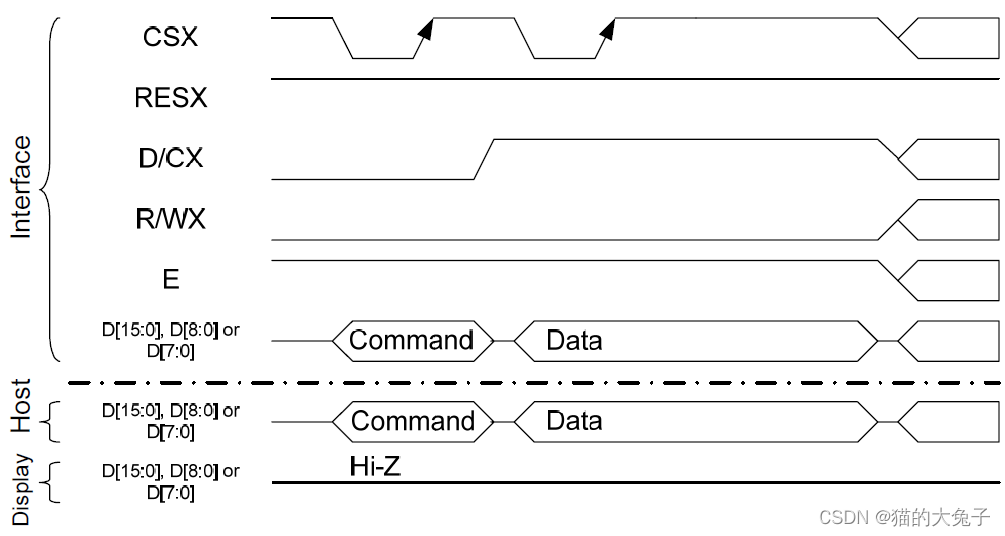

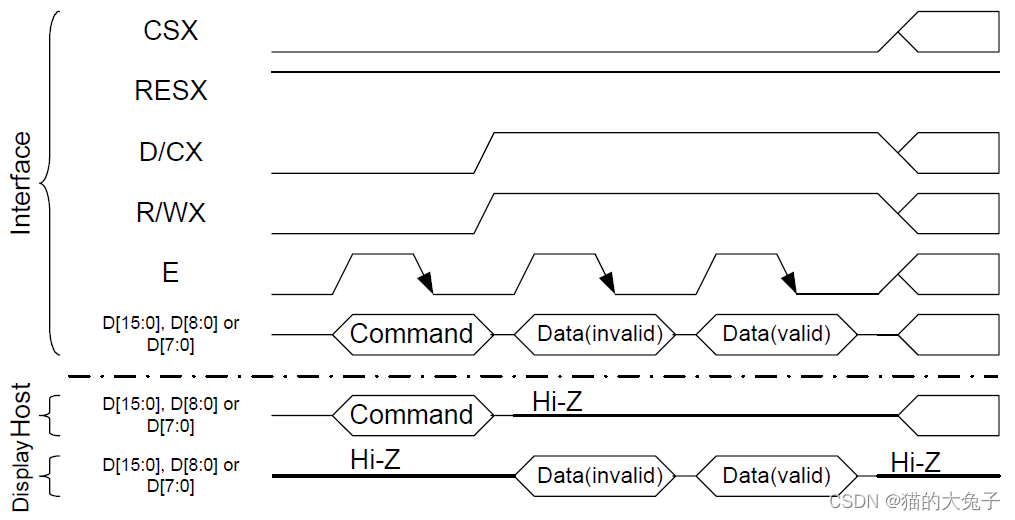

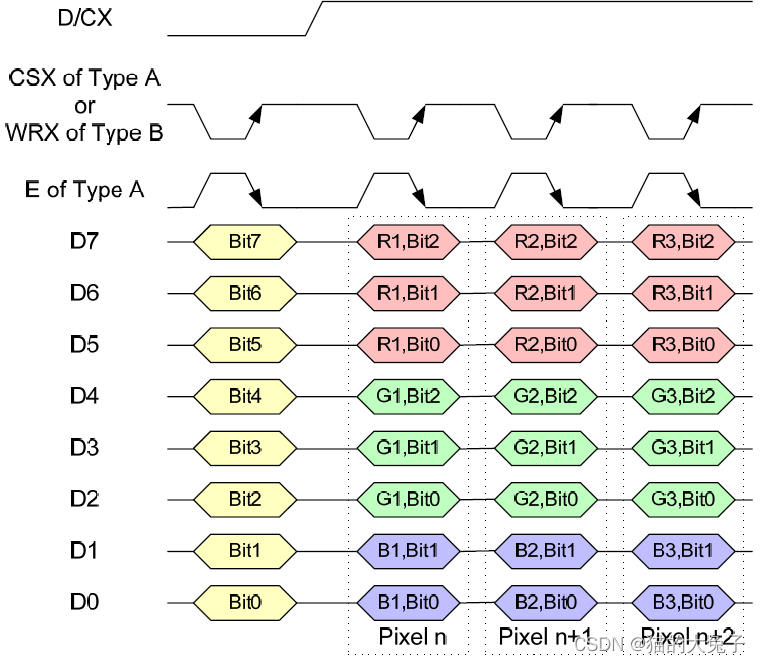

4.2 Type B Interface Write and Read Cycles

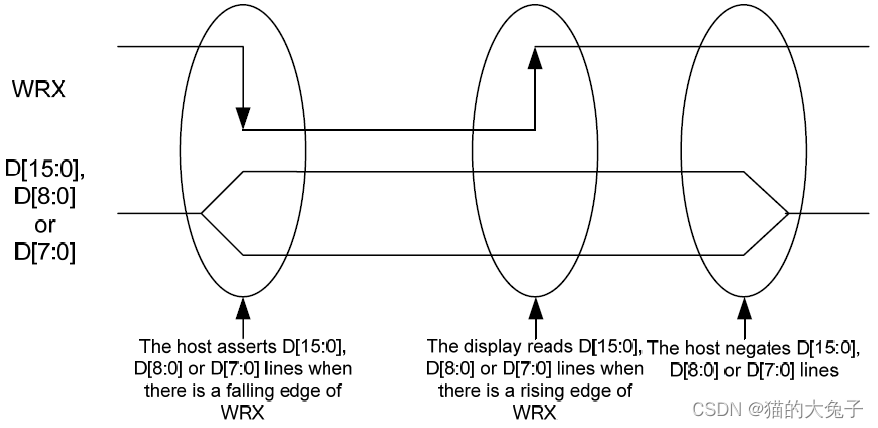

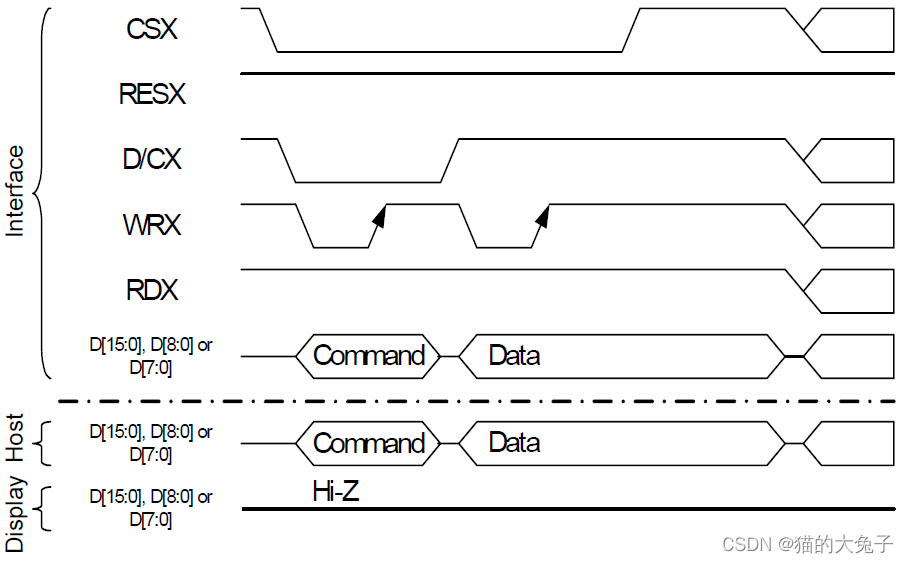

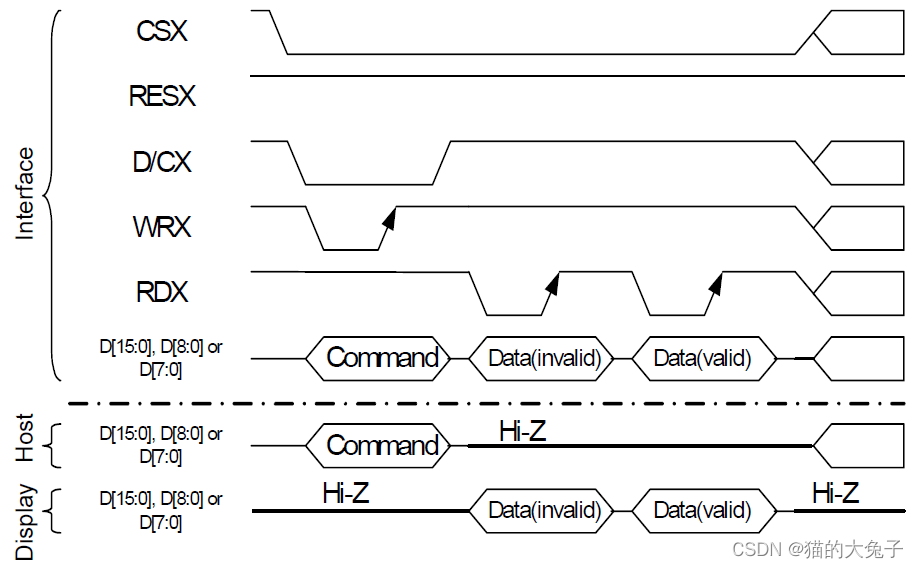

在写周期期间,主处理器通过接口向显示模块发送数据。 B 类接口使用 D/CX、RDX 和 WRX 信号以及所有八个 (D[7:0])、九个 (D[8:0]) 或十六个 (D[15:0]) 信息信号。 WRX 在写周期中从高电平驱动到低电平,然后拉回到高电平。 主机处理器在写周期期间提供信息,而显示模块在 WRX 的上升沿读取主机处理器信息。 当命令信息在接口上时,D/CX 被驱动为低电平,当数据存在时被拉高。

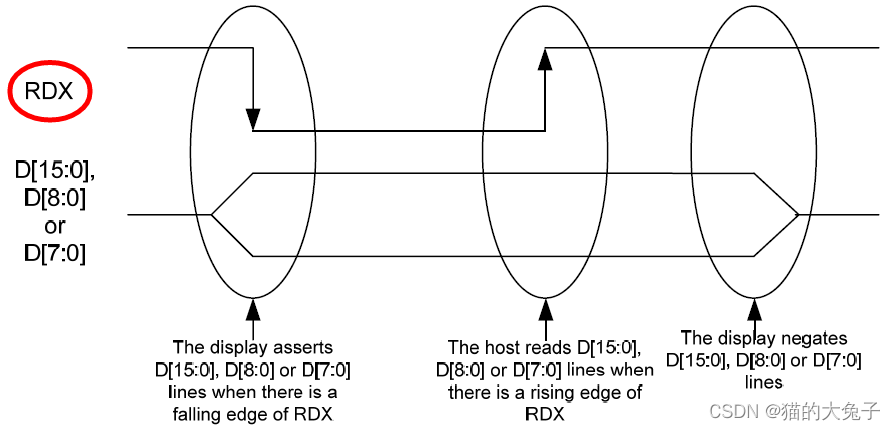

在读取周期期间,主机处理器通过接口从显示模块读取数据。 B 类接口使用 D/CX、RDX 和 WRX 信号以及所有八个 (D[7:0])、九个 (D[8:0]) 或十六个 (D[15:0]) 信息信号。 RDX 从高电平驱动到低电平,然后在读取周期内被拉回高电平。 显示模块在读取周期内向主机处理器提供信息,而主机处理器在 RDX 的上升沿读取显示模块信息。 D/CX 在读周期被驱动为高电平。

4.2.1 Type B Interface Example RW Sequence

Type B Interface Examplle Write Sequence:

Type B Interface Examplle Read Sequence:

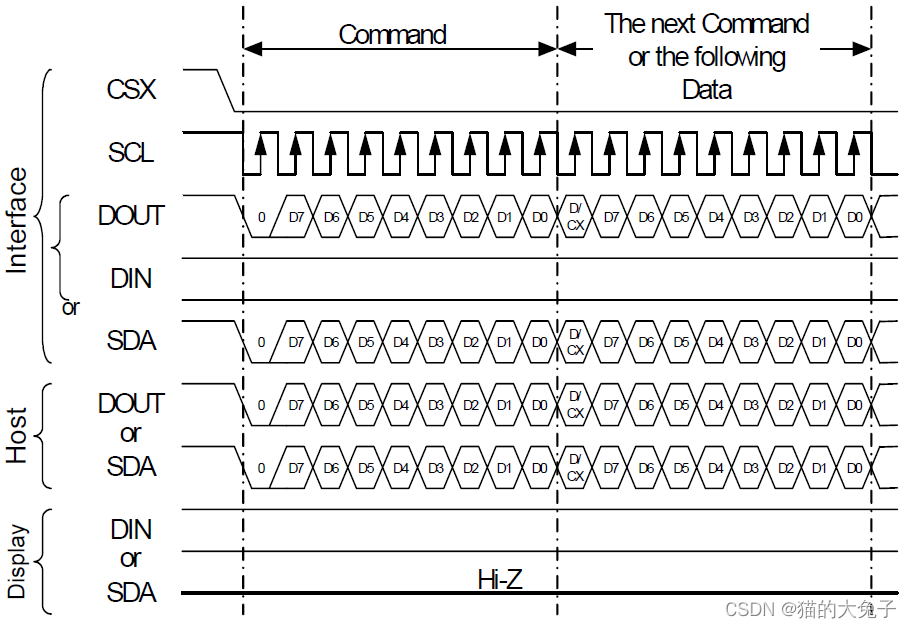

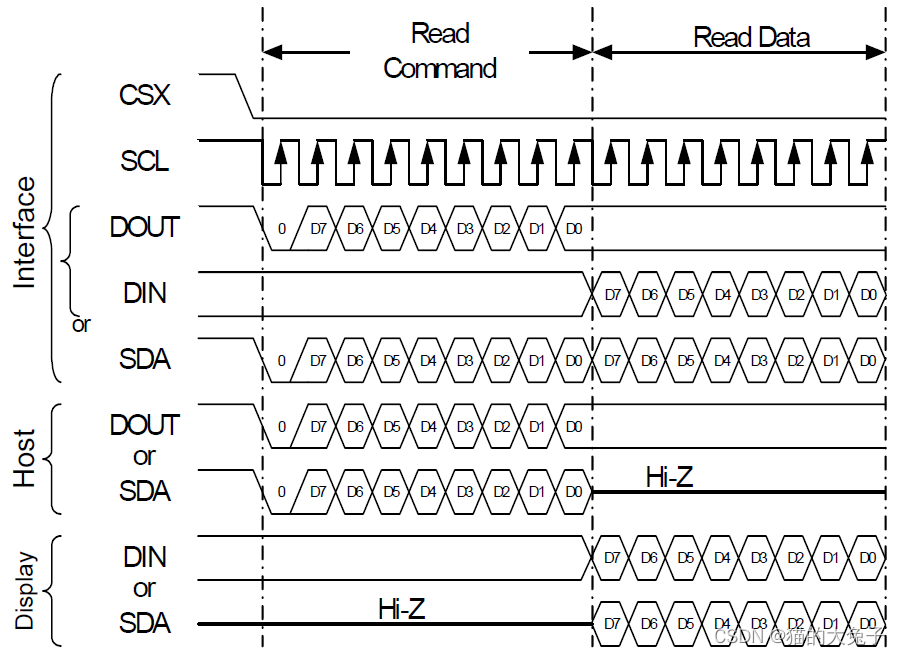

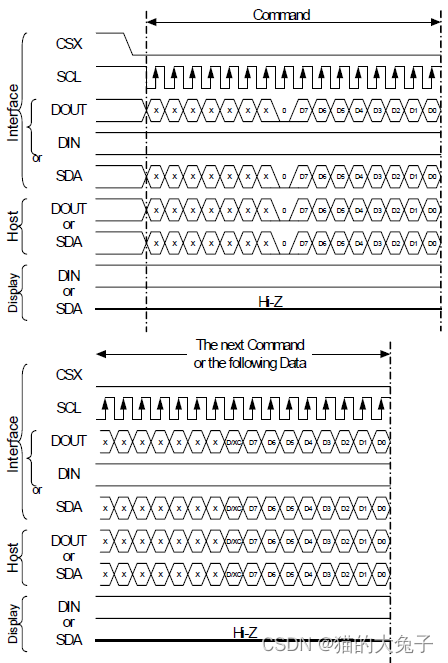

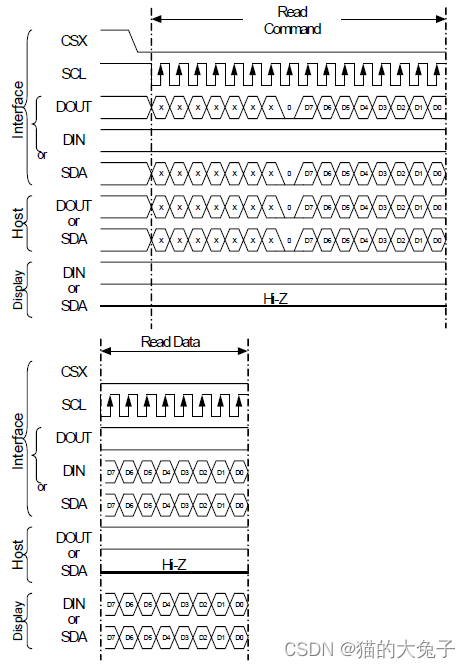

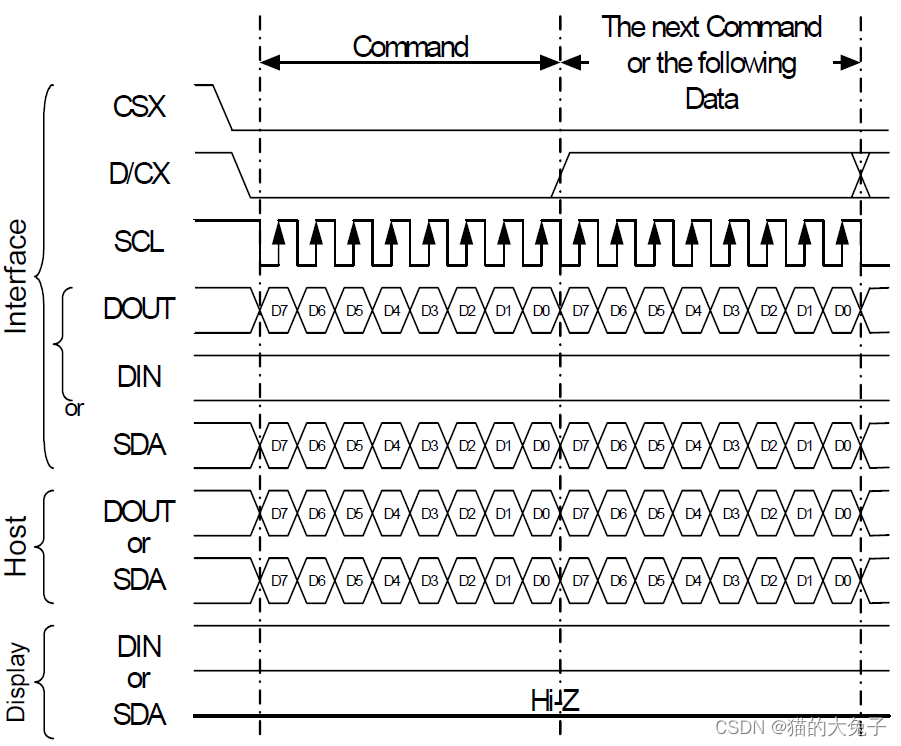

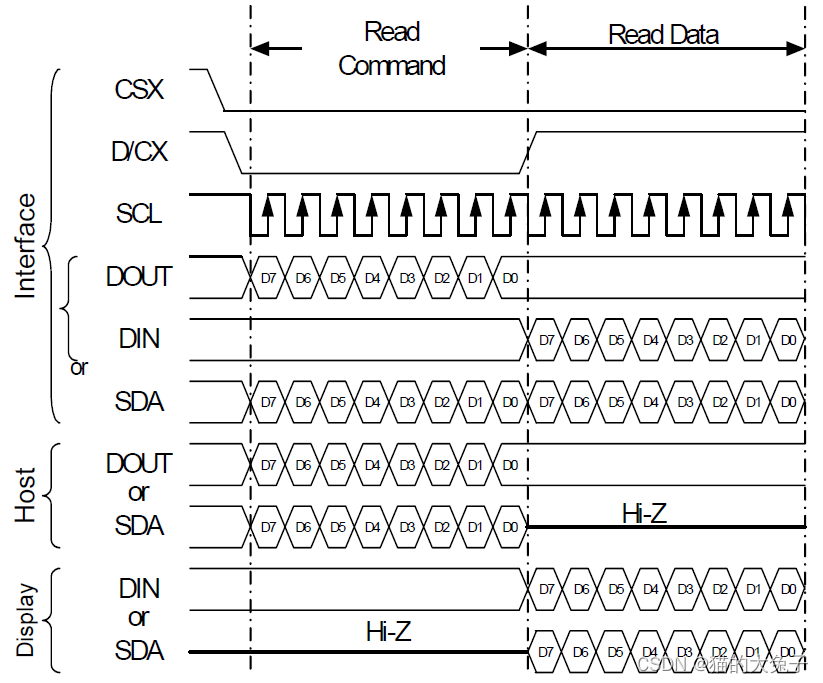

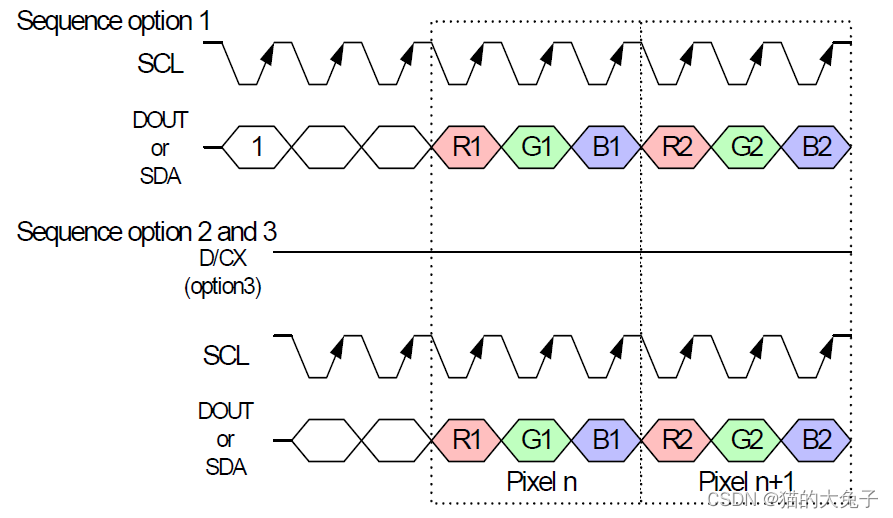

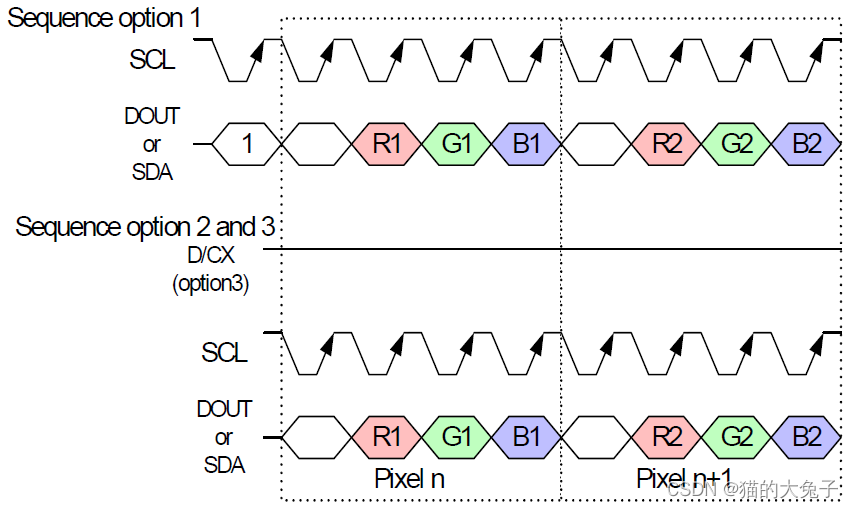

4.3 Type C Interface Write and Read Cycles

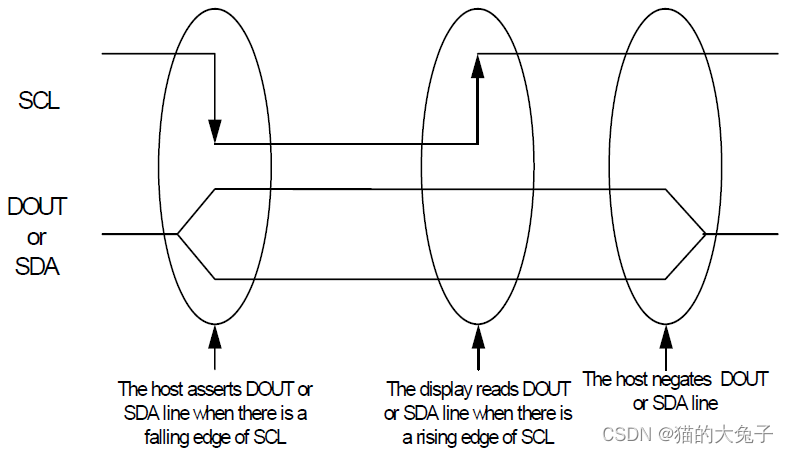

在写周期期间,主机处理器通过接口向显示模块发送一位数据。C 类接口利用 CSX、SCL 和 SDA 或 DOUT 信号。 在写周期中,SCL 从高电平驱动到低电平,然后拉回高电平。 主机处理器在写周期期间提供信息,而显示模块在 SCL 的上升沿读取主机处理器信息。

在读取周期期间,主机处理器通过接口从显示模块读取一位数据。C 类接口利用 CSX、SCL 和 SDA 或 DIN 信号。 SCL 在读周期中从高电平驱动到低电平,然后拉回高电平。 显示模块在读取周期期间提供信息,而主机处理器在 SCL 的上升沿读取显示模块信息。 如果在选项 3 中使用 D/CX,则在读取周期期间驱动它。

在写入序列期间,主机处理器通过接口将一个或多个字节的信息写入显示模块。 写序列在 CSX 从高电平驱动到低电平时启动,并在 CSX 拉高时结束。 每个字节的长度为 9 或 16 个写周期。 如果使用可选的 D/CX 信号,则一个字节的长度为 8 个写周期。 当命令信息在接口上时,D/CX 被驱动为低电平,当数据存在时被拉高。

在读取序列期间,主机处理器通过接口从显示模块读取一个或多个字节的信息。 读取序列在 CSX 从高电平驱动到低电平时启动,并在 CSX 拉高时结束。 每个字节的长度为 9 或 16 个写周期。 如果使用可选的 D/CX 信号,则一个字节为八个读取周期长。 当命令信息在接口上时,D/CX 被驱动为低电平,当数据存在时被拉高。。

D7 is MSB and D0 is LSB of byte

针对读写时序,有三种版本,其主要却别在于命令和数据的线上格式差异。

4.3.1 Type C Interface RW Sequence - Option 1

Type C Interface Write Sequence – Option 1:

Type C Interface Read Sequence – Option 1:

4.3.2 Type C Interface RW Sequence - Option 2

Type C Interface Write Sequence – Option 2:

Type C Interface Read Sequence – Option 2:

4.3.3 Type C Interface RW Sequence - Option 3

Type C Interface Write Sequence – Option 3:

Type C Interface Read Sequence – Option 3:

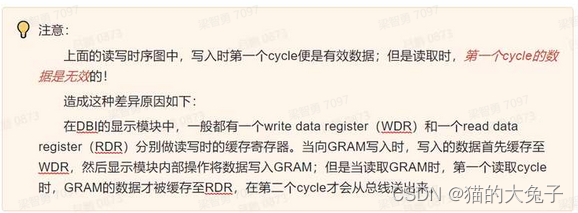

4.4 Note

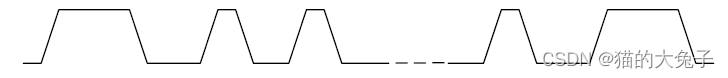

5 Tearing Effect

显示模块可以使用TE信号向主处理器提供内部信号,其主要有两种方式,如下所示:

-

Tearing Effect Signal with VSYNC

-

Tearing Effect Signal with VSYNC + HSYNC

6 ColorCoding

颜色编码使用红色 [R]、绿色 [G] 和蓝色 [B] 加色混合方法。

6.1 3-bit Interface

6.1.1 3-bits/pixel (R 1-bit, G 1-bit, B 1-bit), Eight Colors - Option1

6.1.2 3-bits/pixel (R 1-bit, G 1-bit, B 1-bit), Eight Colors - Option2

6.2 8-bit Interface

6.2.1 8-bits/pixel (R 3-bit, G 3-bit, B 2-bit), 256 Colors

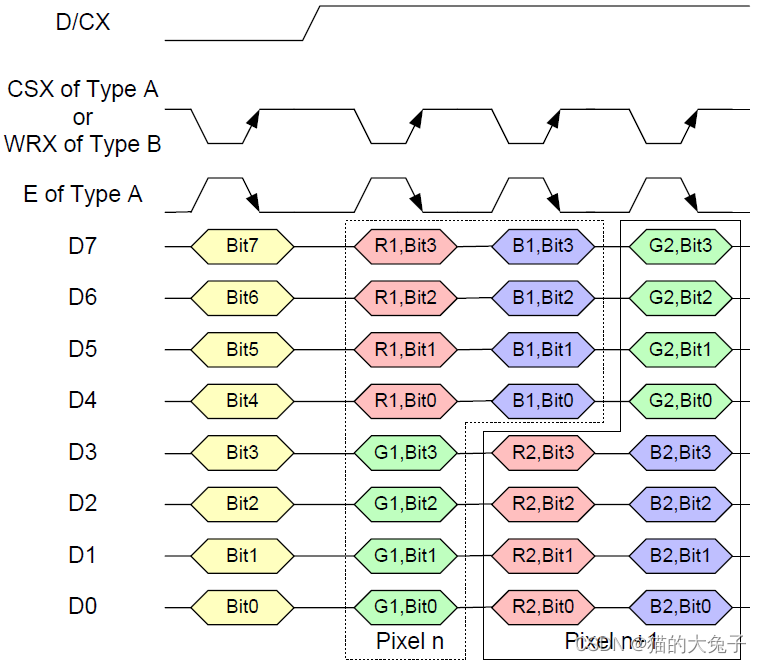

6.2.2 12-bits/pixel (R 4-bit, G 4-bit, B 4-bit), 4,096 Colors

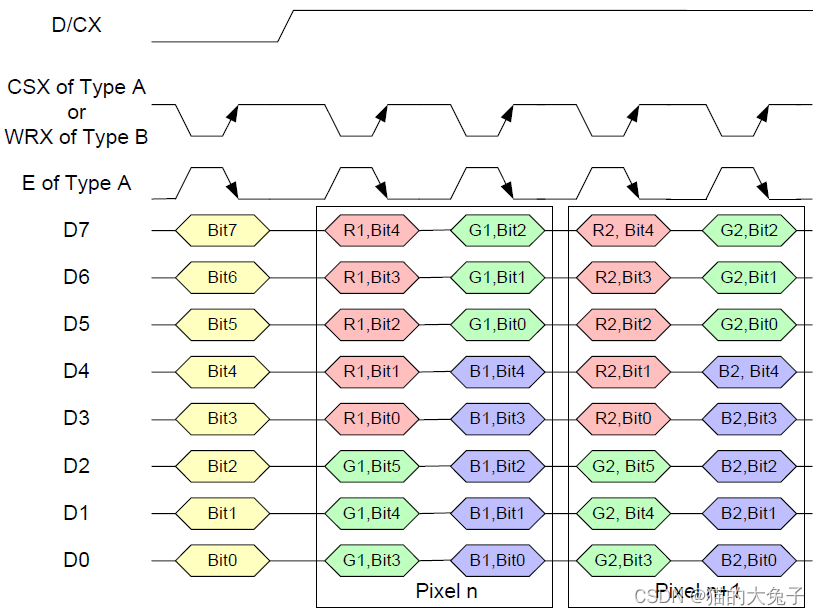

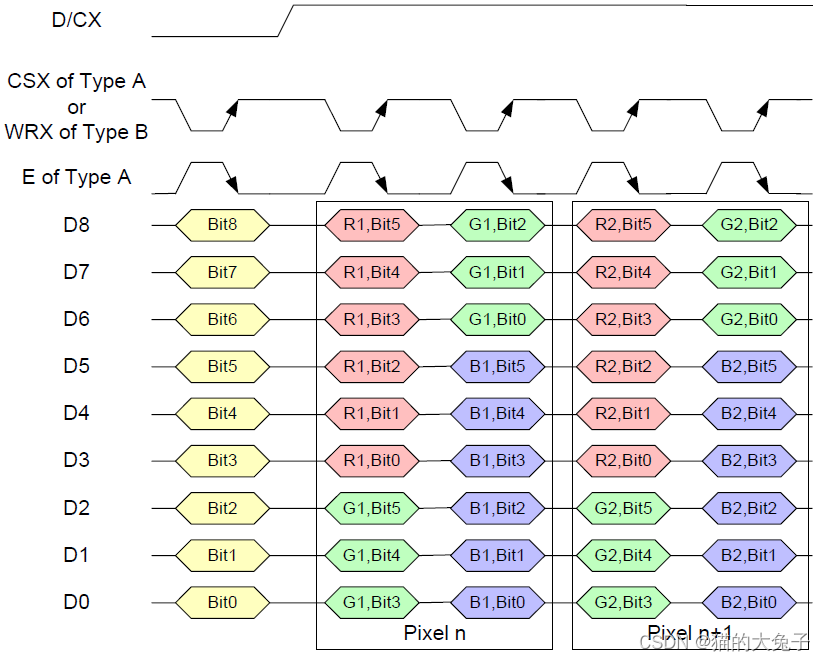

6.2.3 16-bits/pixel (R 5-bit, G 6-bit, B 5-bit), 65,536 Colors

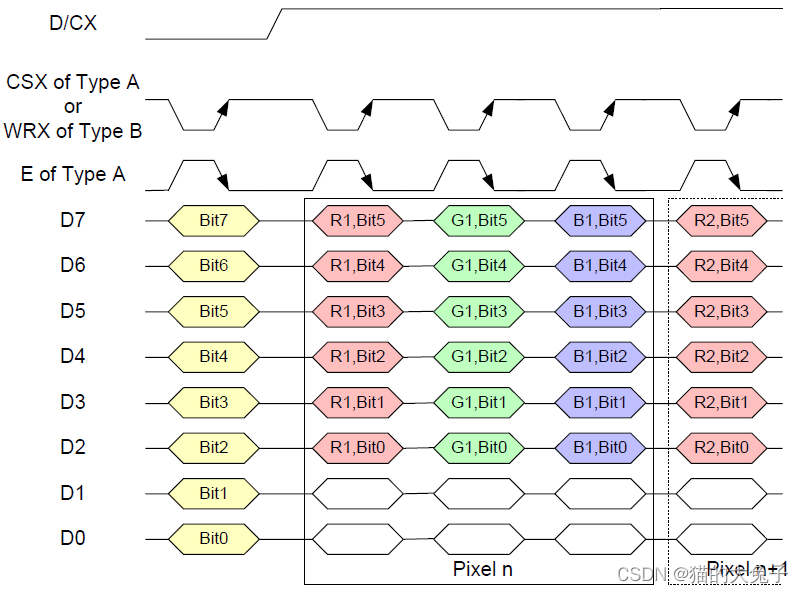

6.2.4 18-bits/pixel (R 6-bit, G 6-bit, B 6-bit), 262,144 Colors

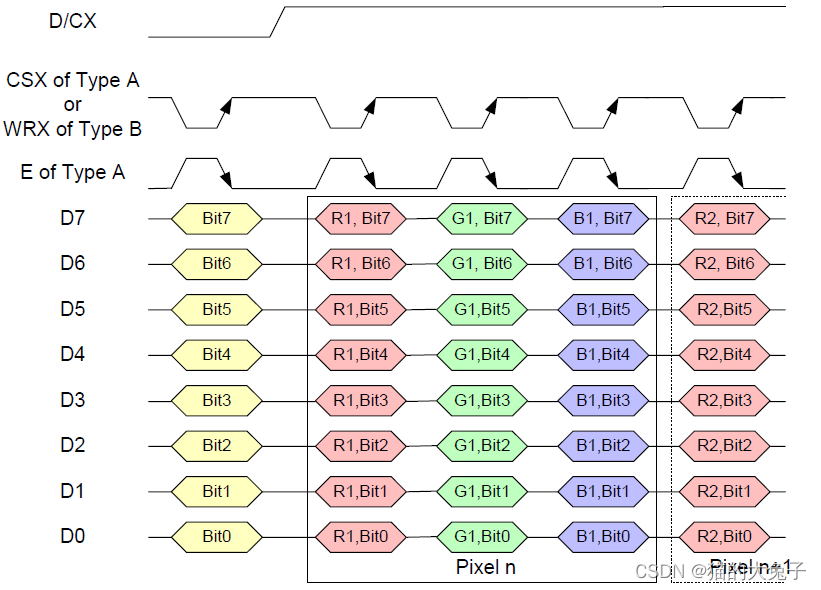

6.2.5 24-bits/pixel (R 8-bit, G 8-bit, B 8-bit), 16,777,216 Colors

6.3 9-bit interface

6.3.1 18-bits/pixel (R 6-bit, G 6-bit, B 6-bit), 262,144 Colors

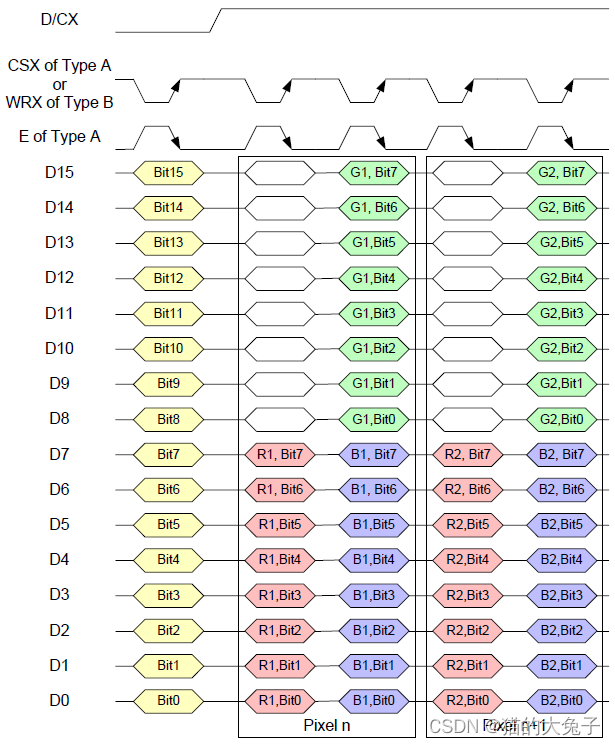

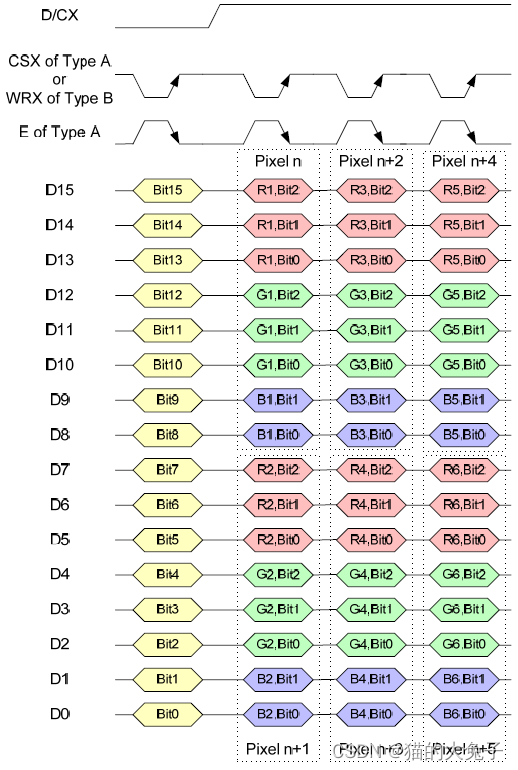

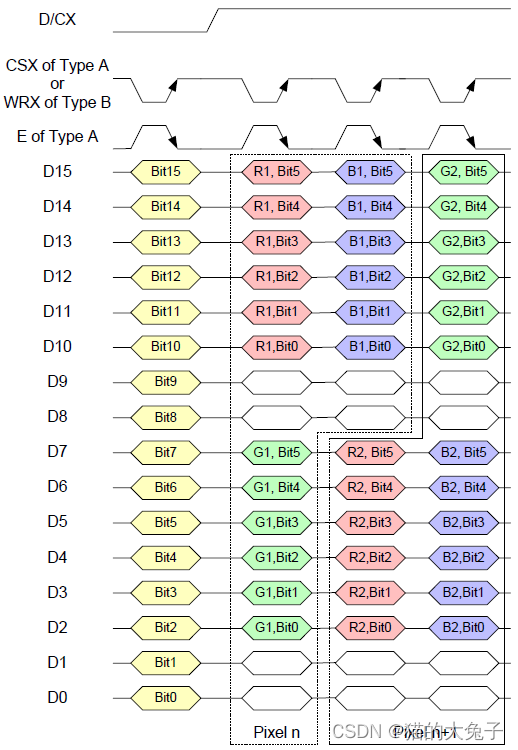

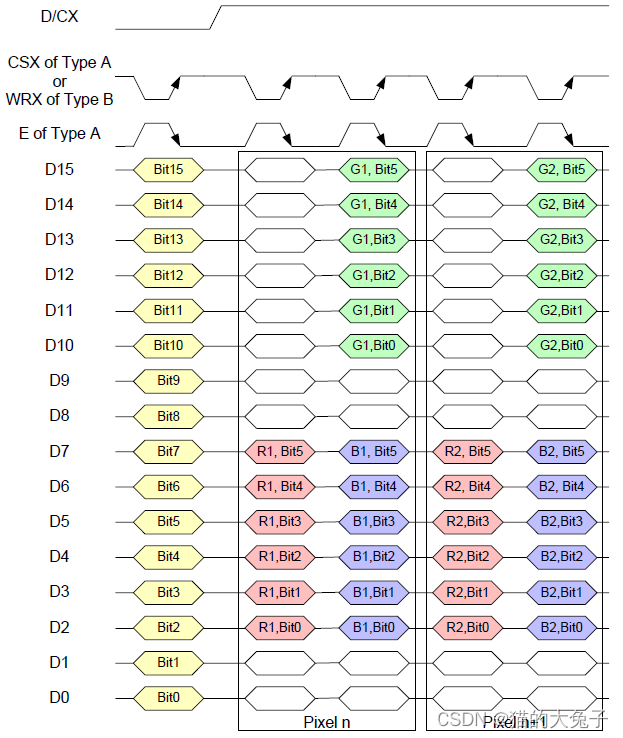

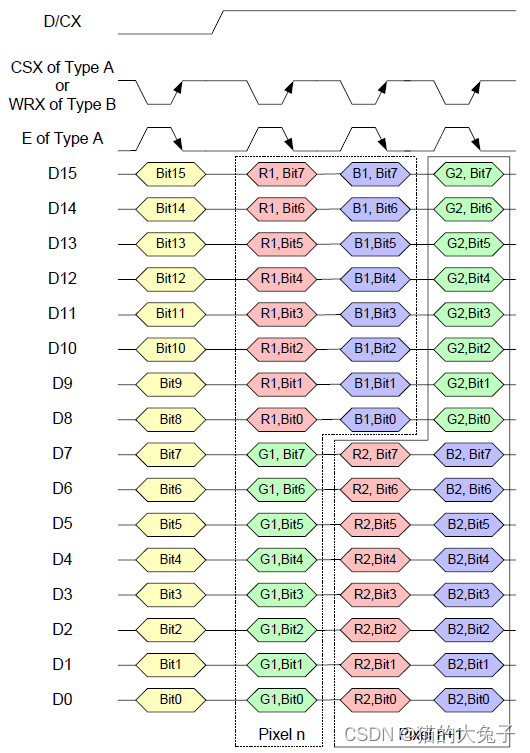

6.4 16-bit Interface

6.4.1 8-bits/pixel (R 3-bit, G 3-bit, B 2-bit), 256 Colors

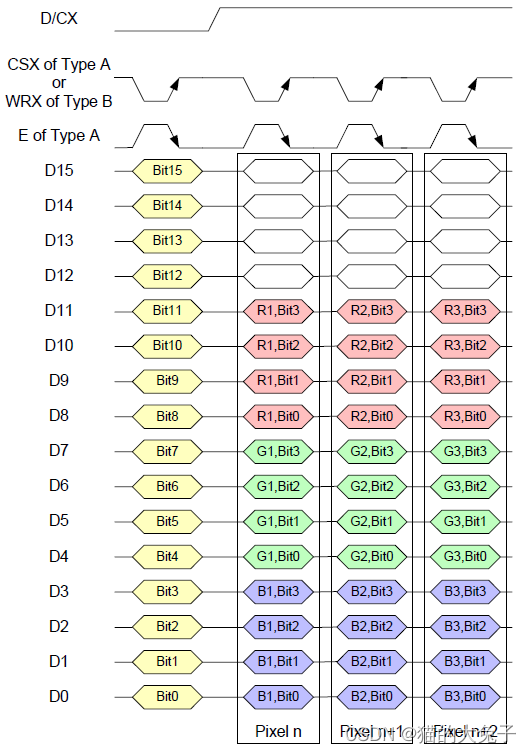

6.4.2 12-bits/pixel (R 4-bit, G 4-bit, B 4-bit), 4,096 Colors

6.4.3 16-bits/pixel (R 5-bit, G 6-bit, B 5-bit), 65,536 Colors

6.4.4 18-bits/pixel (R 6-bit, G 6-bit, B 6-bit), 262,144 Colors - Option 1

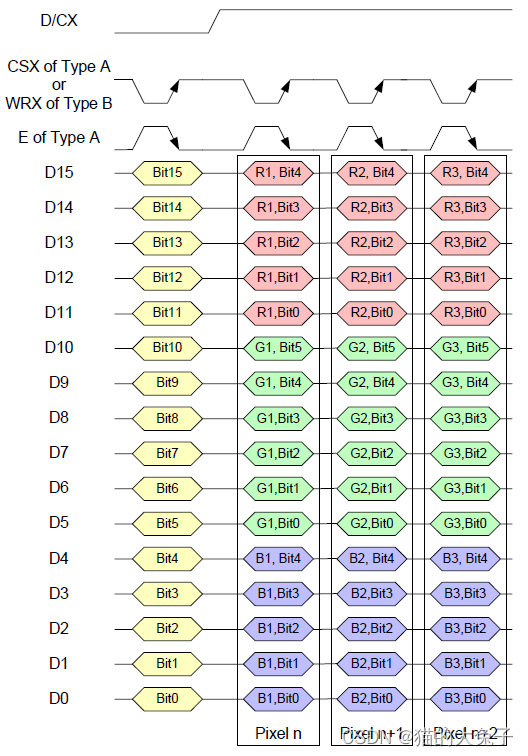

6.4.5 18-bits/pixel (R 6-bit, G 6-bit, B 6-bit), 262,144 Colors - Option 2

6.4.6 24-bits/pixel (R 8-bit, G 8-bit, B 8-bit), 16,777,216 Colors - Option 1

6.4.7 24-bits/pixel (R 8-bit, G 8-bit, B 8-bit), 16,777,216 Colors - Option 2