静态时序分析Static Timing Analysis4——多时钟域和多时钟时序检查

文章目录

- 前言

- 一、多时钟域时序分析

-

- 1、慢时钟域到快时钟域

-

- 1.1 建立时间检查

- 1.2 保持时间检查

- 1.3 多周期检查

- 2、快时钟域到慢时钟域

-

- 2.1 建立时间检查

- 2.2 保持时间检查

- 2.3 合理的约束

- 3、总结

- 二、多时钟

-

- 1、整数倍关系

- 2、非整数倍关系

- 三、相位移动

前言

2023.4.12 这里讲的多时钟域和多时钟都是指的同步电路,异步电路是不进行STA的,如果是CDC的话,直接就set_false_path了

一、多时钟域时序分析

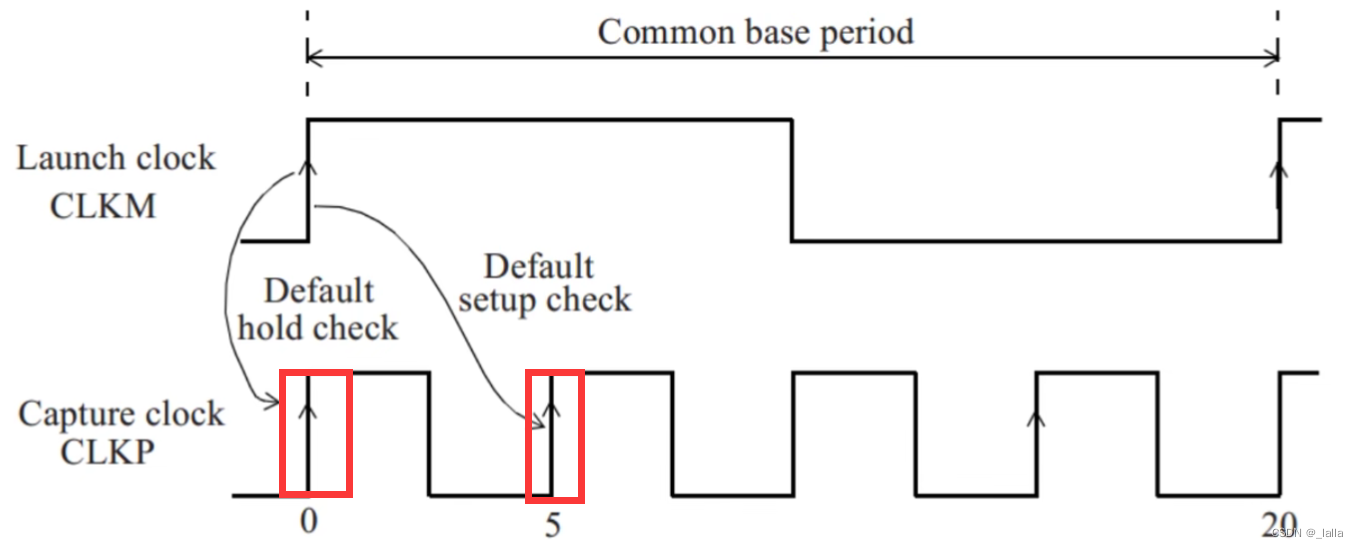

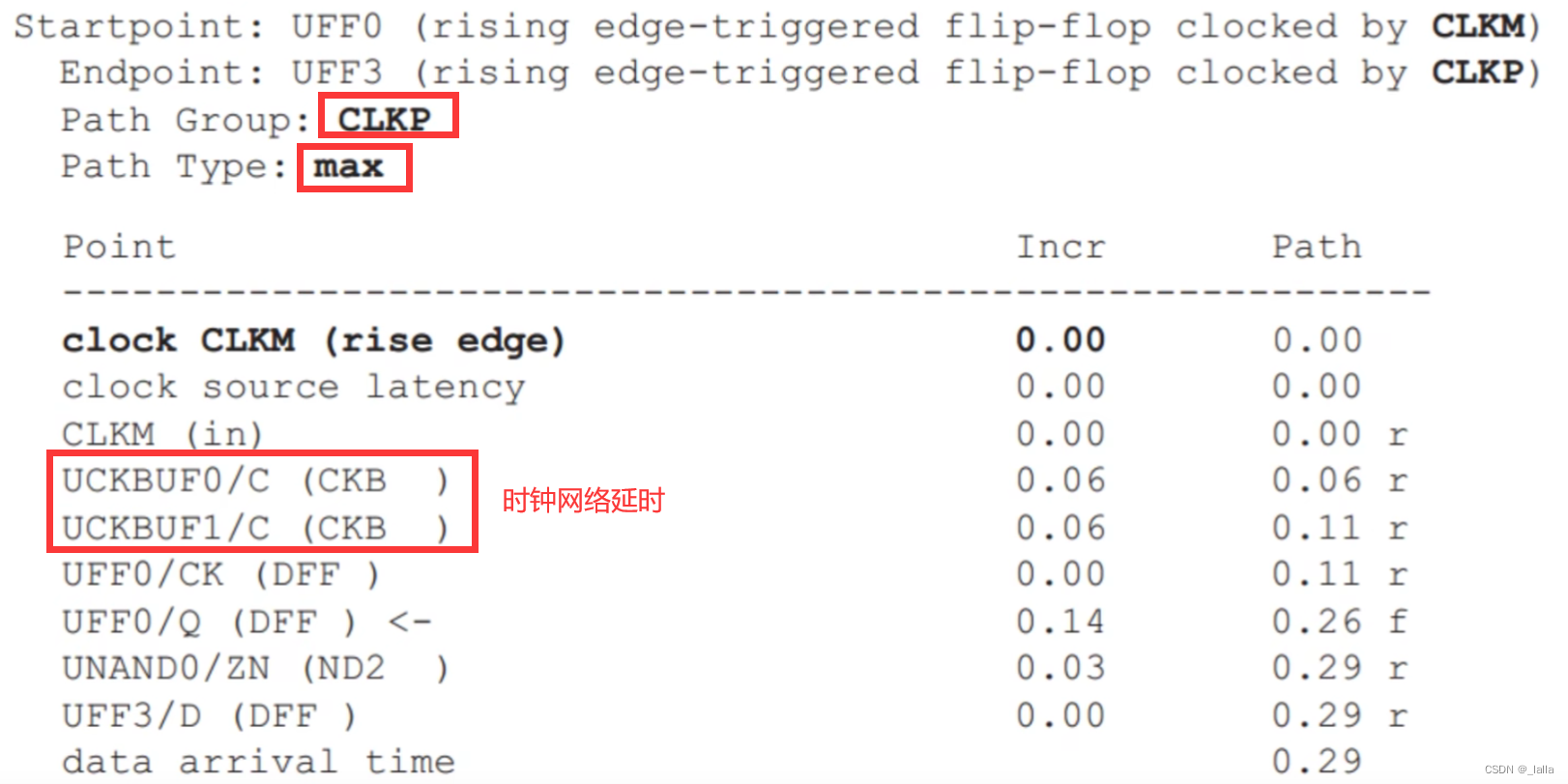

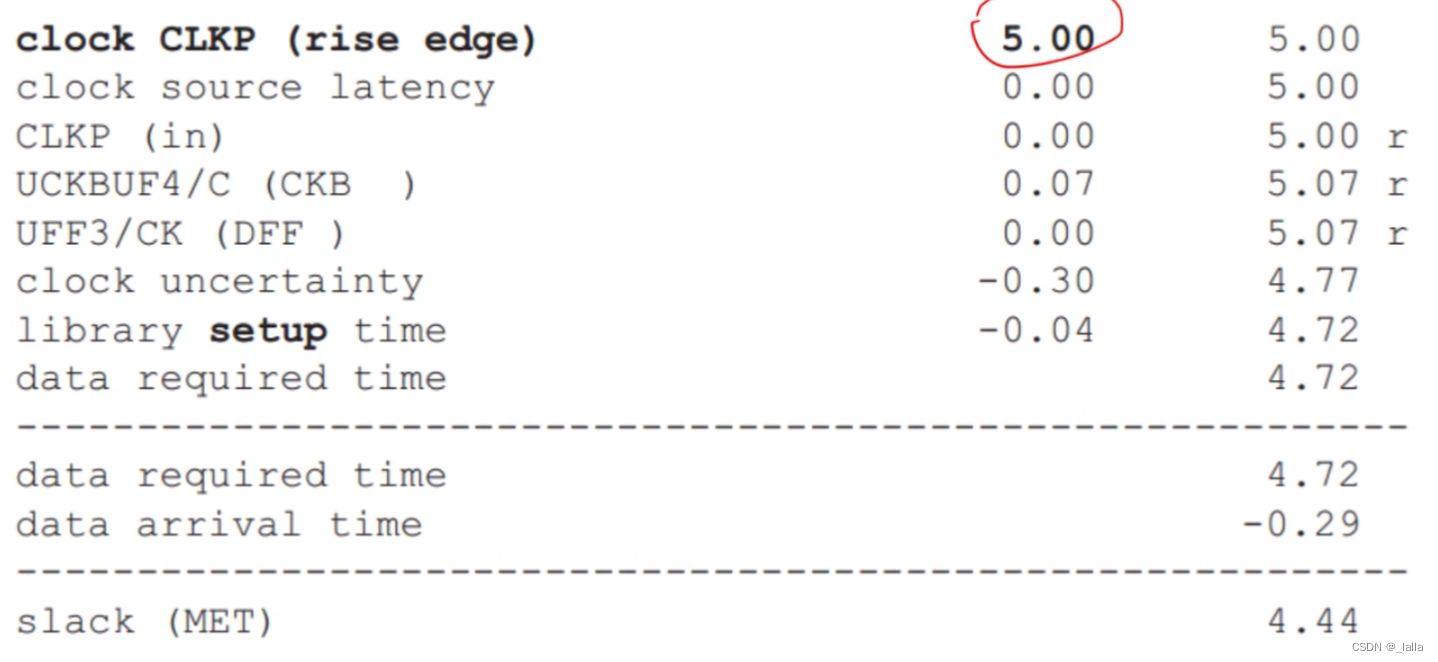

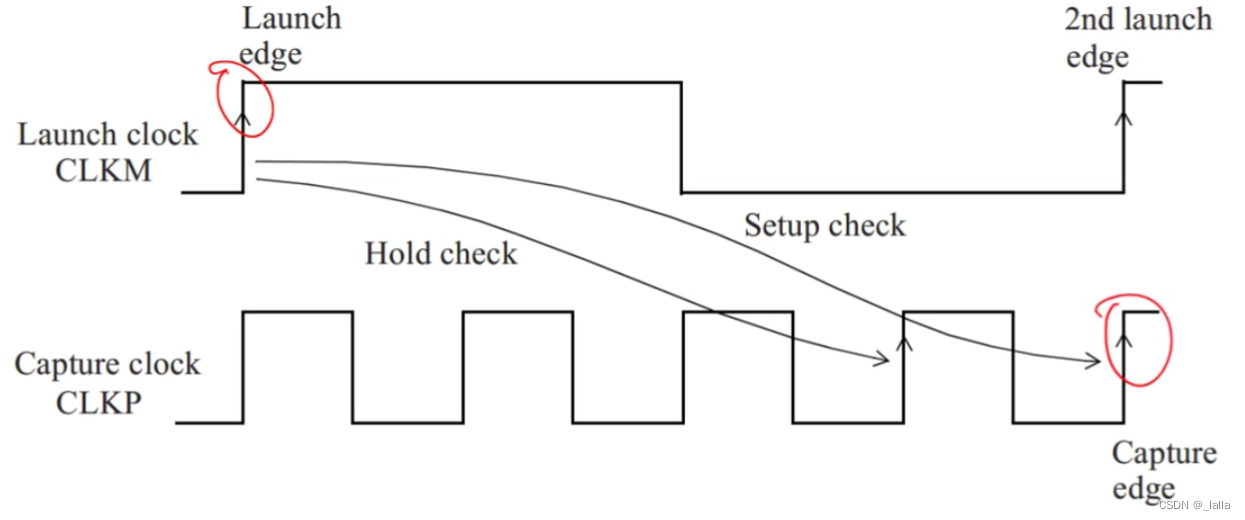

1、慢时钟域到快时钟域

在快时钟域的第一个上升沿检查是最为严格的

create_clock -name CLKM -period 20 -waveform {0 10} [get_ports CLKM]

create_clock -name CLKP -period 5 -waveform {0 2.5} [get_ports CLKP]

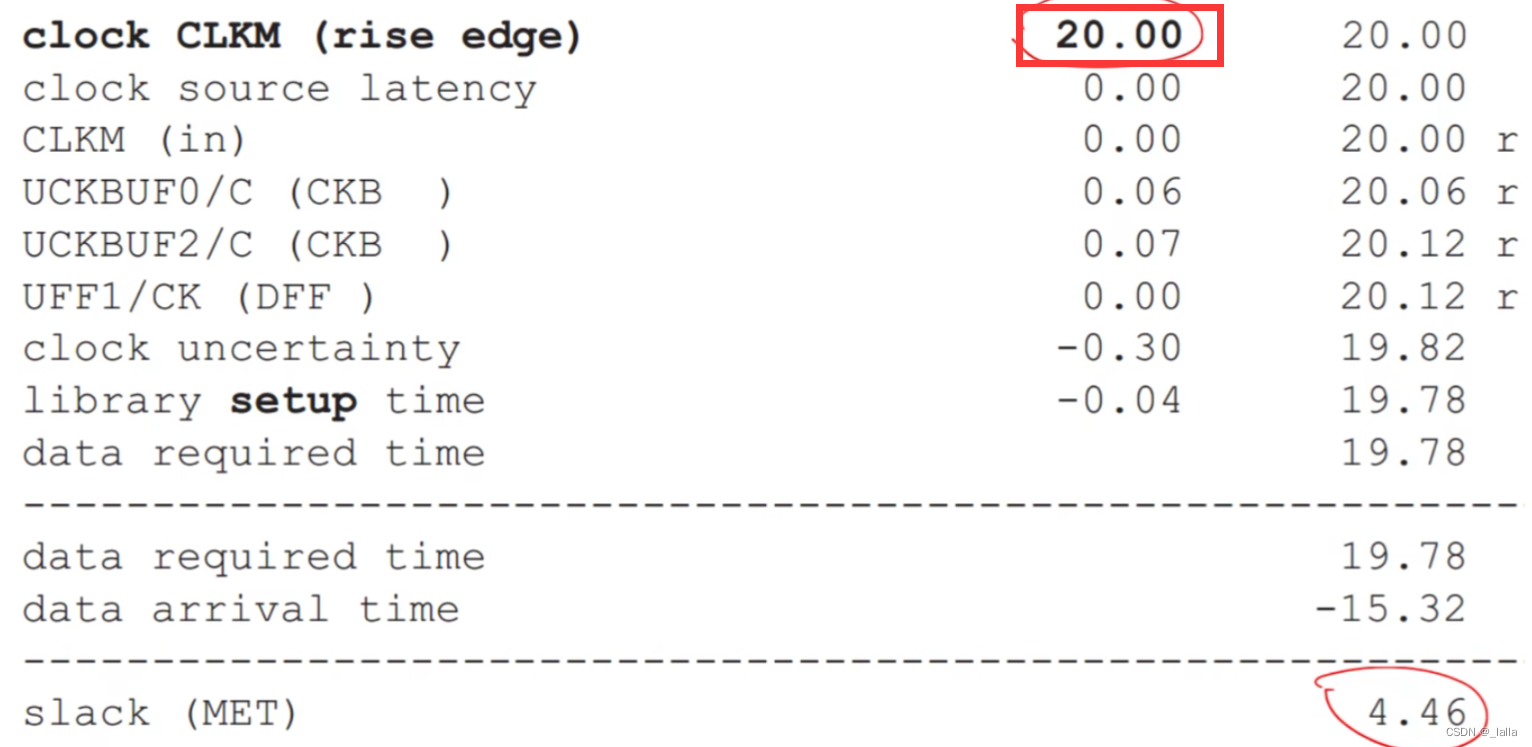

1.1 建立时间检查

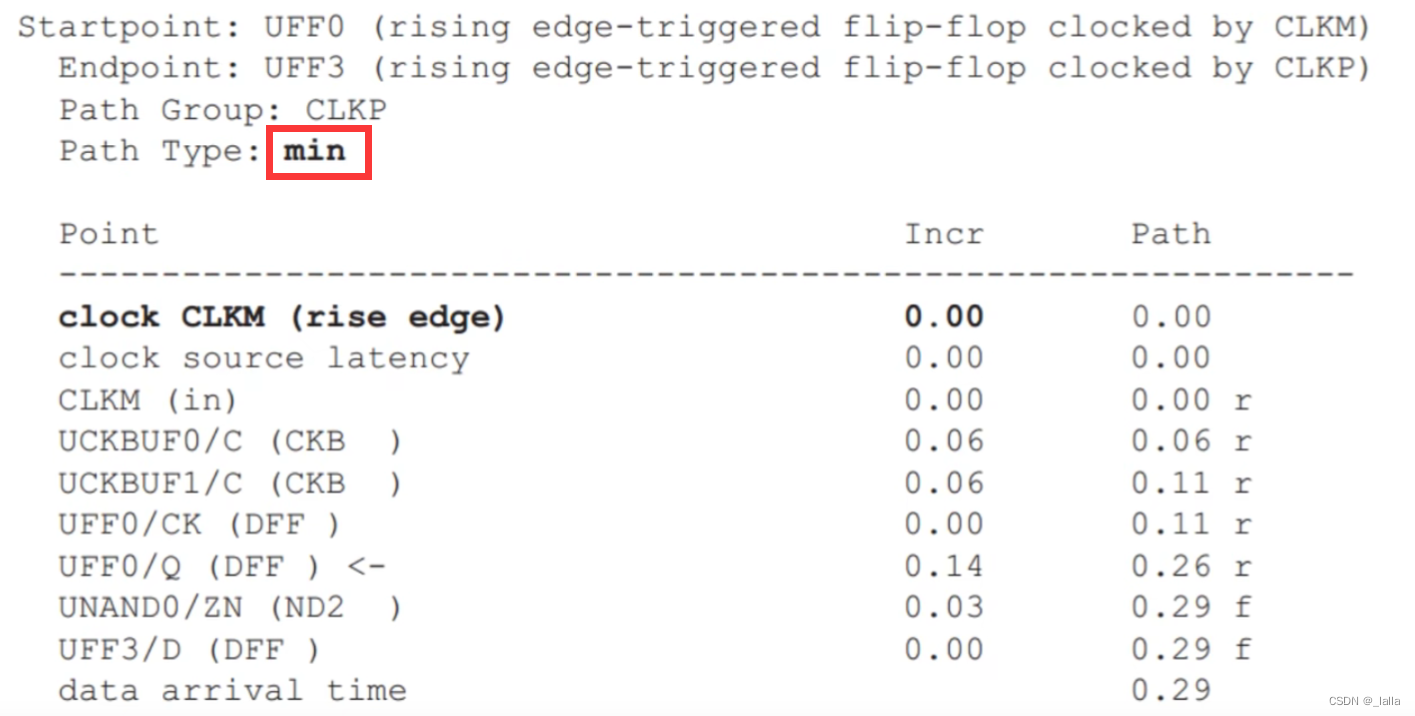

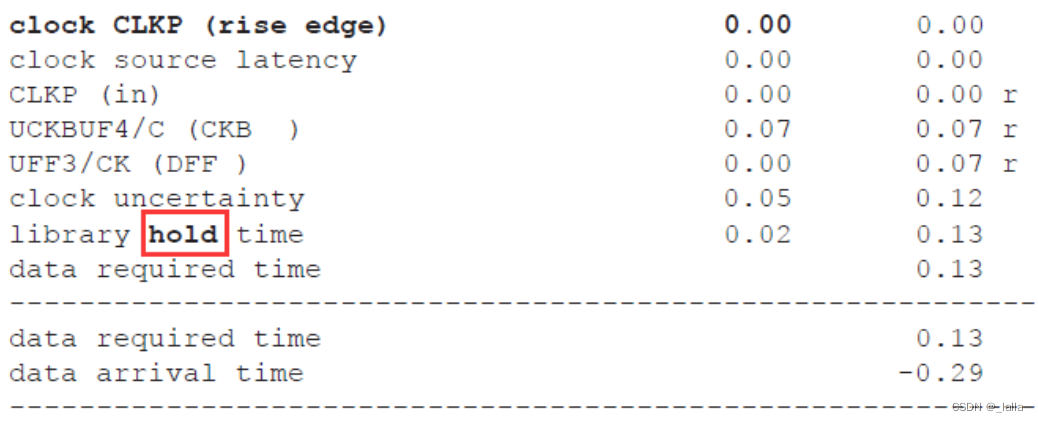

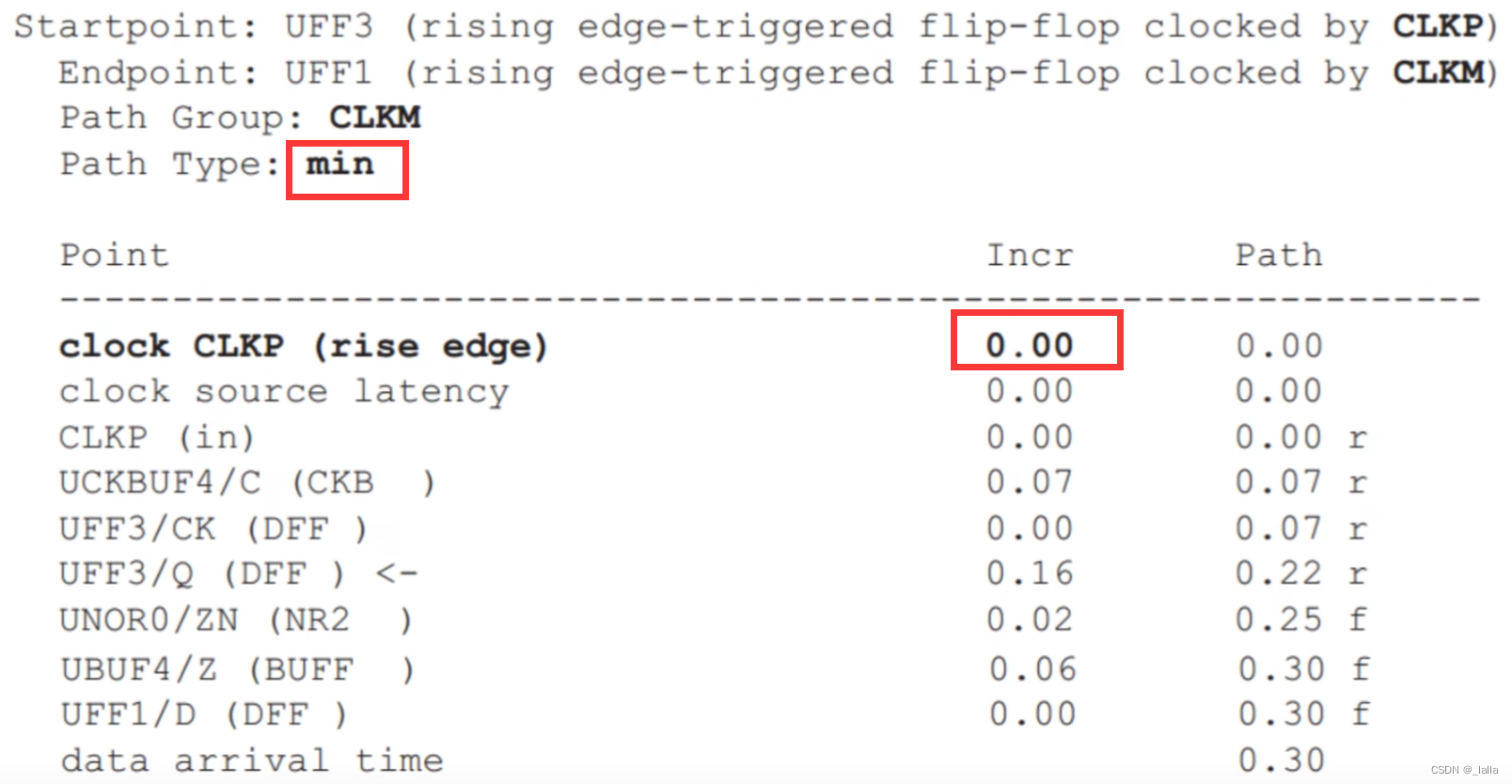

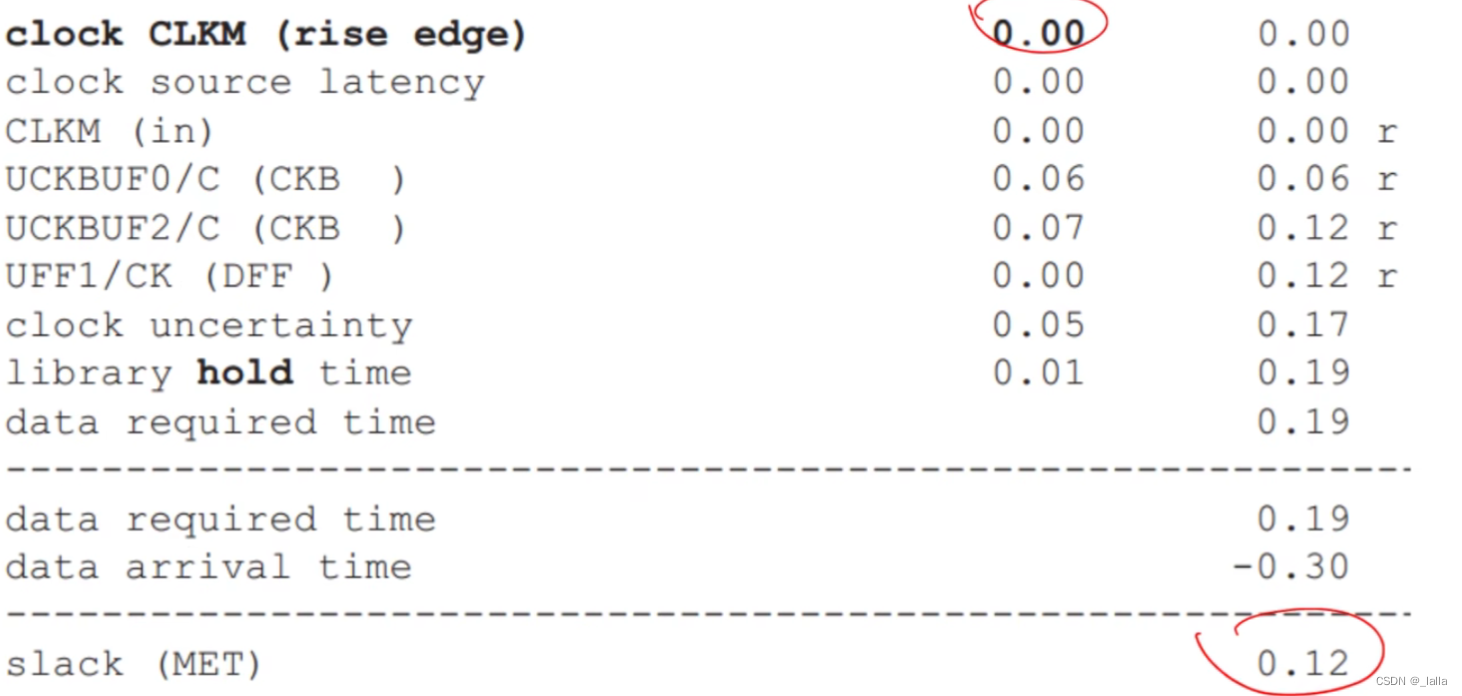

1.2 保持时间检查

1.3 多周期检查

-end:指定了多周期4是用于终点(endpoint)或捕获时钟的

在快时钟的第四个周期检查的好处:刚好是慢时钟的第一个周期,数据稳定了

set_multicycle_path 4 -setup -from [get_clocks CLKM] -to [get_clocks CLKP] -endset_multicycle_path 3 -hold -from [get_clocks CLKM] -to [get_clocks CLKP] -end //把hold时间检查,挪到前面,在0ns检查

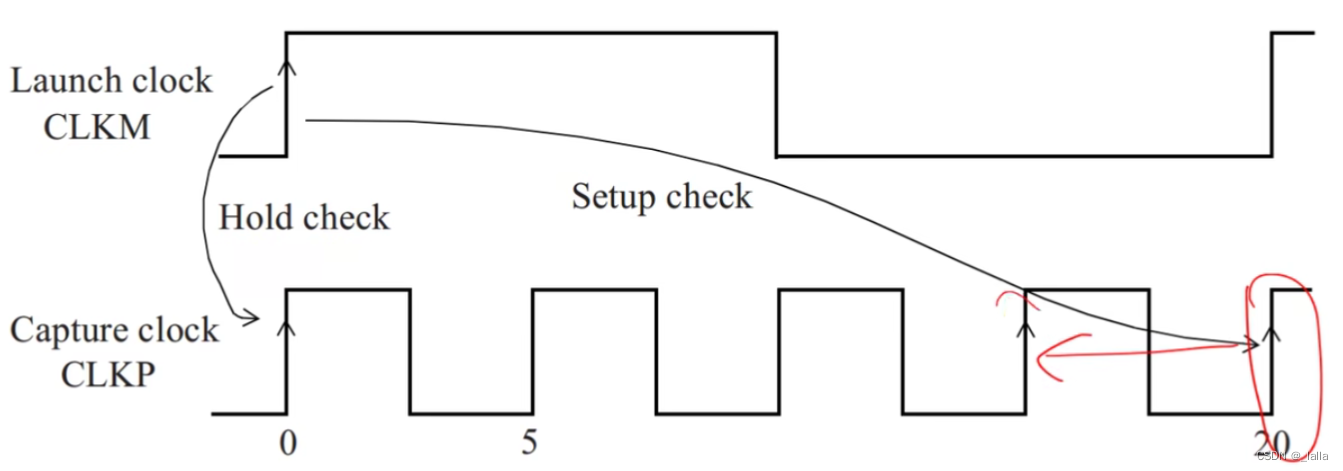

2、快时钟域到慢时钟域

2.1 建立时间检查

从setup4时钟沿发送数据,开始检查,是最严格的,留给组合逻辑的时间最短

2.2 保持时间检查

2.3 合理的约束

-start:针对的是起点的时钟

由于前面对建立时间的约束太严格了,所以稍微放宽松些

set_multicycle_path 2 -setup -from [get_clocks CLKP] -to [get_clocks CLKM] -start

set_multicycle_path 1 -hold -from [get_clocks CLKP] -to [get_clocks CLKM] -start

3、总结

- end和start选项:-start指作用在前面的时钟,-end是后面

- 要确定想要检查的周期边沿,hold是在setup的基础上向前移动一个周期

- 和上一节讲的特殊路径检查中多周期路径检查的区别:虽然都用到了

set_multicycle_path来约束路径,但是前者是同一个时钟,只是组合逻辑消耗了多个周期;这里是两个时钟频率不同造成的多周期差异,是不同的时钟

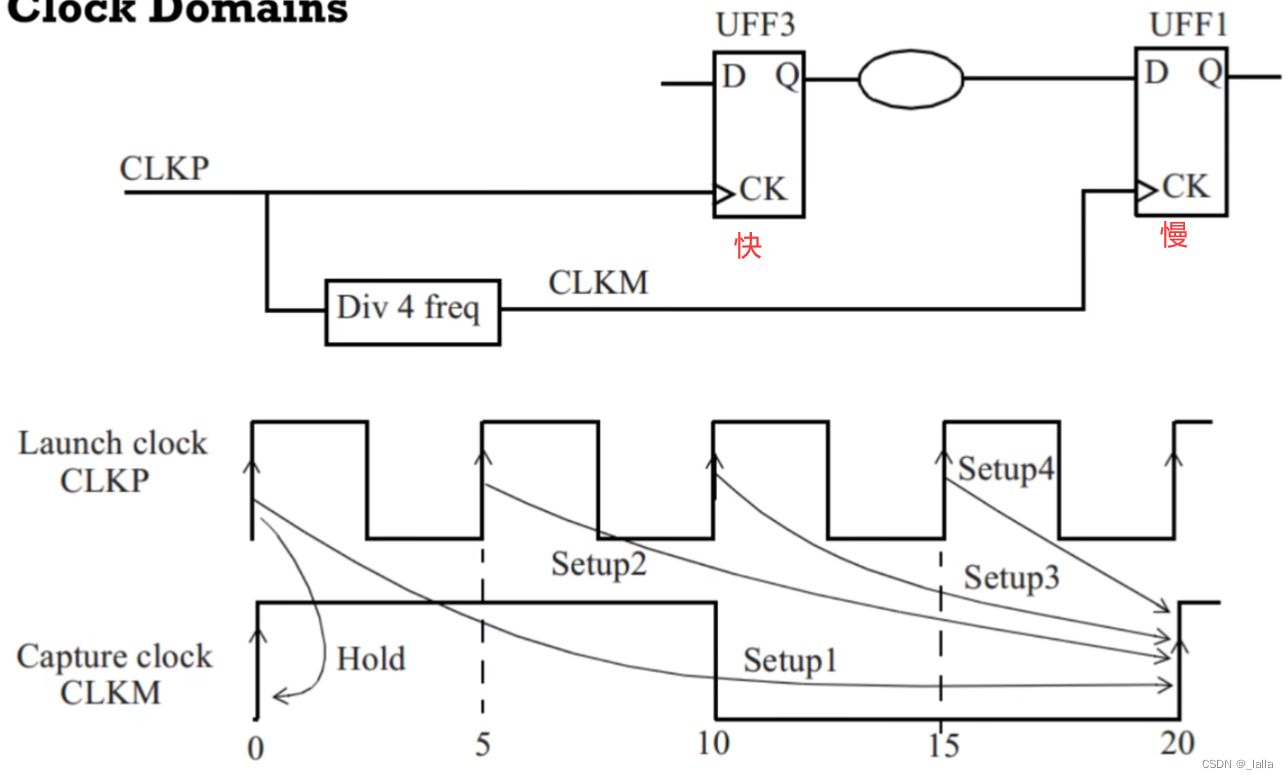

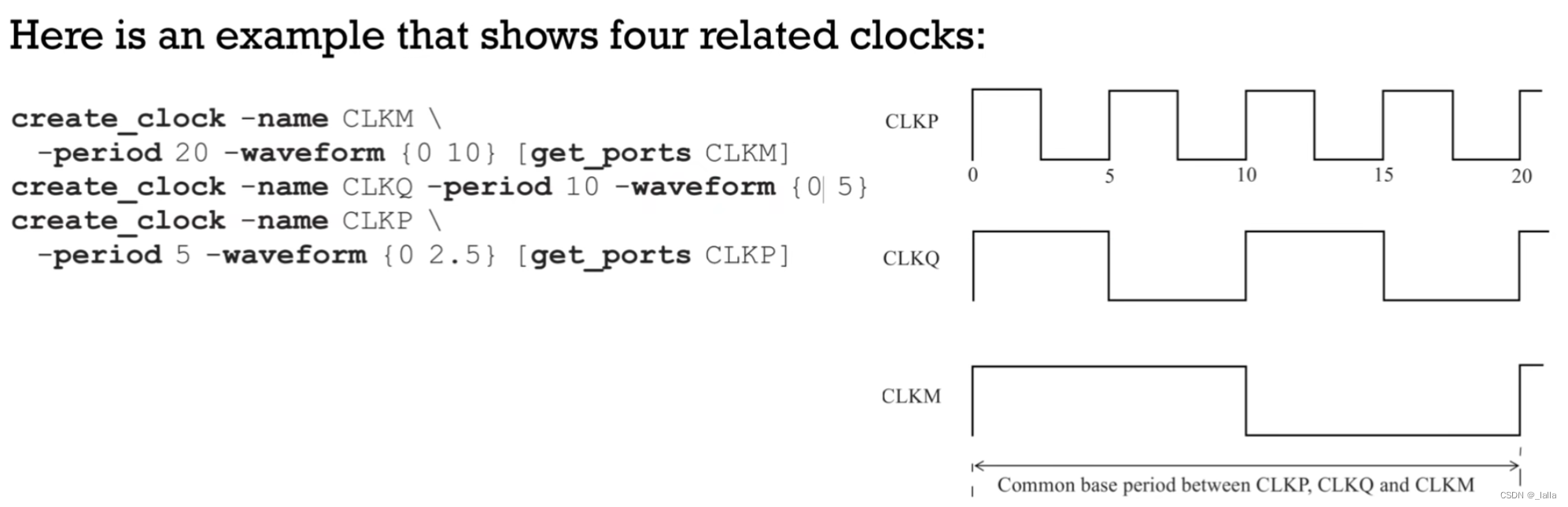

二、多时钟

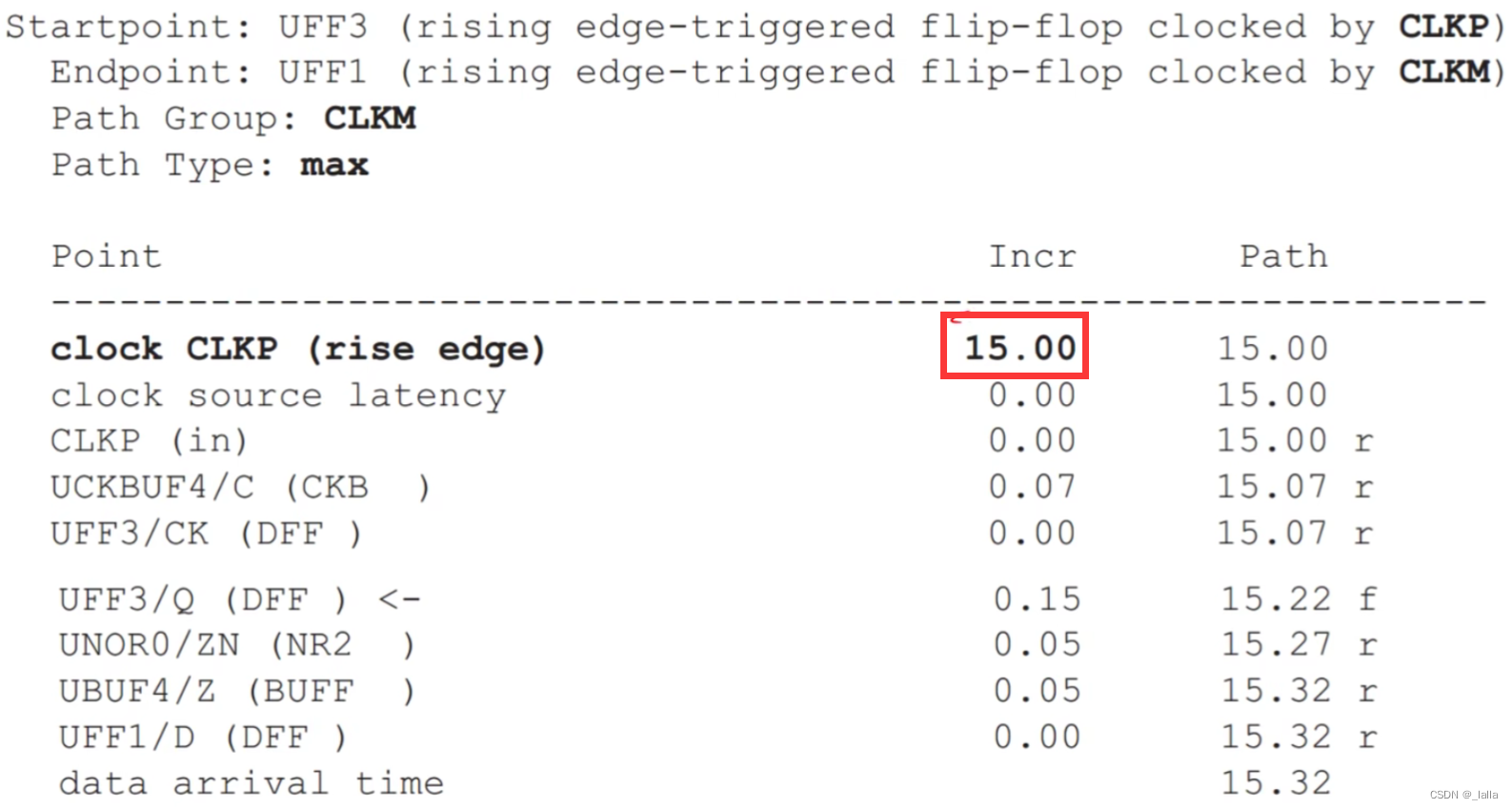

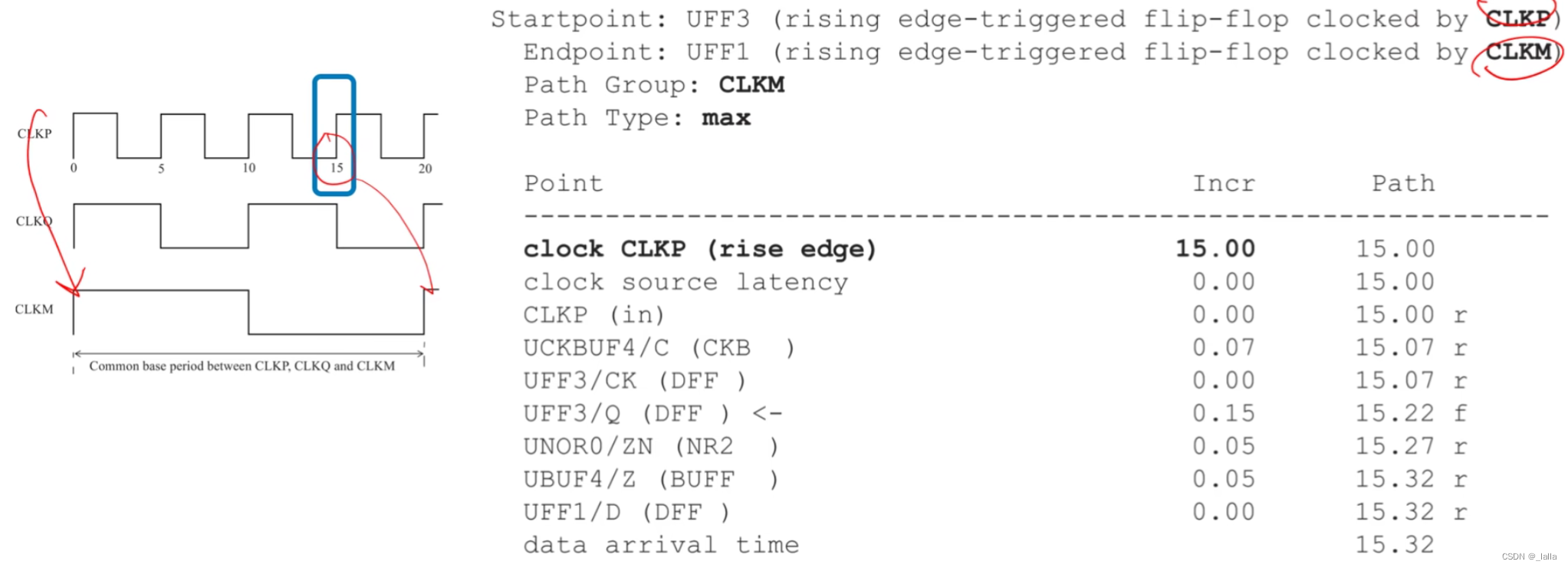

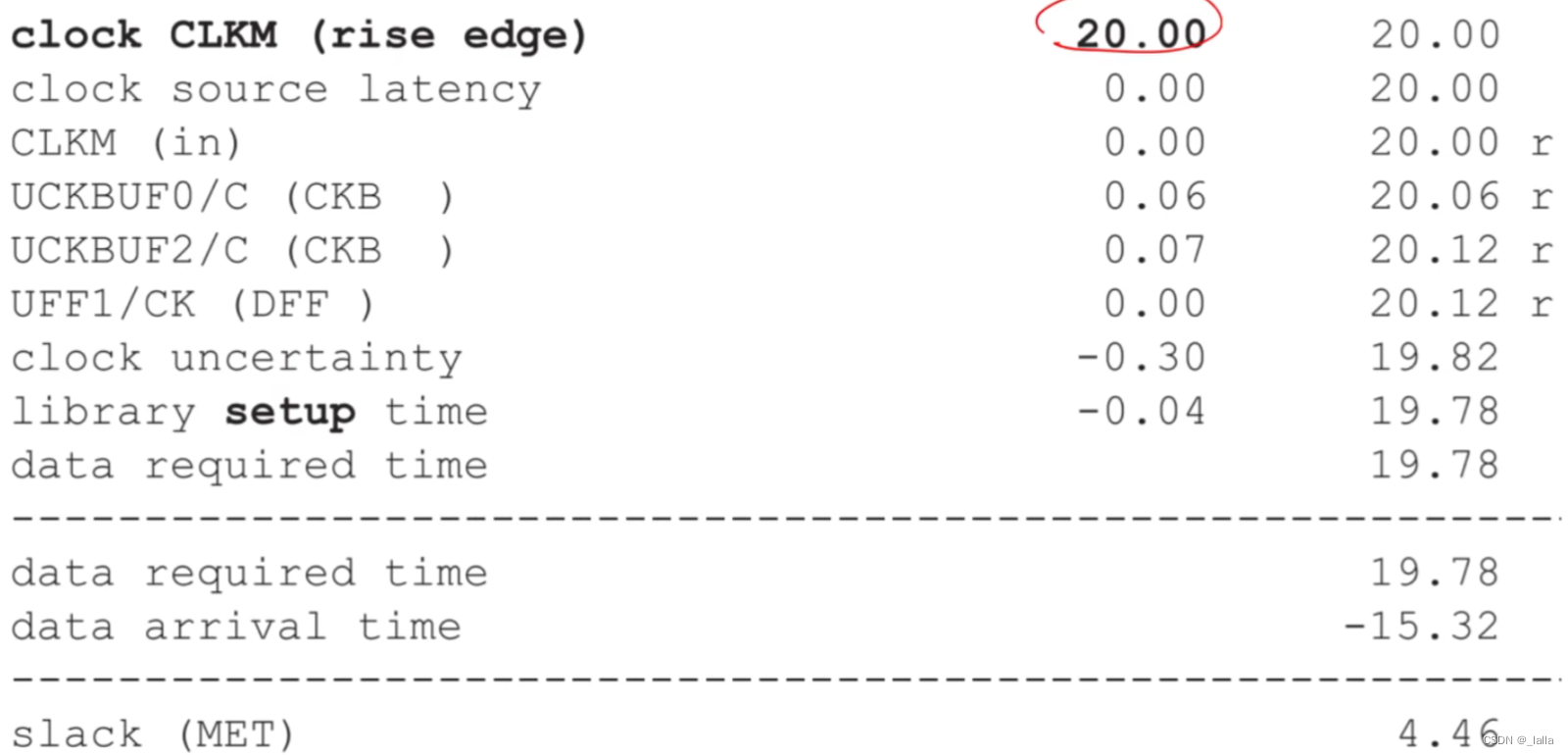

1、整数倍关系

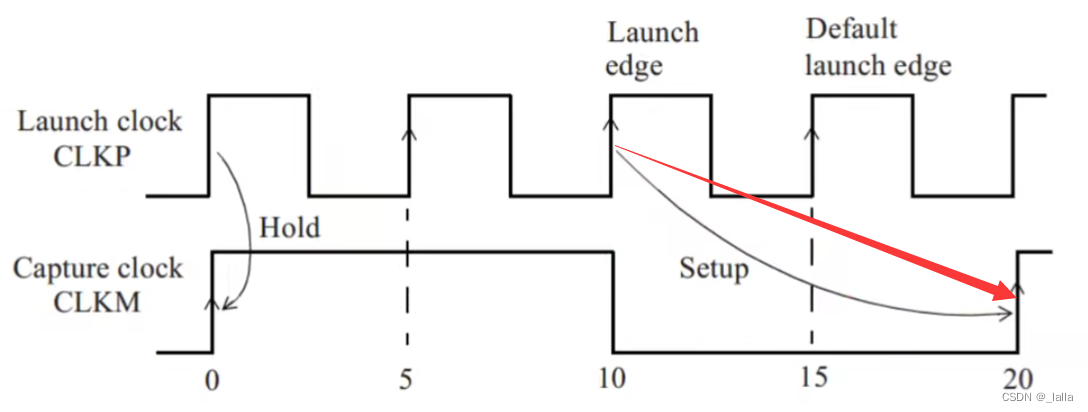

多个时钟,找最小公倍数的部分,下面就是20ns

最严格的检查就是在15ns开始

hold time则是从0开始检查

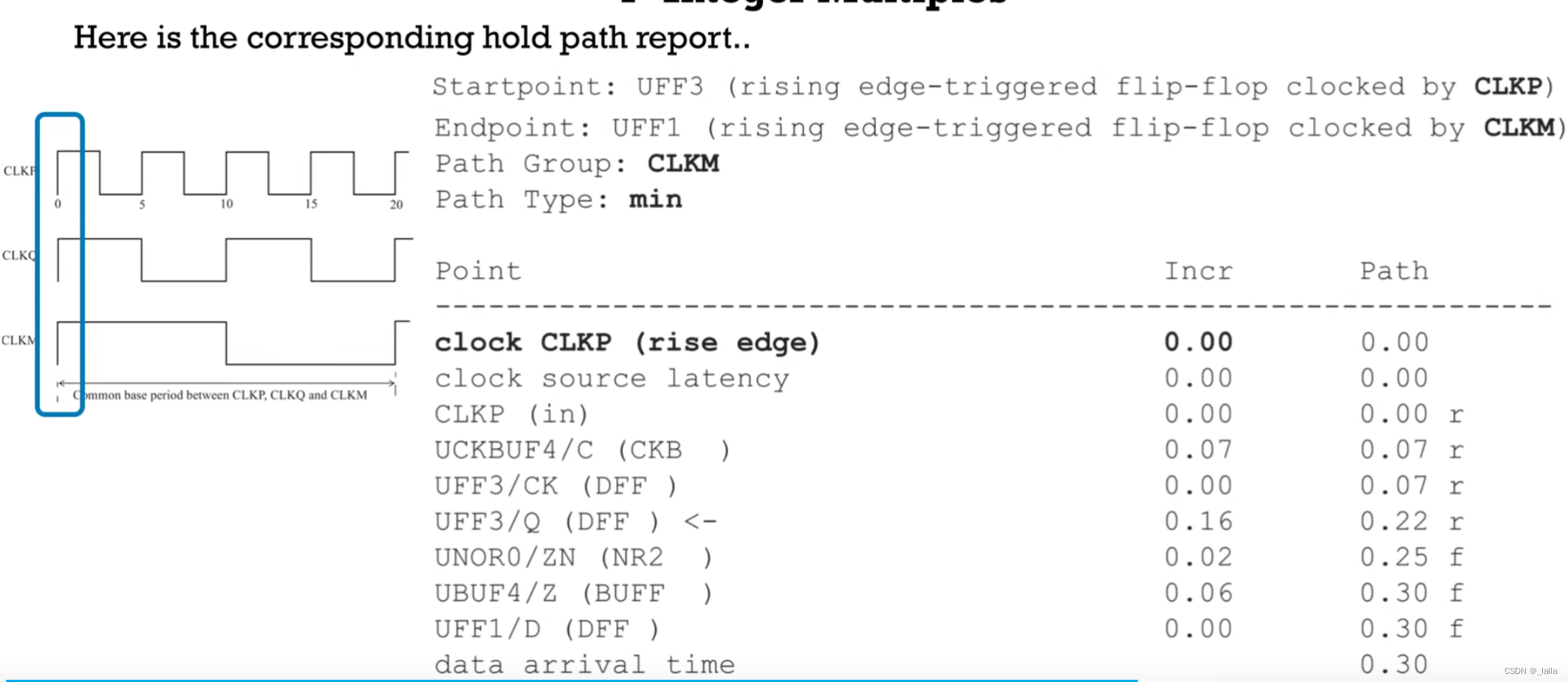

2、非整数倍关系

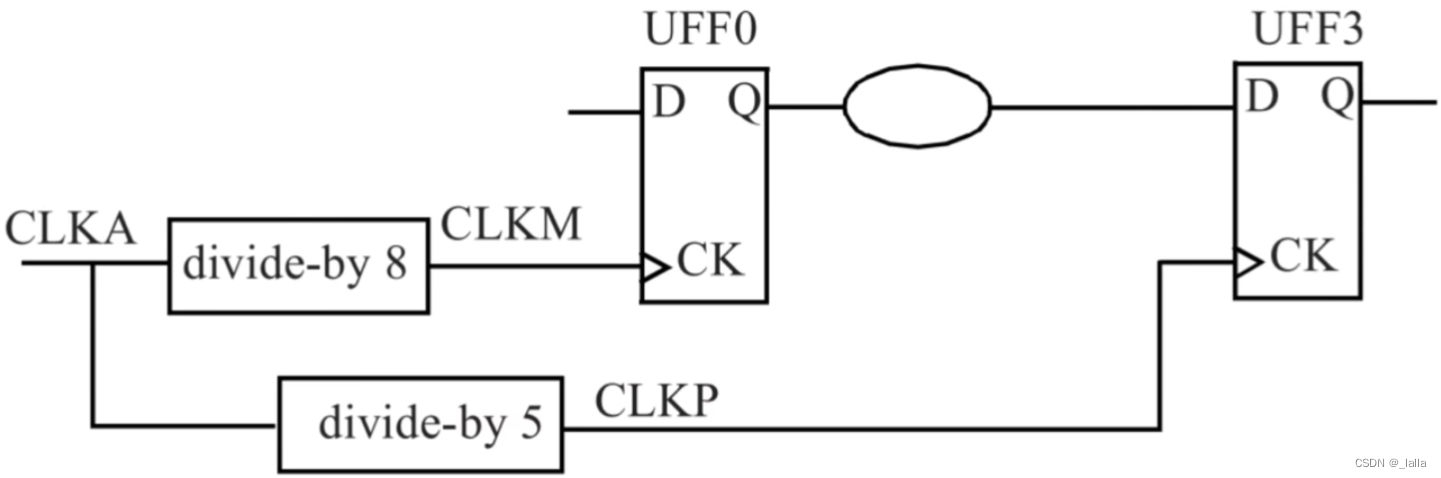

找最小公倍数40ns

create_clock -name CLKM -period 8 -waveform {0 4} [get_ports CLKM]

create_clock -name CLKQ -period 10 -waveform {0 5}

create_clock -name CLKP -period 5 -waveform {0 2.5} [get_ports CLKP]

从CLKM到CLKP:

- 24ns发送,25ns接收是最严格的,如果这种情况都能满足时序要求,说明其他情况也可以。

- 保持时间依旧是0ns时刻开始检查。

从CLKP到CLKM:

- 15ns到16ns去检查建立时间

- hold从0开始检查

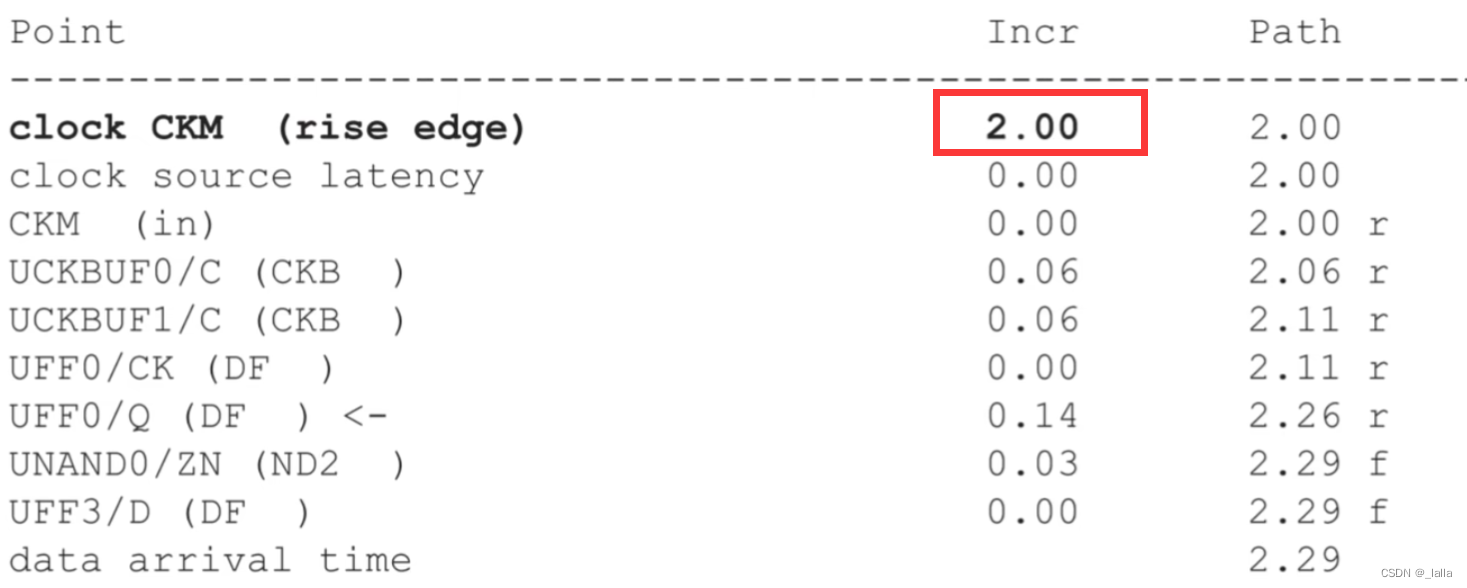

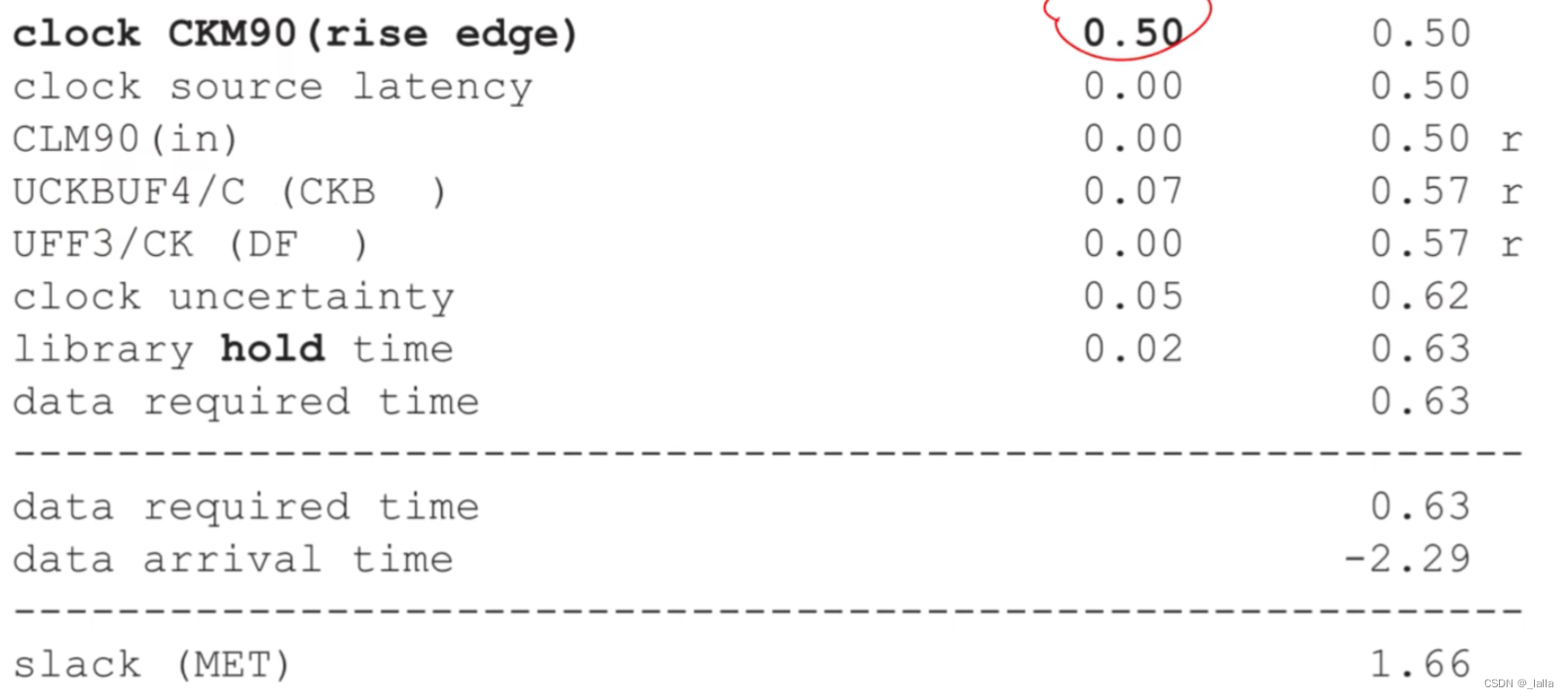

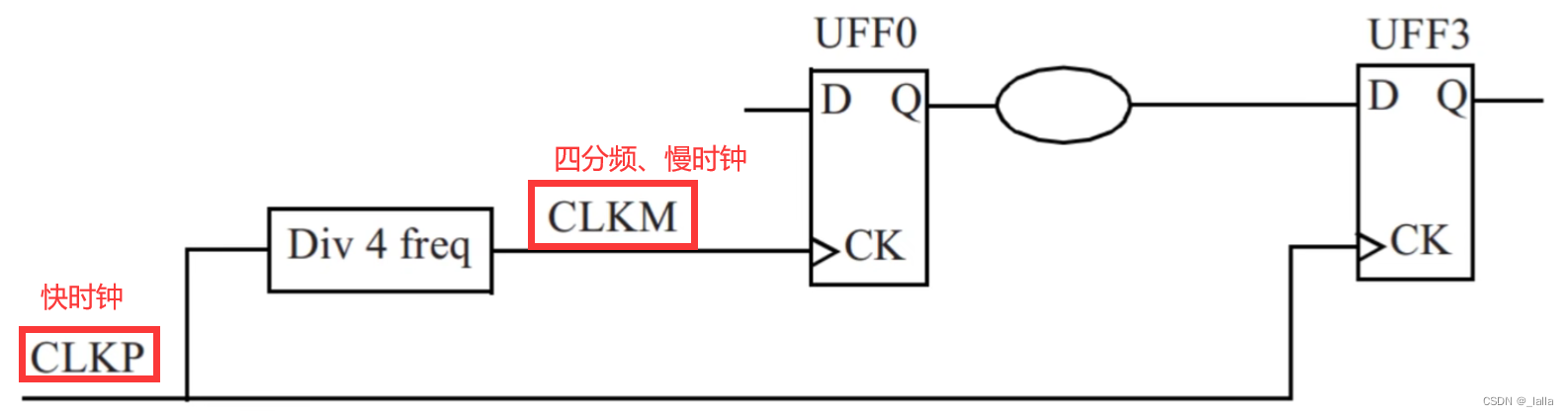

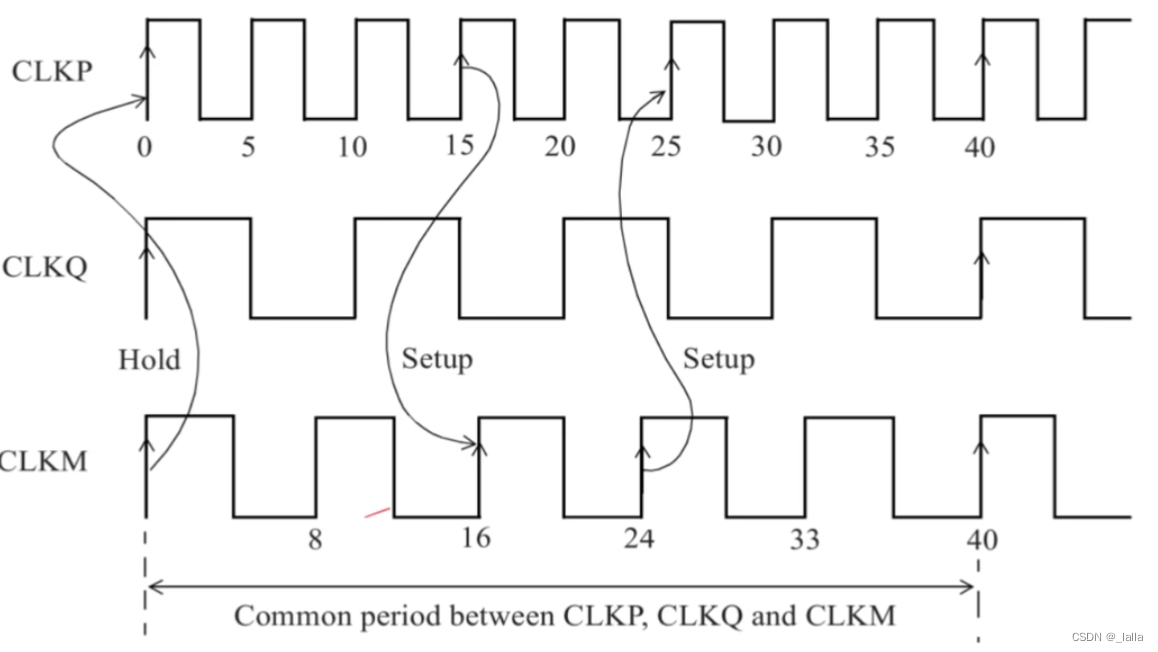

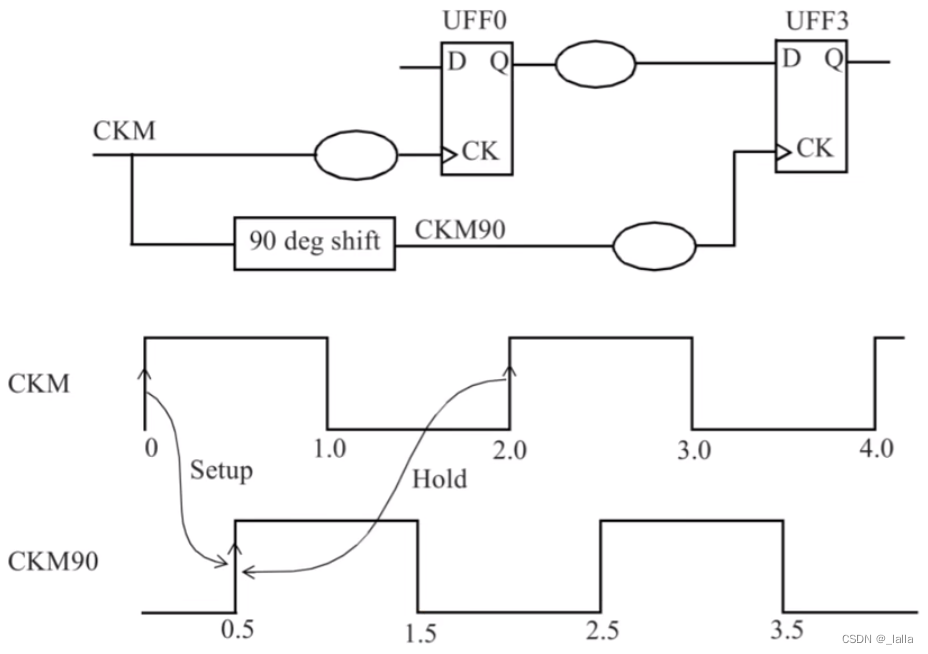

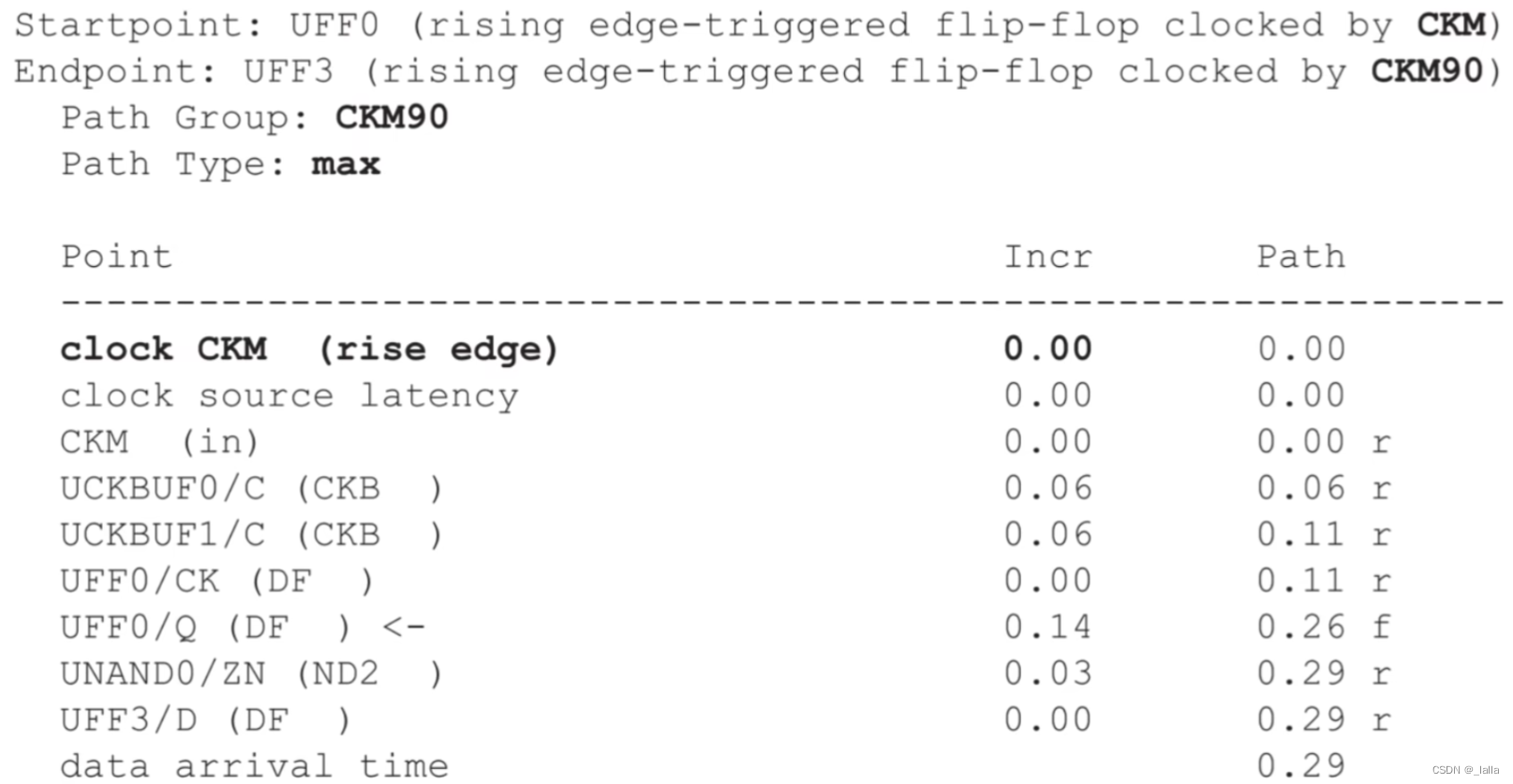

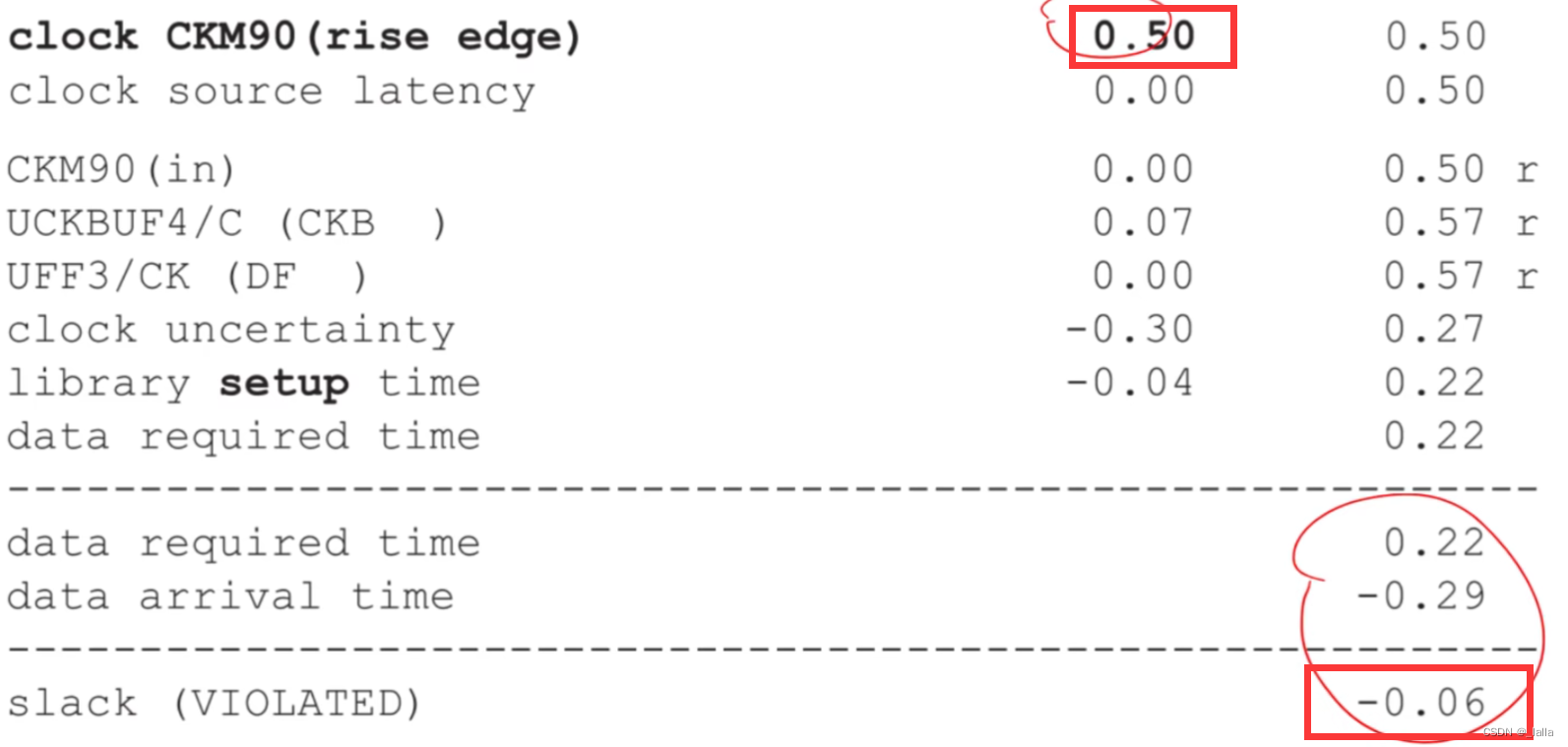

三、相位移动

create_clock -period 2.0 -waveform {0 1.0} [get_ports CKM]

create_clock -period 2.0 -waveform {0.5 1.5} [get_ports CKM90]

这种情况下,只有1/4个周期,常常难以满足建立时间要求

0开始,0.5ns检查

但是对于保持时间,有点类似前面的半周期路径,因此可以很容易满足

2ns开始,0.5ns检查