|

一、产品概述

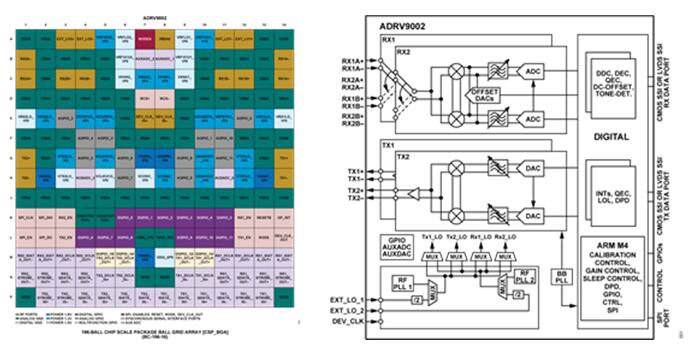

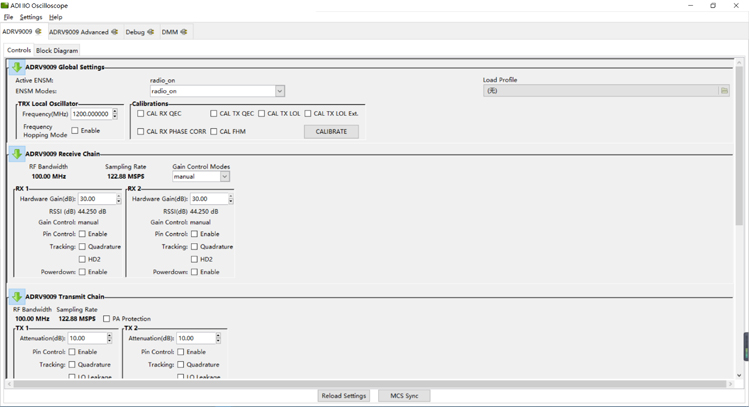

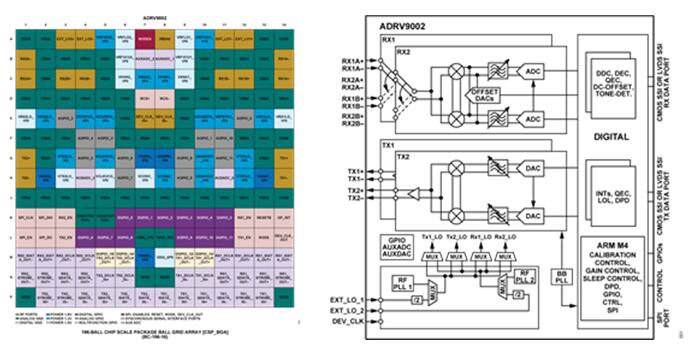

ADRV9002 是一款高性能、高线性度、高动态范围收发器,旨在针对性能与功耗系统进行优化。该设备是可配置的,非常适合要求苛刻、低功耗、便携式和电池供电的设备。ADRV9002 的工作频率为 30 MHz 至 6000 MHz,涵盖 UHF、VHF、工业、科学和医疗 (ISM) 频段、窄带 (kHz) 的蜂窝频段以及高达 40 MHz 的宽带操作。 ADRV9002 能够同时进行 TDD 和 FDD 操作。

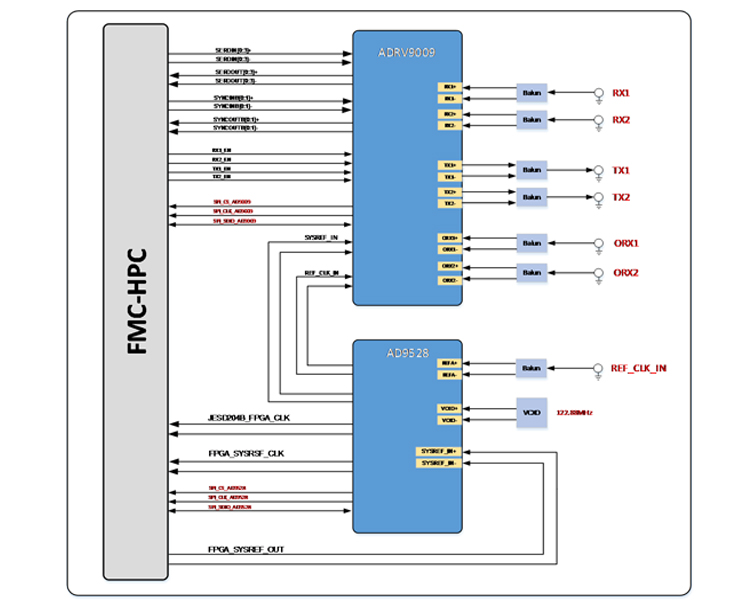

收发器包括直接转换信号路径,具有先进的噪声指数和线性度。每个完整的接收器和变送器子系统都包括直流失调矫正、正交误差校正 (QEC) 以及可编程数字滤波器,因此数字基带中不再需要这些功能。另外,它集成了辅助模数转换器 (ADC)、辅助数模转换器 (DAC) 以及通用输入/输出 (GPIO) 等若干辅助功能,因而可提供额外的监测和控制能力。

完全集成的锁相环 (PLL) 为变送器、接收器和时钟部分提供高性能、低功耗小数 N 频率合成。精心选用的设计和布局技术提供了高性能个人射频应用所需要的隔离。

其中集成了全部压控振荡器 (VCO) 和环路滤波器元件,从而尽可能减少外部元件数量。本地振荡器 (LO) 具有灵活的配置选项,并包括快速锁定模式。

该收发器具有低功耗睡眠和监控模式,可在监控通信的同时,节省功耗并延长便携式设备的电池寿命。

完全集成的低功耗数字预失真 (DPD) 针对窄带和宽带信号进行了优化,并实现了高效功率放大器的线性化。

ADRV9002 的内核可以直接由 1.0 V、1.3 V 和 1.8 V 稳压器供电,并通过标准 4 线串行端口进行控制。其他电源用来提供正确的数字接口电平,并优化接收器、变送器和辅助转换器性能。

使用可配置的 CMOS 或低电压差分信号 (LVDS) 串行同步接口 (SSI) 选项,可支持高数据速率和低数据速率接口。

二、优势和特点

• 2 × 2 高度集成的收发器

• 频率范围为 30 MHz 至 6000 MHz

• 变送器和接收器带宽为 12 kHz 至 40 MHz

• 两个完全集成的小数 N 射频频率合成器

• LVDS 和 CMOS 同步串行数据接口选项

• 低功耗监控器和休眠模式

• 多芯片同步功能

• 快速跳频

• 动态配置文件切换,可实现动态数据速率和采样率

• 完全集成的 DPD,适用于窄带和宽带波形

• 可通过 4 线 SPI 完全编程

• 12 mm × 12 mm、196 球 CSP_BGA

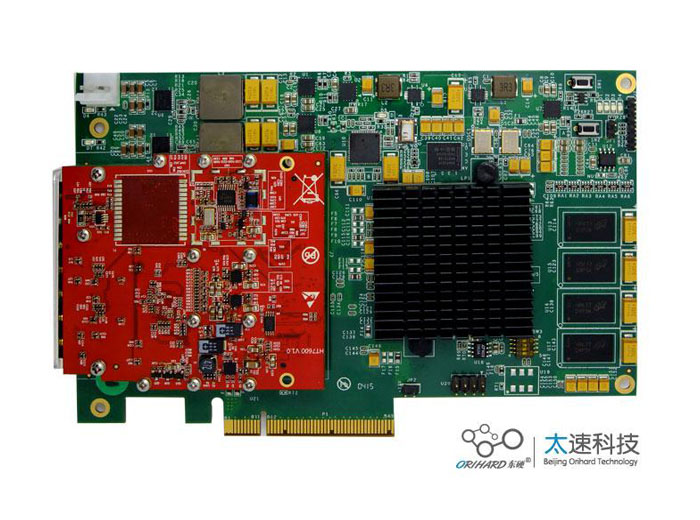

• 通过FMC连接器连接FPGA母板(ZC706和ZCU102)

• 采用单个FMC连接器供电

• 包括原理图、布局、BOM、HDL、驱动程序和应用软件

三、产品应用

• 关键任务通信

• 甚高频 (VHF)、超高频 (UHF),以及蜂窝到 6 GHz

• 时分双工 (TDD) 和频分双工 (FDD) 应用

|