Verilog学习笔记1——关键词、运算符、数据类型、function/task、initial/always、generate

文章目录

前言

2023.4.4

2023.4.7 补充综合和不可综合的关键词

一、关键词

module/endmodule

input/output/inout

parameter

wire/reg

always/assign

begin/end

posedge/negedge

case/default/endcase

if/esle

for

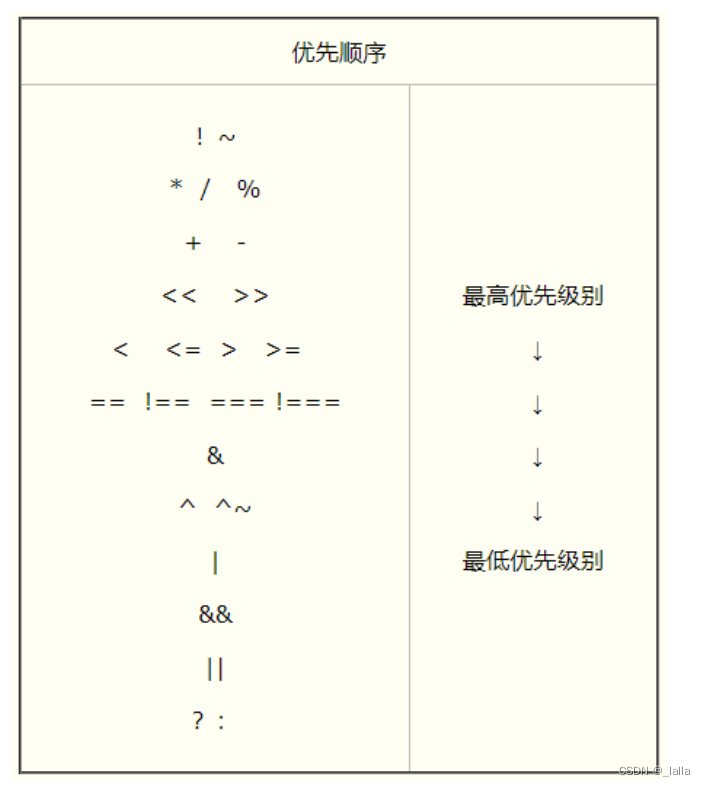

二、运算符

位运算符和缩位运算符区别:缩位运算符结果为1bit,位运算符结果位数和操作数位数相同

三、数据类型

总共:19种

1、基本类型:reg、wire、integer、parameter

当信号没有定义类型时,缺省类型为wire,缺省值为高阻Z。

wire:常和assign用来描述组合逻辑,verilog中输入输出缺省类型为wire。

reg:寄存器数据类型,缺省值是未知的,无符号数,但reg可以是负数也可以是正数。

在表达式的操作数中被当作是无符号数,假如是4bit的-1,则在实际运算时是-1的补码,也就是+15。

在always块内的每一个信号都必须是reg类型。

integer:寄存器数据类型,有符号数,最小为32位,与宿主机的字的位数。

parameter:定义常量,用来提高代码的可读性和可维护性

- reg 型和 wire 型的区别:reg 型保持最后一次的赋值,而 wire 型则需要持续的驱动。

- reg, integer, real,time 都是寄存器数据类型,定义在 Verilog 中用来保存数值的变量,和实际的硬件电路中的寄存器有区别。

- reg、integer是可综合的,time(64位)不可综合,real(32位)由仿真器决定。

四、条件语句

1、条件语句必须在过程块中使用,其他地方不可以。

2、0、z、X都是假,只有1条件才为真

3、出现锁存器的情况:

- if else没有写完整

- always里面,如果给定条件下变量没有被赋值,这个变量将一直保持原来的值,就会生成锁存器

- 有else不一定没有锁存器,没有else也不一定有锁存器。

4、case语句如果情况完备,可以不写default

五、循环语句

1、for

for:for循环几次,就会把电路复制几次,循环次数越多,面积越大,综合越慢

2、generate

generate:生成可配置的、可综合的RTL设计结构。在elaboration阶段、仿真之前执行,必须保证generate的所有表达式都是常量

应用场景:

- 多次实例化某个模块

- 条件generate,if-generate或者case-generate

- 断言

module n_bit_xor

#(parameter SIZE = 16)

(input [SIZE-1:0] a,input [SIZE-1:0] b,output [SIZE-1:0] y

);genvar i;generatefor(i=0;i<SIZE;i=i+1)begin:label //这里一定要写模块名称,否则会报错xor u_xor(y[i], a[i], b[i]);//会实例化生成label[0].u_xor、label[1].u_xor、label[2].u_xor//实例化后的层次路径为n_bit_xor.label[0].u_xorendendgenerate

endmodule

六、function和task

| function | task |

|---|---|

| 只能用于组合逻辑 | 组合逻辑和时序逻辑都可以,但只有组合逻辑才能综合 |

| 可以有/无返回值,缺失则返回一位寄存器类型数据 | 无返回值 |

| 只能出现在过程块内,不能出现initial和always | |

| 至少有一个输入 | 多个输入/输出/双向端口 |

| 只能调用函数 | 可以调用函数/任务 |

| 不包含时间控制语句 | 可包含时延控制语句(不可综合) |

七、initial和always

1、initial和always相同点和区别

之前在SV语法的这篇文章里面有:传送门

initial:初始化仿真变量,作为电路的仿真信号来生成激励

always:边沿触发和电平触发,可综合成寄存器或者锁存器

2、always和assign语句区别

- assign语句赋值的信号类型为wire,always块里面是reg类型,但是不是真的寄存器,只有当always的触发条件为时钟上升沿,才会被综合为触发器

- 当仿真时,a=0,但是b是不定态。因为b的触发条件是always内的所有输入信号发生改变,才会变化,而1‘b0始终是不变的

assign a = 1'b0;always@(*)b = 1'b0;