AES算法中S盒的FPGA实现

AES算法中S盒的FPGA实现 I

语言 : verilog EDA

工具 : quartus

-

-

- AES算法中S盒的FPGA实现 I

- 一、S盒的简介

- 二、S盒的实现要求

- 三、S盒FPGA实现的具体方案

-

一、S盒的简介

在密码学中,S盒(Substitution-box)是对称密钥算法 ,执行置换计算的基本结构。S盒用在分组密码算法中,是唯一的非线性结构,其S盒的指标的好坏直接决定了密码算法的好坏。

二、S盒的实现要求

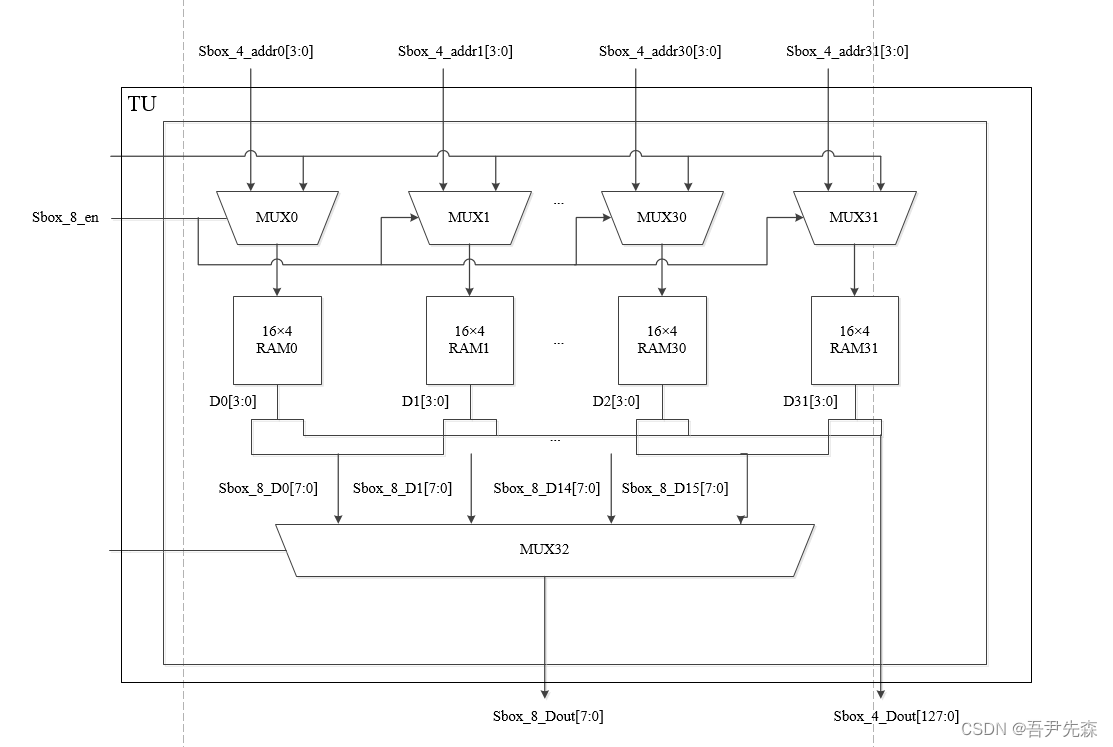

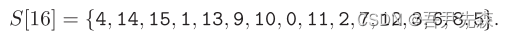

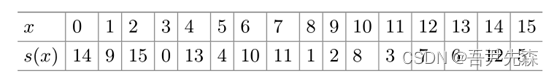

4×4的S-Box所占空间为64bit,对应于图中 RAM0~RAM31 这32个数据存储块。以上 32 个 S-Box 的总空间为 256 字节(=8×256bit),正好是一个8×8的S-Box 的所需空间。

图中与输入数据直接相连的 32 个 2 选 1 选择器主要负责选择输入数据的来源,由信号 Sbox_8_en 控制,当 Sbox_8_en使能时输入数据选择 Sbox_8_addr [3:0](Sbox_8_addr的低4位)的通道,不使能Sbox_8_en时输入数据选择Sbox_4_addr31[3:0]~ Sbox_4 addr0[3:0](共128位)的通道。Read_en 信号和 Write_en 信号则是分别用来控制 32 个 RAM 的数据读模式和数据写模式。每个 RAM 的输出分别标记位 D0[3:0]、D1[3:0]、…、D30[3:0]、D31[3:0],对应的输出数据 Sbox_4_Dout[127:0]是由以上32个半字节数据按照从高到低组合而成。而对于另一条路径对应的输出有16个数据:Sbox_8 D0[7:0] = {D0[3:0],D1[3:0]}、…、Sbox_8_D15[7:0] = {D30[3:0],D31[3:0]},这16个数据最终由Sbox_8_addr [7:4](Sbox_8 _addr 的高4位)控制一个16选 1 的选择器来进行选择,输出为Sbox_8_Dout[7:0]。

三、S盒FPGA实现的具体方案

具体实现的方案如下所示: