Candence PCB Si 仿真设计篇3:板级链路仿真

接上篇Candence PCB Si 仿真设计篇2;提示仿真链路中无VIA过孔仿真模型,可手动添加VIA过孔仿真模型;

1.添加过孔VIA仿真模型.

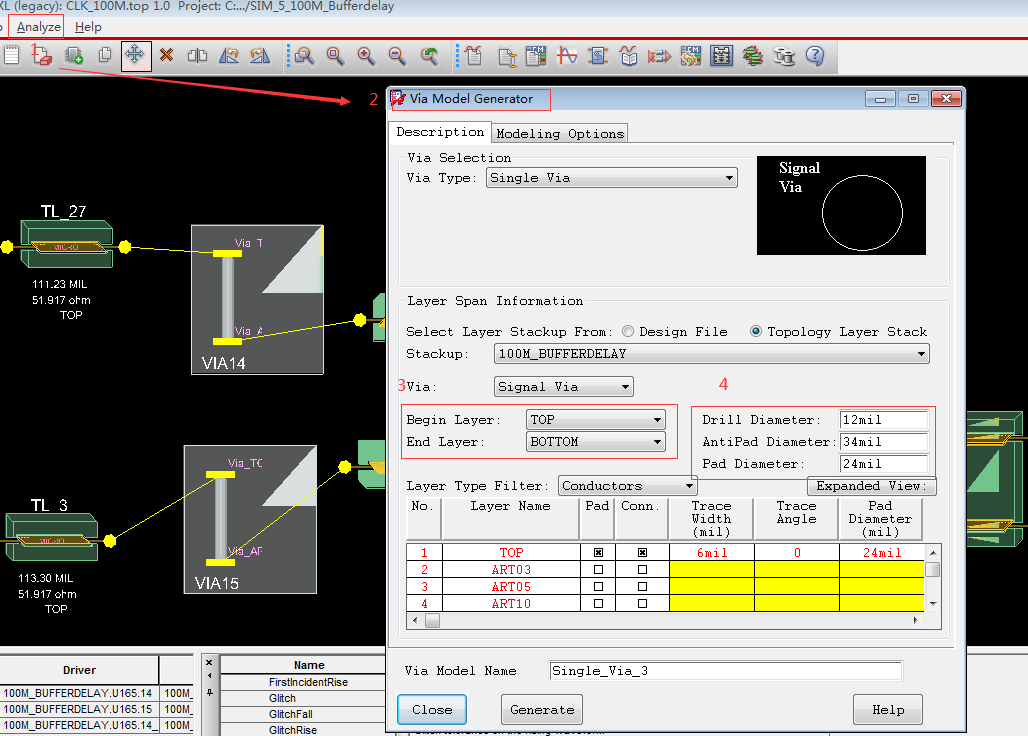

在SigXplorer PCB SI GXL界面中,菜单栏Analyze->Via Model Generator弹出设置VIA模型设置;

生成的VIA中可能需要设置过孔的起始层,过孔的大小类型,这个根据实际的类型设置参数,如下图所示:

这个步骤主要是新建过孔模型供仿真拓扑使用;

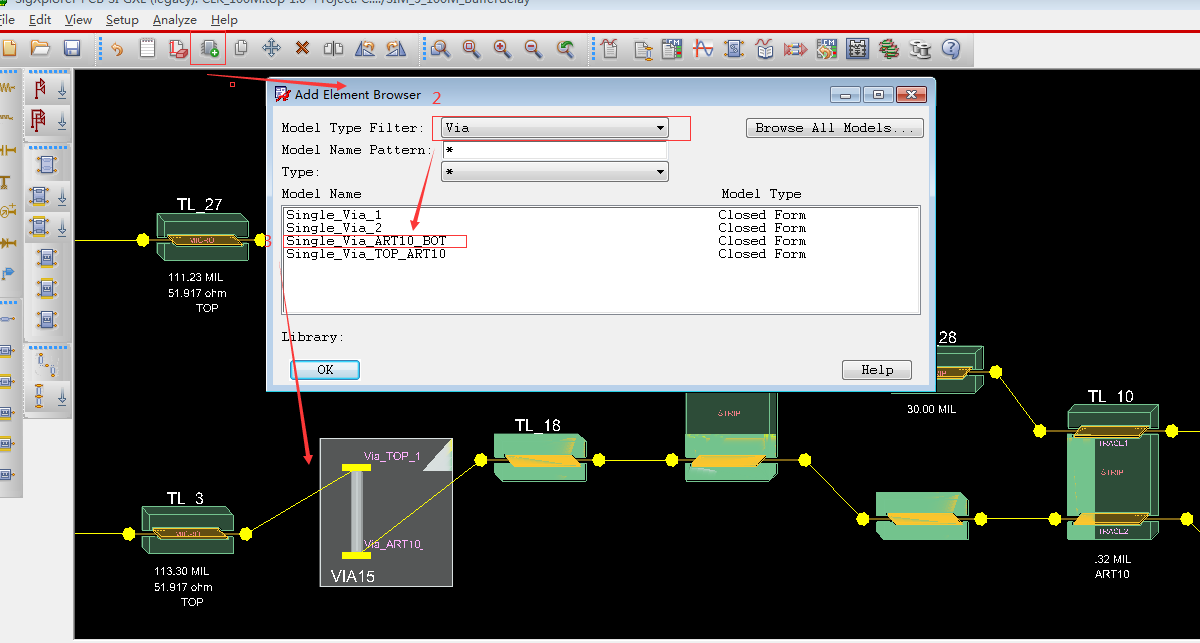

调用过孔模型的步骤如下图所示;将上一步生成的VIA模型依次替换掉原来的VIA即可。

2、仿真参数设置

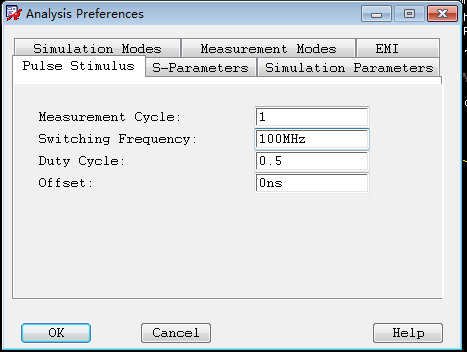

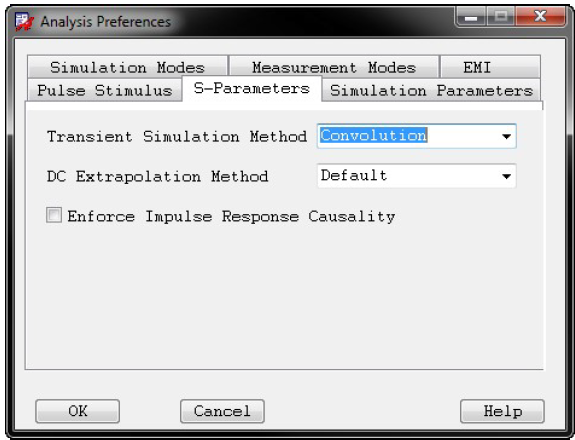

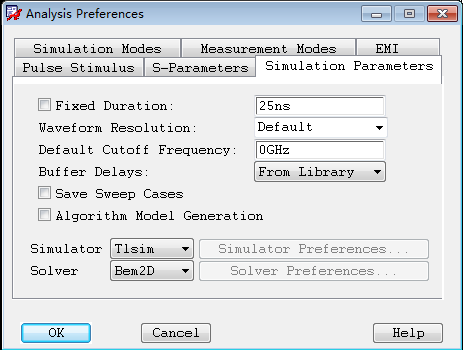

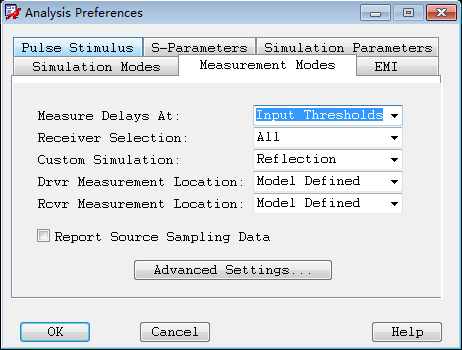

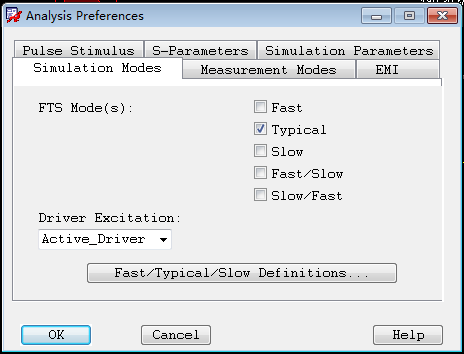

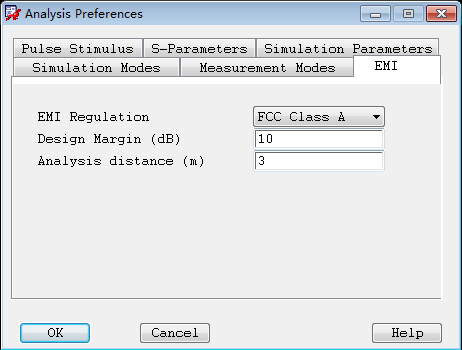

在SigXplorer PCB SI GXL界面中,菜单栏Analyze->Preferrence弹出仿真参数设置;设置内容和Allegro PCB SI中的同名窗口基本一致,如果在提取得到的拓扑文件中打开此窗口,会发现其中的参数值是从Allegro PCB SI传递过来的,不必再设置,

Pulse Stimulus栏 S-Parameters栏

Pulse Stimulus栏 S-Parameters栏

Simulation Paremeters栏 Measurement Modes栏

Simulation Modes栏 EMI栏

3.仿真激励设置

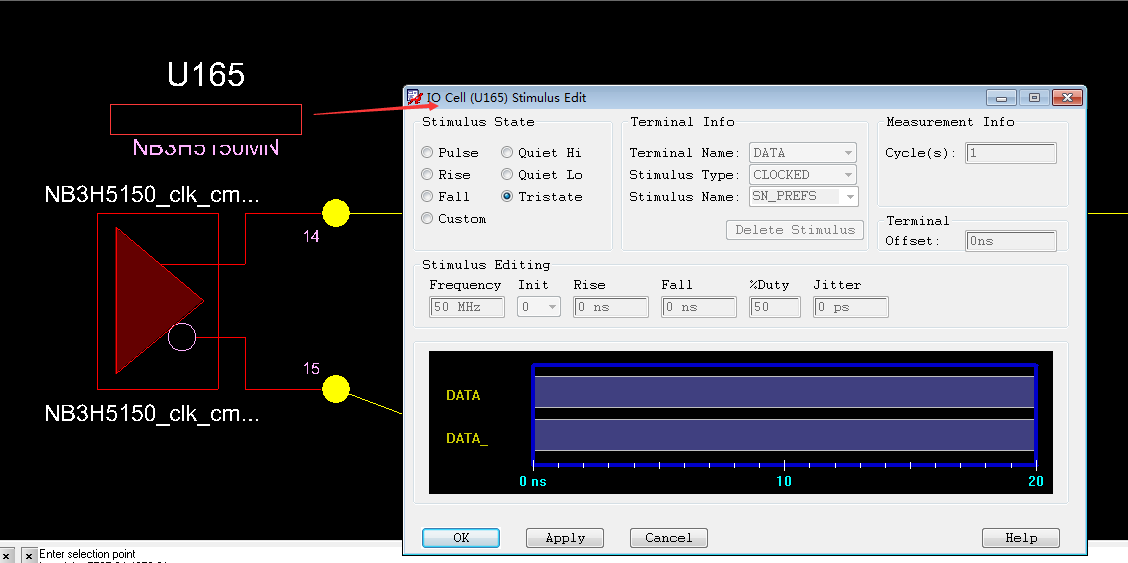

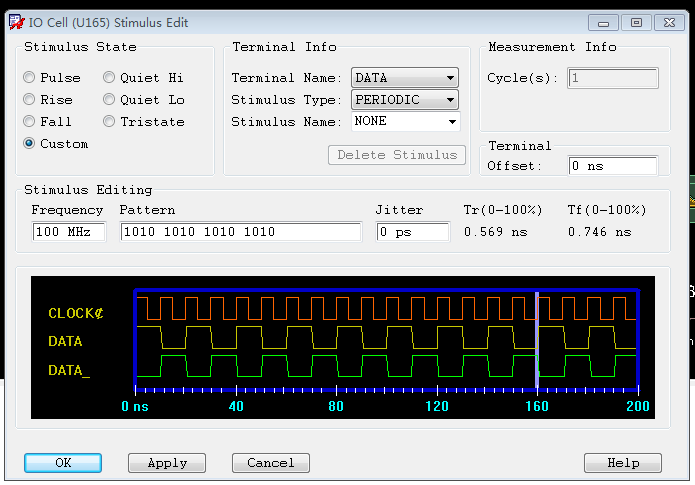

在SigXplorer PCB SI GXL界面中,点击驱动端缓冲器表征状态的字符,就会弹出IO Cell Stimulus Edit激励编辑窗口,激励的类型和简介如下图和下表所示:

说明一下IO Cell Stimulus Edit窗口的选项:

具体选择使用那种激励源进行测试,请根据实际的场景进行选择设置;

本案例激励源设置如下:

仿真类型主要包括以下4大类:

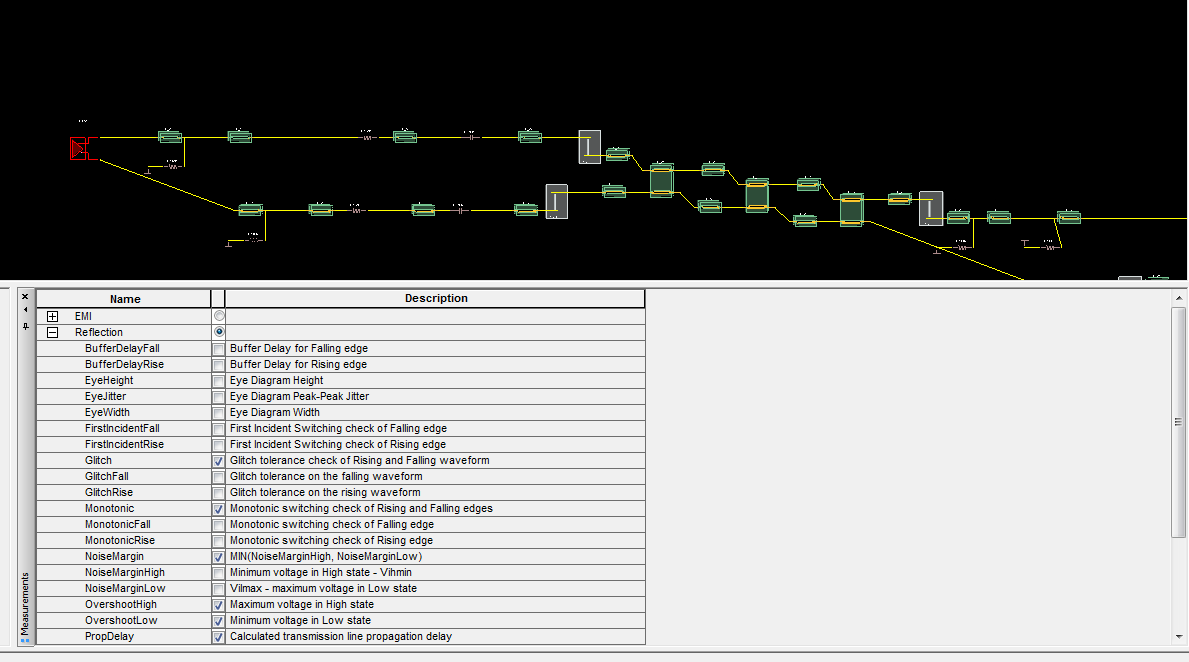

1、EMI仿真;2、Crosstalk(串扰)仿真;3、Reflection(反射仿真)4、Custom(自定义)

每次仿真只能选择一个大类下测量;

本案例选择Reflection大项大类以及其默认项如下:

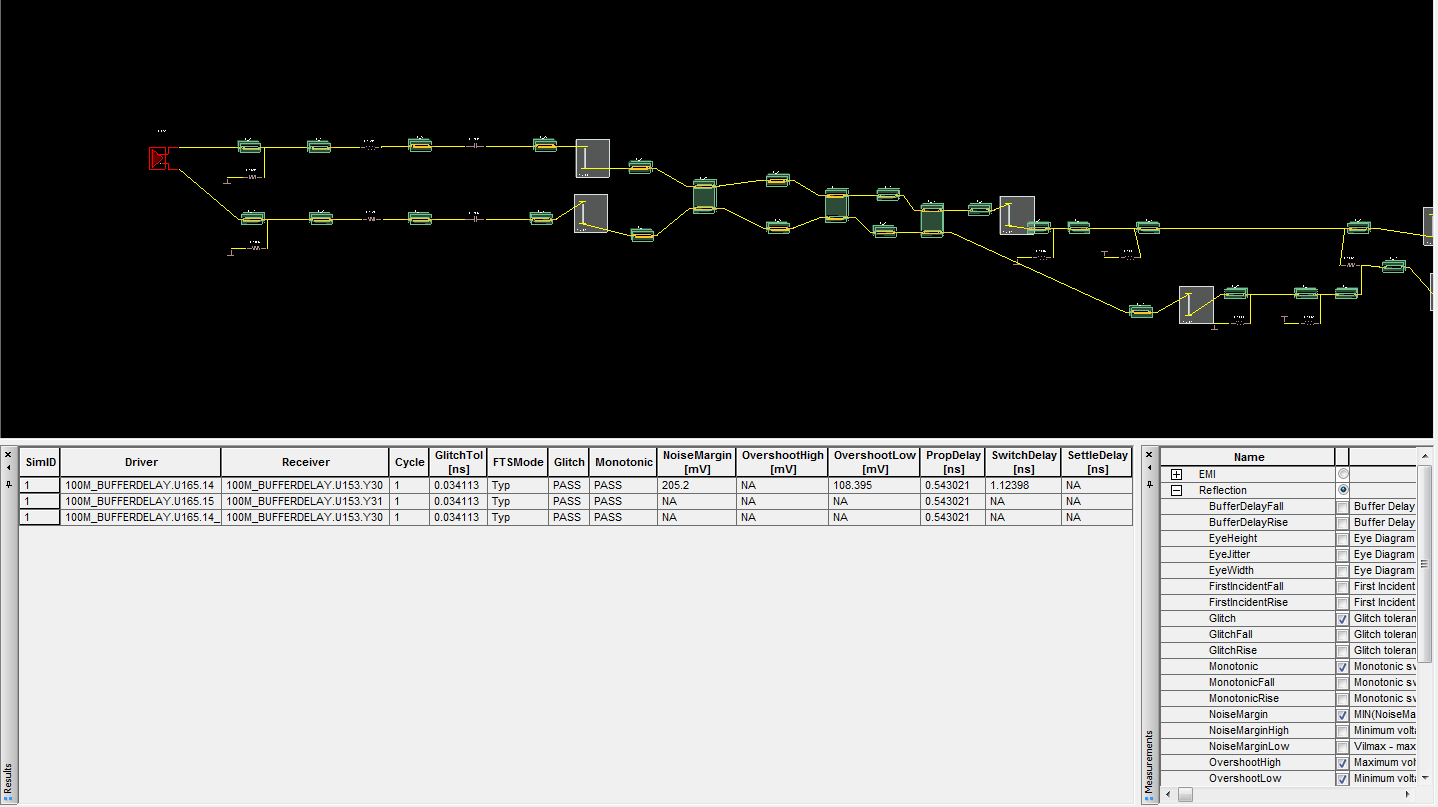

4.仿真结果分析

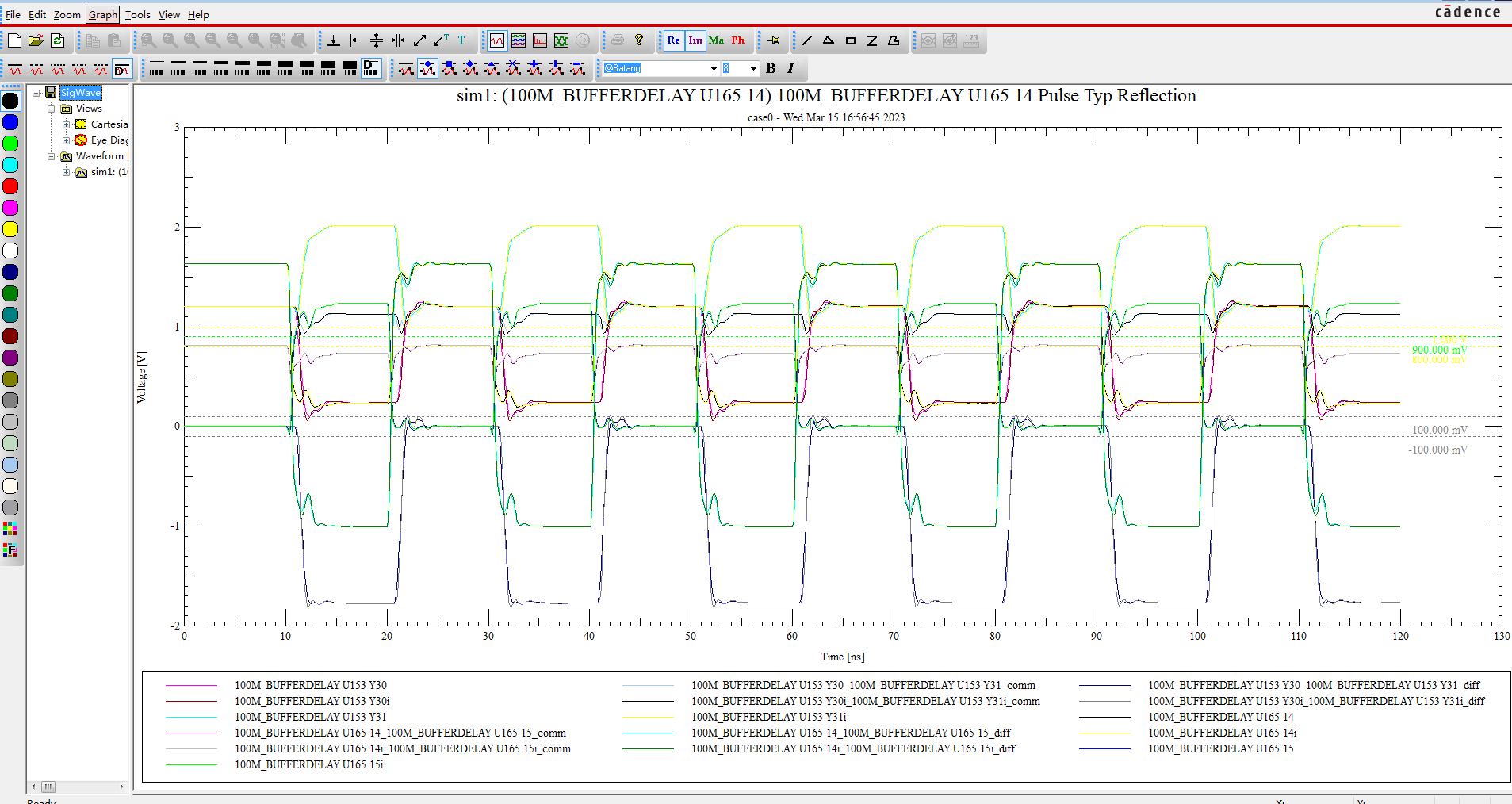

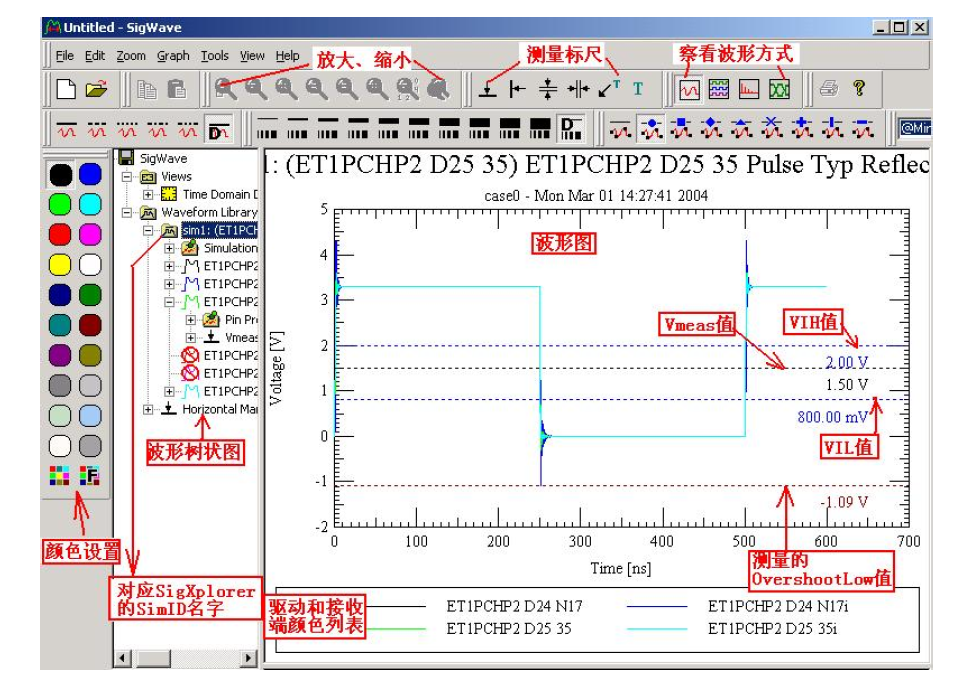

创建或提取并设置好仿真拓扑,就可以执行仿真了。点击Analyze -> Simulate或者快捷按钮,在一段时间之后仿真完成,测量结果显示在Results栏,同时也会弹出SigWave窗口显示波形。

对左边的一些波形的名称举例解释如下:

—D24 N17 表示拓扑中D24 器件N17 Pin 处的波形;

—D24 N17_buffdly 表示接测试负载时N17 Pin 处的波形;

—D24 N17_buffdlyi 表示接测试负载时N17 Pad 处的波形;

—D24 N17i 表示拓扑中D24 器件N17 Pad 处的波形;

SigWave 仿真波形窗口

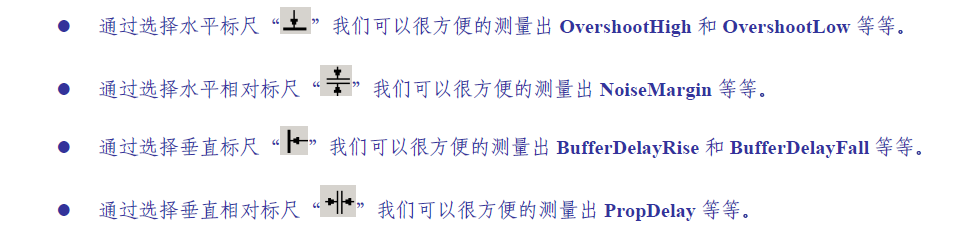

测量标尺说明:

5. 参考文献:

https://download.csdn.net/download/sunlight_vip/86247419