连接器信号完整性仿真教程 二

在连接器信号完整性仿真教程一中Step by Step演示了如何进行连接器信号完整性仿真,看完这片博文后应该可以做类似产品的仿真。如果说,看了这篇博文就学会了连接器信号完整性仿真,那就有点过了。有人也许会说信号完整性仿真难学,不学、不做也罢。

为何要做连接器信号完整性仿真呢? 在连接器信号完整性仿真教程一中讲到了,一些协议标准中对连接器的信号完整性有要求,不达到其要求就是不合格。关键是在高速电路设计时必须考虑连接器信号完整性参数。如果你是一个PCB设计师,你肯定不会忽略连接器的信号完整性,甚至要求供应商提供连接器的3D模型,做一下仿真,以评估其对系统信号完整性的影响。如果你是一个连接器设计工程师,当你接到一个新开发案,明确提出了传输速度要求或者信号完整新要求,如果不做仿真,你的设计图敢拿出来开模吗?信号完整性相关的特性参数是看不见,摸不着的东西。绝大多数连接器在设计之初,除了仿真,别无他法。

从上面例子可以看出,要从事相关专业性较强的专业,真还需要正学会连接器信号完整性,首先要明白信号完整性的概念。什么是信号完整性?从广义上讲,信号完整性是指信号在系统线路传输过程中保持其时域、频域、幅值的能力,即信号在电路中以正确的时序、相位、幅值做出响应的能力。信号完整性有两个基本条件,信号幅值完整性与时间完整性。幅值完整性是指满足电路的最小输入高电平和最大输入低电平要求。时间完整性是指电路的最小建立和维持时间。

上面说到的信号完整性还是一个笼统的概念,他需要以一些参数来具体表示,以便具体测量与评判。连接器信号完整性特性参数大多与S参数有关,如果你看过我的博文《S参数及高速电子连接器特性参数简介》,对连接器信号完整性特性参数应该有所了解,如果没有看过,可去看看。这里不再去做具体介绍。

哪些因素会影响到连接器的信号完整性?电子连接器大多数由金属导体(端子)组成对插连接电路,除少数连接器外,没有额外去串/并电阻、电感或电容。连接器的端子,我们可以把它当作传输线来处理。交流信号向前传输的的过程实际上是一个电磁场向前移动的过程。电流流过导体,导体电阻会导致发热损耗;电磁场穿过介质也会产生耗损;如果传输线路存在阻抗不匹配,传输线路的阻抗不匹配还会导致反射,这是影响连接器信号完整性不可忽略的最主要因素,其主要表现在回波损耗(Return Loss)上面。这些都是影响连接器信号完整性的因素。

连接器的直流电阻(也就是我们常说的接触电阻)较小,一般在几十毫欧,在特性阻抗中z直流电阻几乎可以忽略不计。阻抗主要与端子pitch、长度、端子形状、材料厚度、介质的介电常数相关。高速连接器的仿真其实主要是在解析S参数,而仿真优化主要是围绕阻抗匹配进行。

在后续的教程中将继续主要以CST studio suite为主要软件,详细讲解如何进行高速连接器信号完整性仿真,可能也会用同一模型以HFSS分析做一下对比。

电磁仿真对电脑配置要求相对较高,无论是用HFSS或者CST。分析耗时较长,CPU占用较高,如果有条件建议使用图形工作站,高主频,2个或以上CPU,最好有Nvida加速卡或者Nvida显卡,配置大容量硬盘,因为一次仿真结果占用硬盘空间,少则几个Gb,多则几十个Gb,如果硬盘较小,不旧就会被填满,除非你不在乎你的分析结果,做一次删除一次。当然用PC机也不是不可以,你可能得忍受CPU高速运转时,电脑机箱发出的烦人风扇声;前提是你的机器能顶得住几天甚至几个星期不关机。下面简单介绍一下CSTCST 工作室套装(CST Studio Suite):

CST 工作室套装是一个强大的电磁仿真平台,具有十分精确和高效的电磁设计和仿真解决方案,覆盖电磁、带电粒子、电路、热学和力学多物理场的高集成度专业数值仿真。它主要由七个工作室子软件组成,分别是CST 微波工作室、CST 印制板工作室、CST 电缆工作室、CST 设计工作室、CST 电磁工作室、CST 粒子工作室以及CST 多物理场工作室。所有的工作室子软件全部集成在同一个用户界面下,可以无缝快速切换,实现协同仿真。

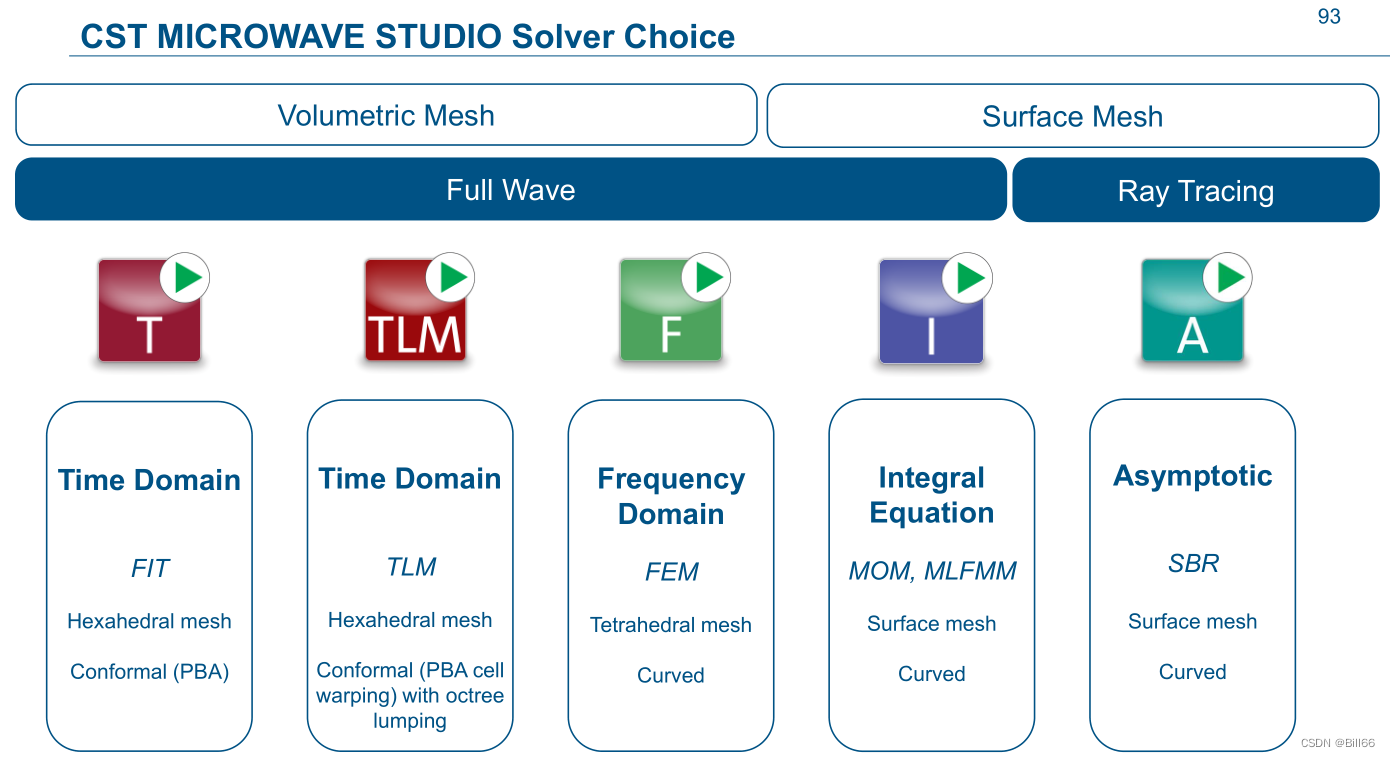

用CST做连接器仿真,有入门容易,边界条件及背景设置简单,有多个单独的连接器仿真模版,使用起来比较方便。CST常用解算器有:

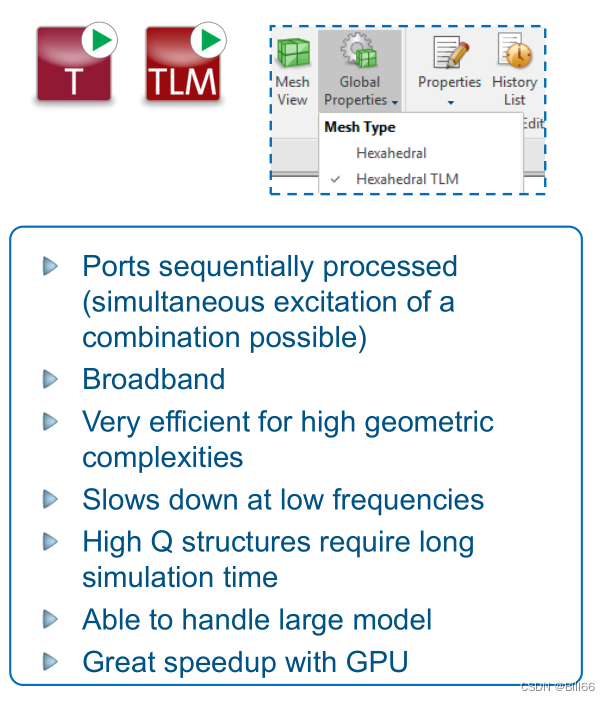

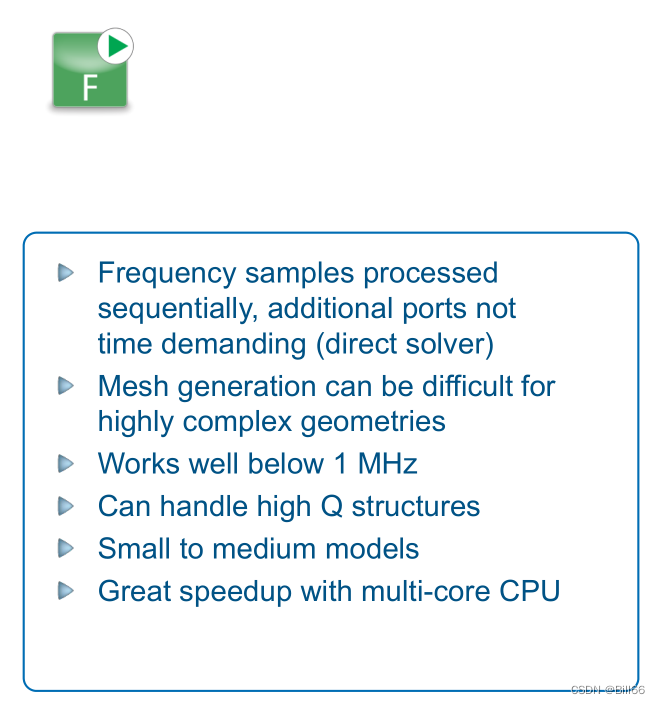

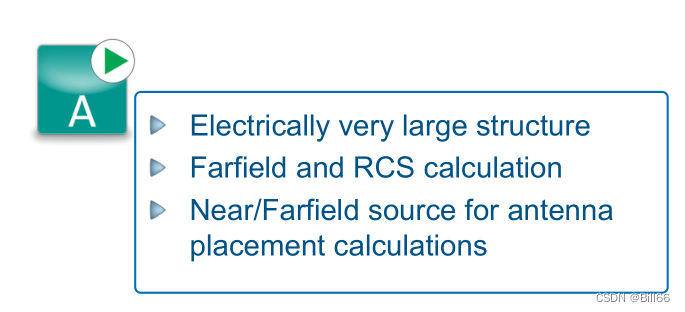

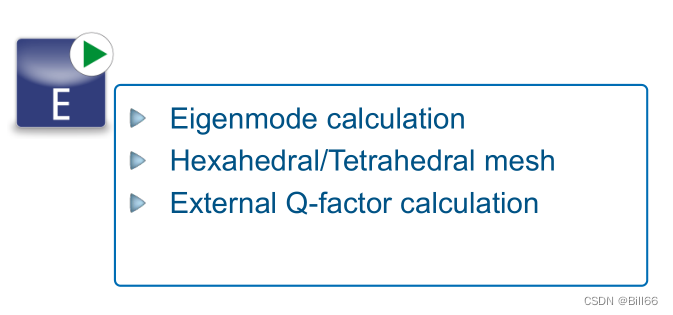

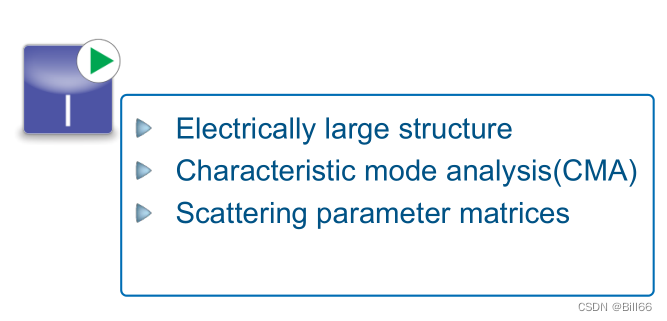

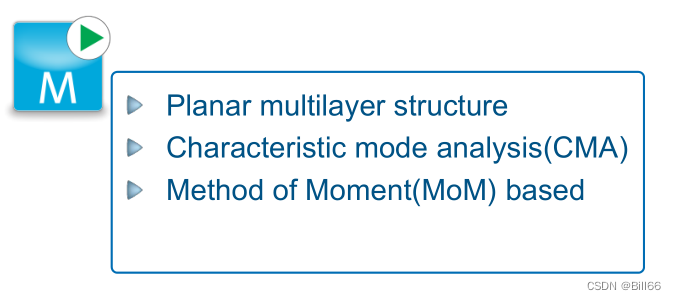

几个解算器的特点及实用场景:

高速连接器仿真,主要用到第一个T解算器,即时域解算器,其内存、CPU、GPU使用有一下特点: