Chapter3: Design Creation with RTL(ug949)

(3.5)Clock Domain Crossing

设计中的跨时钟域电路直接影响设计的可靠性。您可以设计自己的电路,但Vivado design Suite必须识别电路,并且必须正确应用ASYNC_REG属性。Xilinx提供XPM以确保正确的电路设计,包括:

•驱动place_design中的特定功能,减少同步电路的平均无故障时间(MTBF)。

•确保report_synchronizer_mtbf的识别。

•避免report_cdc错误和警告,当迭代时间较长时,这些错误和警告通常会在设计周期的后期出现。

提示:对于可以安全忽略的CDC违规行为,您可以使用waiver机制来豁免违规行为。有关详细信息,请参阅Vivado Design Suite用户指南:Design Analysis and Closure Techniques (UG906)中的相关链接。

当在两个异步时钟之间交叉时,或者当试图通过添加错误路径约束来放松两个同步时钟之间的定时时,需要CDC电路。当使用XPM时,您可以选择一个单比特或多位总线在域之间交叉。

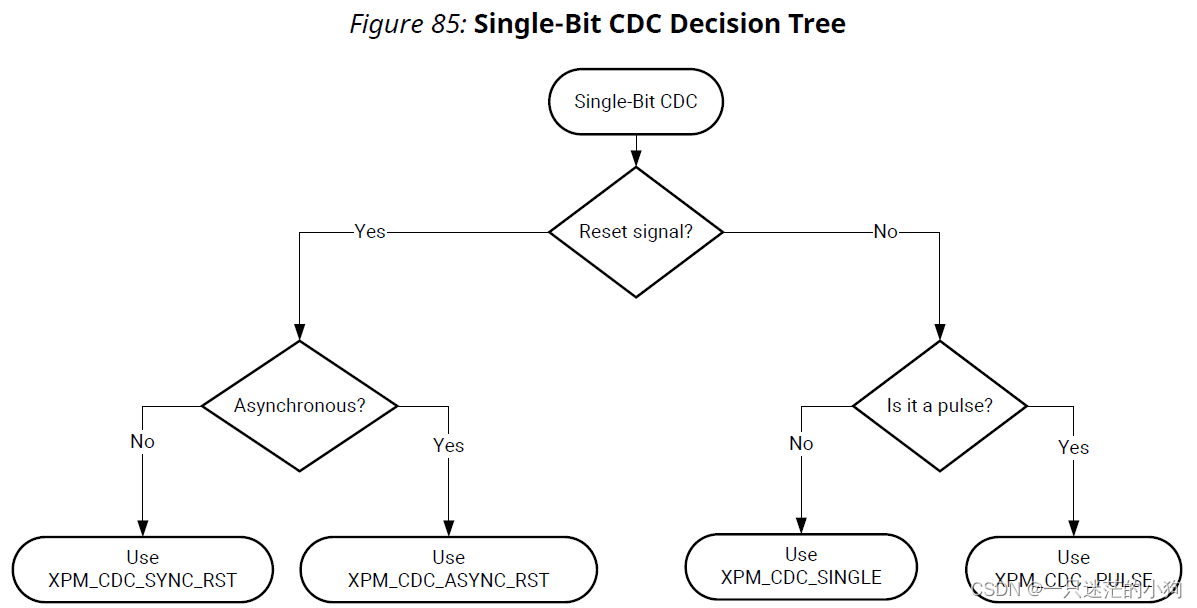

(3.5.1)单比特CDC

下图显示了使用单比特跨时钟域时所需的决策。

注意:有关不同的单比特同步器的更多信息,请参阅设备的Libraries Guide。

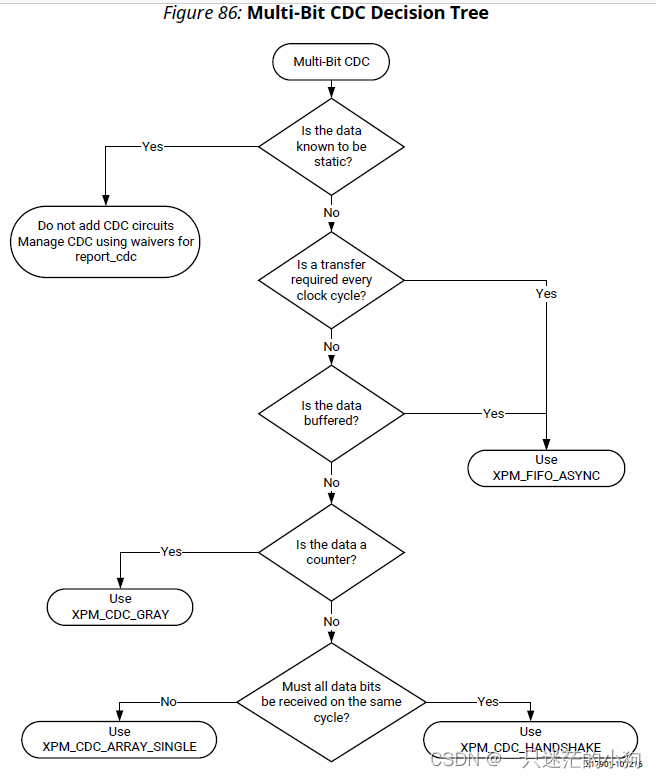

(3.5.1)多比特CDC

下图显示了使用多比特跨时钟域时所需的决策。

(3.6)Optimizing for MTBF(针对MTBF进行优化)

设计的总MTBF是以下各项的函数:

•同步器MTBF

•由于单一事件扰乱(SEUs)导致的设备故障及时率(FIT)

注:SEU导致的设备FIT率在很大程度上取决于工艺和设备尺寸。

同步器MTBF取决于设计,并随以下情况而变化:

•异步CDC点数

•每个交叉点的同步器级数

•目的触发器的频率

•源的切换速率

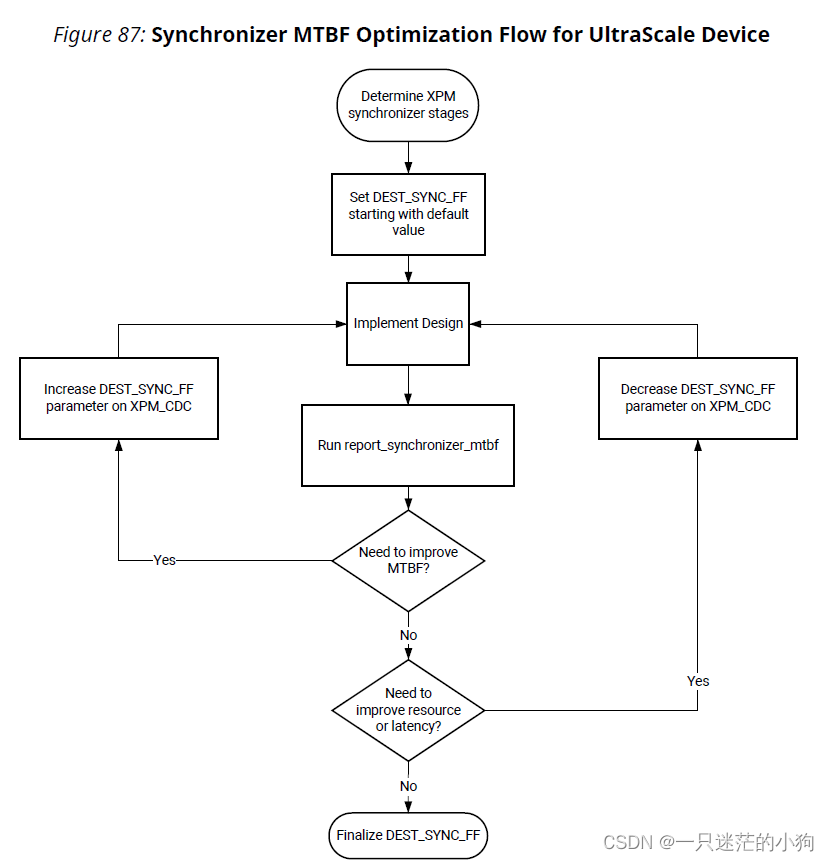

(3.6.1)选择DEST_SYNC_FF参数的正确值(Selecting the Correct Value for the DEST_SYNC_FF Parameter)

DEST_SYNC_FF参数设置使用XPM CDC模块时的亚稳态保护寄存器数量。该寄存器的值影响MTBF、设计大小和交叉点的延迟。选择此寄存器的正确值是一个迭代过程,需要以下内容:

1.通过Vivado design Suite实现流程运行设计。

2.根据您的目标设备,执行以下操作之一:

•对于7系列设备,选择DEST_SYNC_FF的默认值。这是一种保守的方法,可以满足典型的可靠性要求。对于关键设计,进行进一步分析。

•对于UltraScale设备,运行report_synchonizer_mtbf命令,该命令报告整个设计的mtbf。

通过如下图所示迭代流程,您可以在MTBF、延迟和资源之间找到合适的折衷方案。注意:您也可以将此迭代过程用于用户CDC电路,其中ASYNC_REG属性正确应用于所有同步寄存器。

(3.7)Constraining the Design Correctly

XPM CDC提供自己的set_max_delay-datapath_only约束。XPM cdc与set_clock_groups约束不兼容,后者具有更高的优先级,并将覆盖XPM中的约束。

Related Information

Defining Clock Groups and CDC Constraints