Nand Flash基础知识

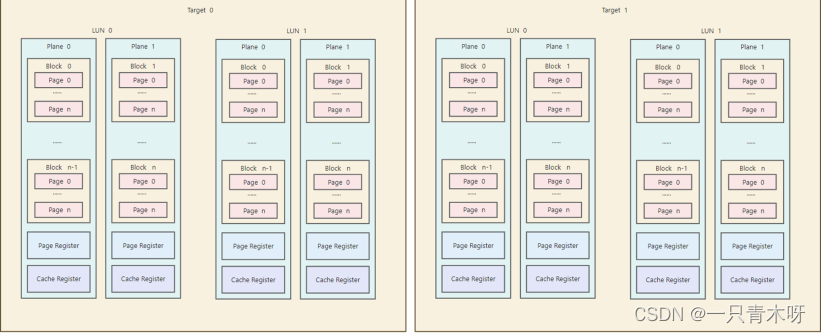

1、Nand Flash组织架构

- Device(Package)就是封装好的nand flash单元,包含了一个或者多个target。

- 一个target包含了一个或者多个LUN,一个target的一个或者多个LUN共享一组数据信号。

- 每个target都由一个ce引脚(片选)控制,也就是说一个target上的几个LUN共享一个ce信号。

LUN(Die):

- LUN是执行命令的最小单元,不同的LUN可以执行不同的命令序列

- LUN包含一个或多个plane(通常有1 2 4 8)

Plane:

- 一个plane包含一个或多个块(通常几百上千个)

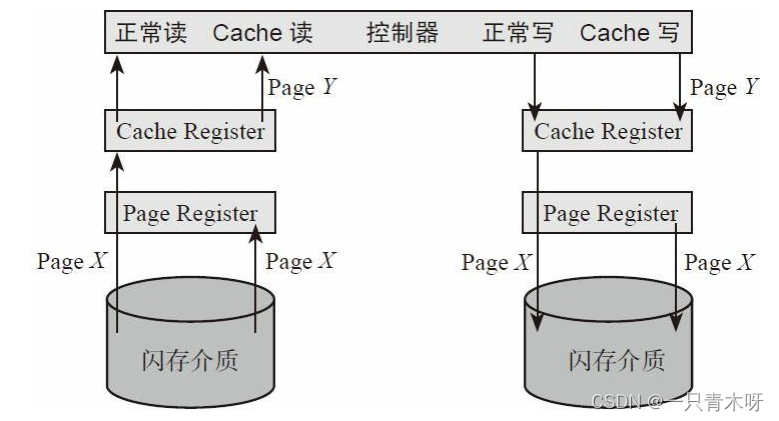

- 每个plane有独立的page register 和 cache register(优化闪存访问速度)

Block:

- 块是最小的擦除单位

- LUN中块的数量是没有限制的

- 块包含很多个页,数量必须为32的倍数

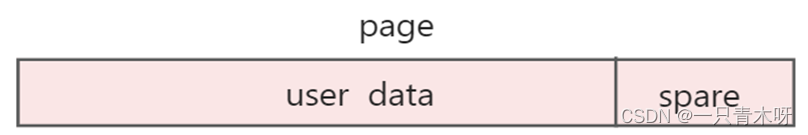

Page:

- 页是最小的读写单元

- 页包含很多个字节(大小通常为2的幂不包括spare区域)

Spare:

- 存储ECC值、坏块标记等。大小2K—> 64byte 4K —>128K 8K—>256

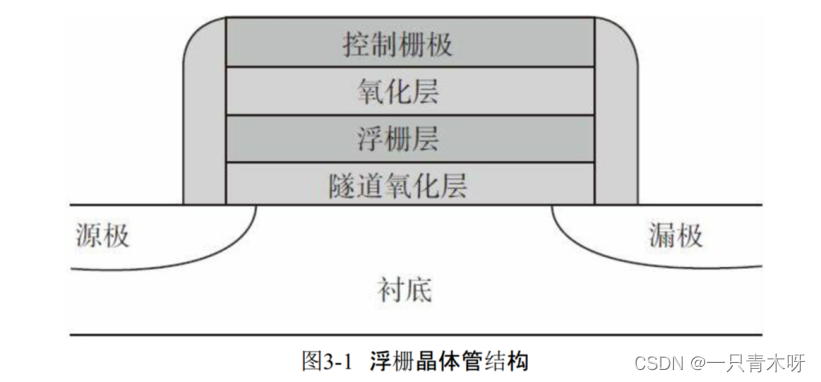

2、存储器原理

闪存的基本存储单元Cell,为非易失性存储器。(在源极(Source)和漏极(Drain)之间电流单向传导的半导体上形成存储电子的浮栅,浮栅上下被绝缘层包围,存储在里面的电子不会因为掉电而消失,所以闪存是非易失性存储器。)

Cell是闪存的最小工作单位,执行数据存储的任务。闪存根据每个单元内可存储的数据量分成SLC(1bit/Cell)、MLC(2bit/Cell)、TLC(3bit/Cell)和QLC(4bit/Cell),成本依次降低,容量依次增大,耐用度也依次降低

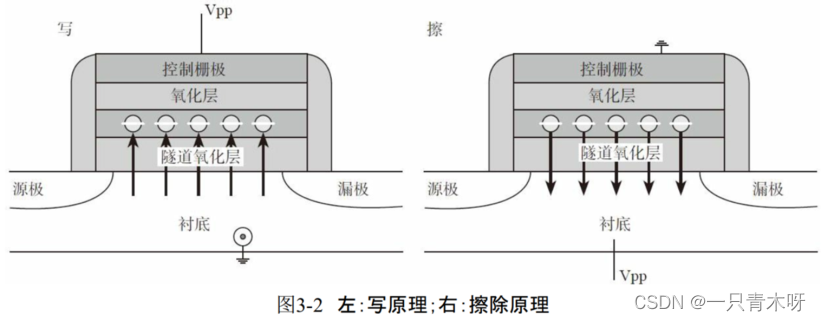

2.1、写/擦除原理

写操作是在控制极加正电压,使电子通过绝缘层进入浮栅极。擦除操作正好相反,是在衬

底加正电压,把电子从浮栅极中吸出来

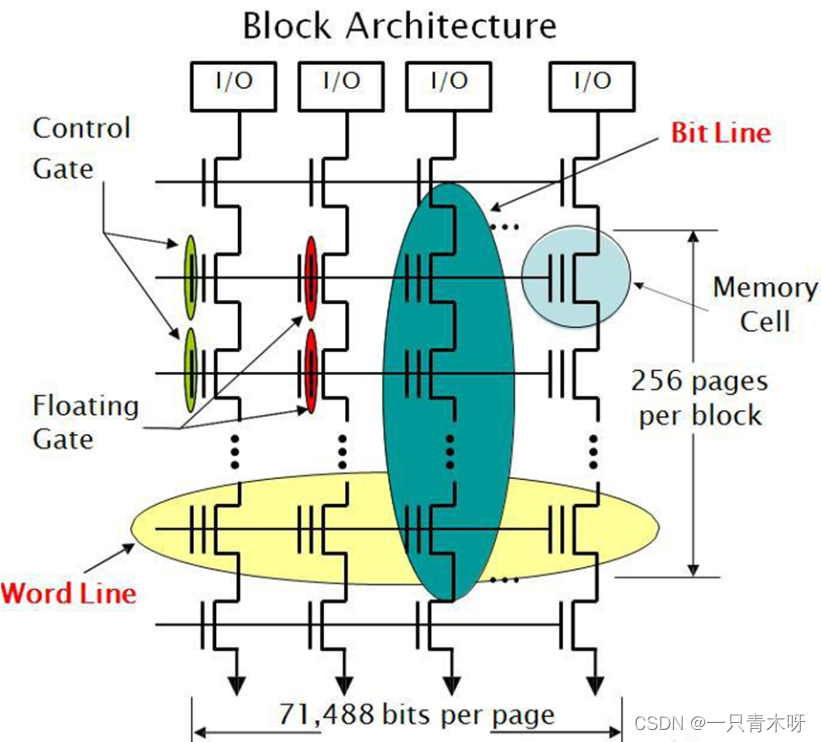

2.2、块组织架构

一个闪存芯片有若干个DIE(或者叫LUN),每个DIE有若干个Plane,每个Plane有若干个Block,每个Block有若干个Page,每个Page对应着一个Wordline,Wordline由成千上万个存储单元构成

2.3、读/写/擦除

2.3.1、擦除

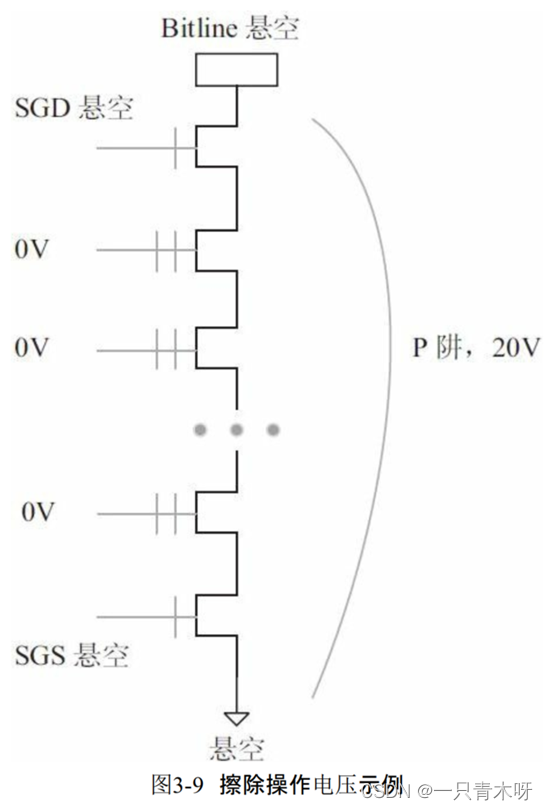

擦除前,浮栅上有可能有电子,Pwell加20V电压,经过足够时间后,由于量子隧道效应,电子从浮栅到沟道里面,完成一个Block的擦除 。

2.3.2、写

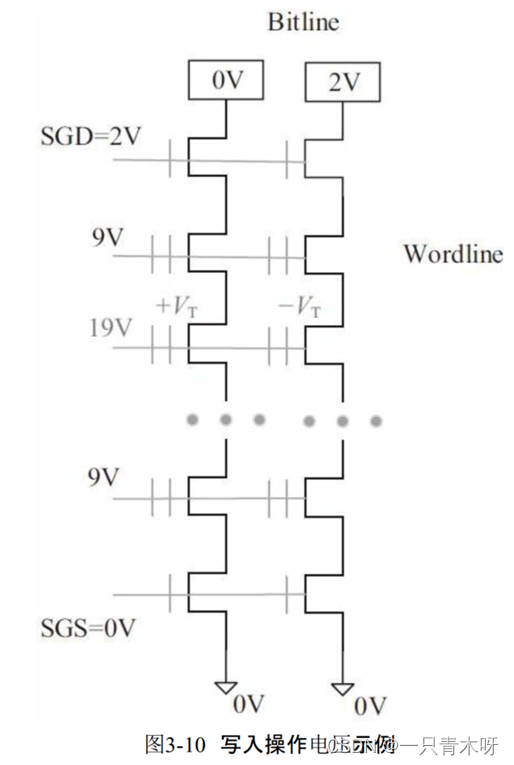

要写的单元Wordline为高电压,Bitline=0V;由于量子隧道效应,电子从沟道到浮栅,成为“0”。不写的单元Bitline为2V,在沟道里的效应阻碍了量子隧道效应发生

2.3.3、读

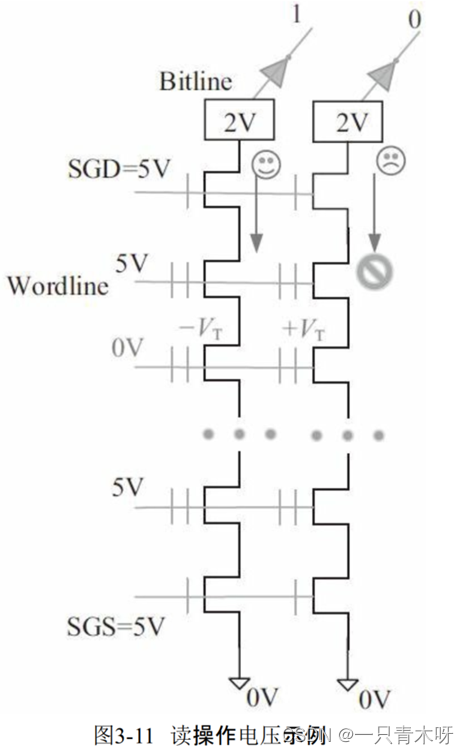

不读的Wordline=5V,管子保持导通;要读的单元Wordline=0V,-VT 的管子导通,Bitline端的传感器能够检测到,所以读到“1”,而经过写的+VT的管子不导通,传感器读为“0”。

3、读/写/擦除

大体流程如下:

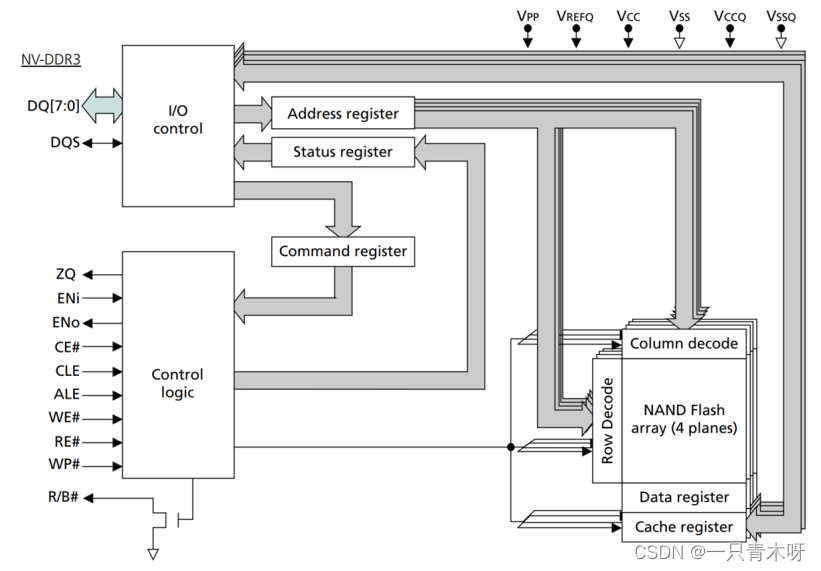

Nand Flash LUN功能框图:

其中有地址寄存器、状态寄存器、命令寄存器等,后面依次介绍。

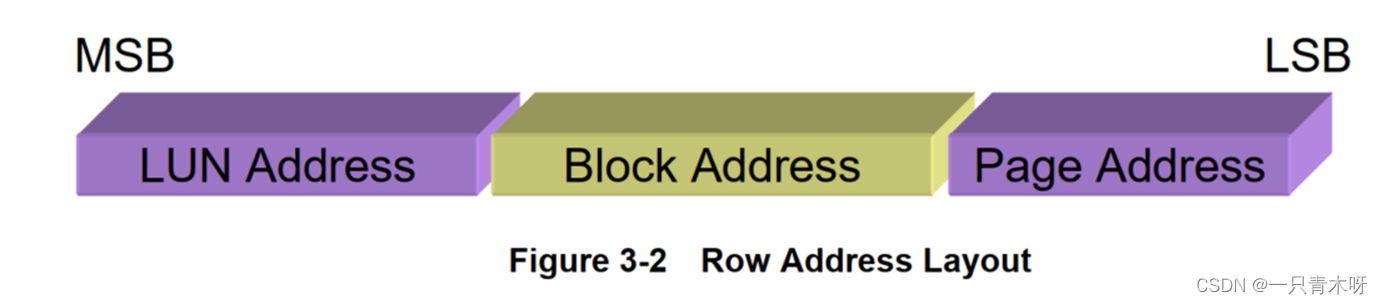

3.1、寻址

寻址方式:

- 行地址:页内偏移

- 列地址:在ONFI协议中,高位到低位依次表示:LUN地址、块地址、页地址

注意:

1、当需要同时发出列地址和行地址时,列地址总是在一个或多个8位地址周期中首先发出。

2、在擦除的时候,列地址不需要发送。

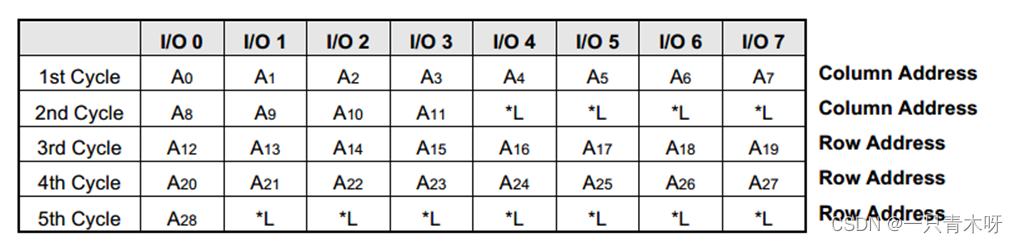

访问数据都是要先通过地址进行定位,在上图中可以看到有12根列地址线(A0-A11)和17根行地址线(A12-A28),总共29根地址线。数据线是8位,一次只能发送8bit,所以地址需要多个周期发送,上图显示的是5cycle发送

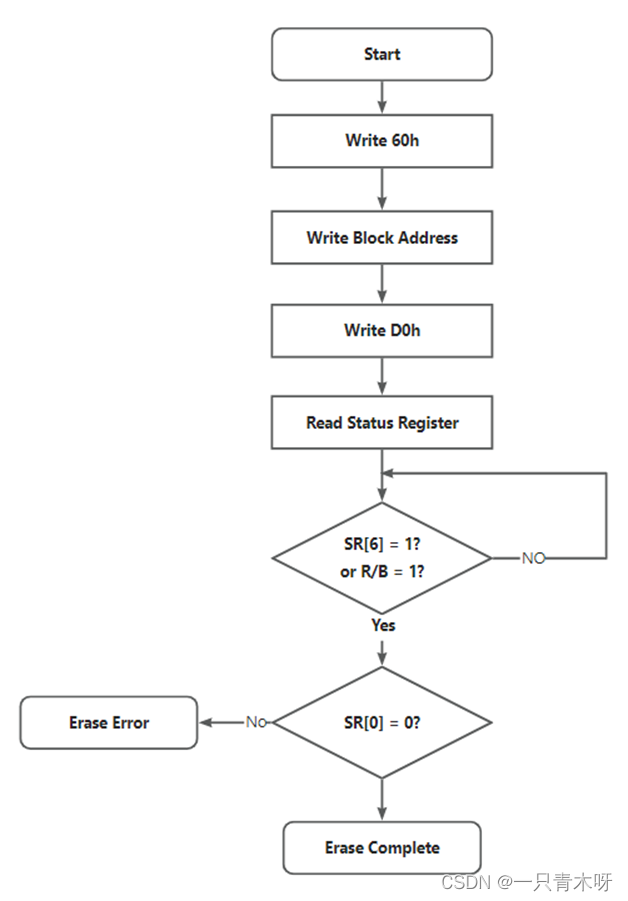

3.2、擦除

擦除以块为单位,不需要列地址。

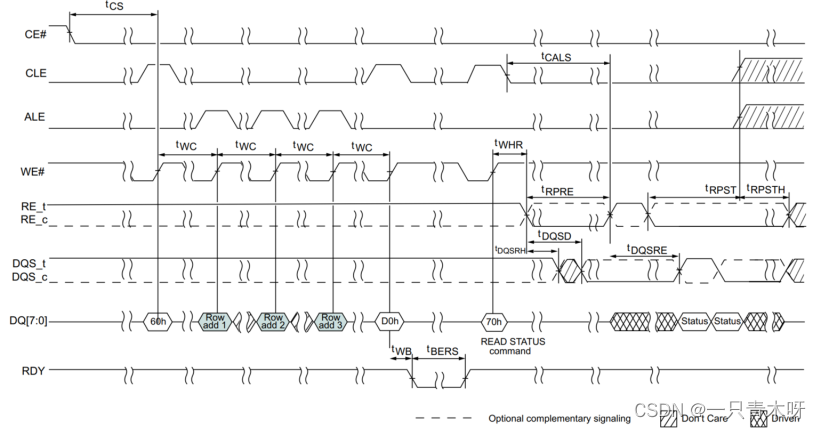

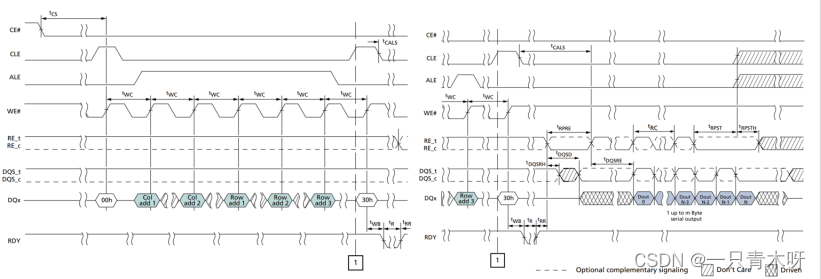

时序图如下:

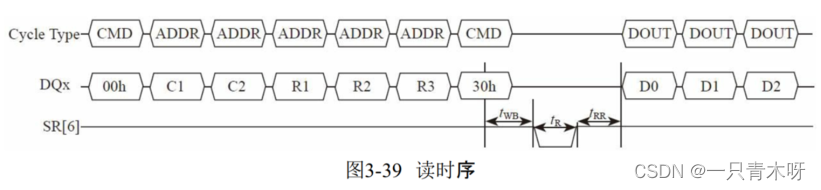

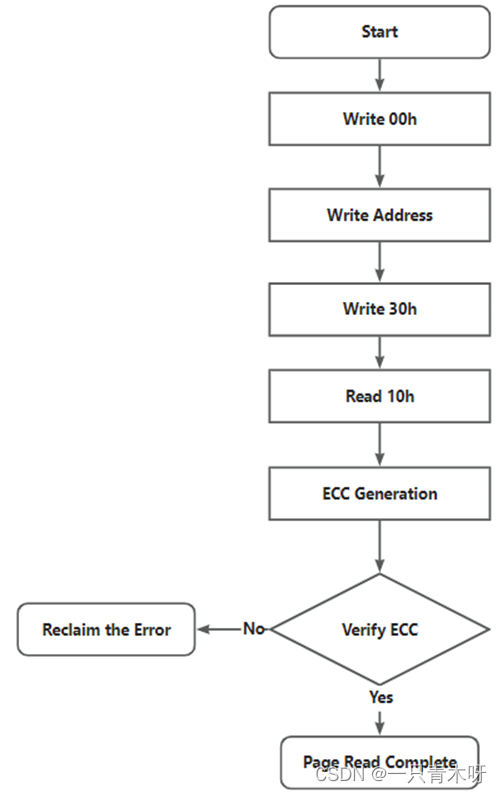

3.3、读

时序图如下:

3.4、写

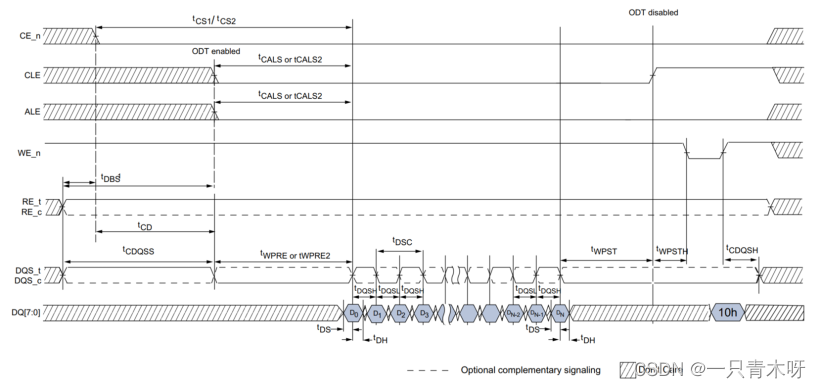

时序图如下:

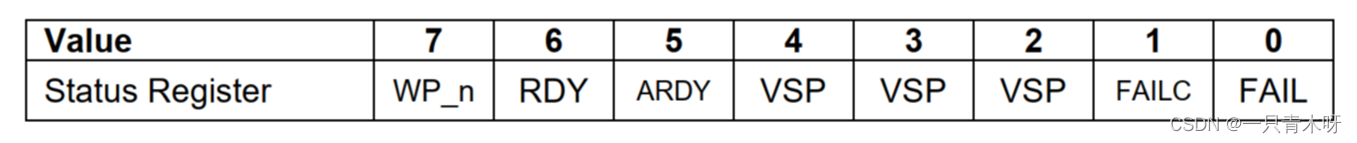

3.5、状态寄存器

当SR[6]为0时,其他所有位无效(WP_n除外),主机需要忽略其状态。

- FALL(0): 返回最近一条命令的结果。1 失败 0 成功。

- FALLC(1): 返回上一条命令的结果。1 失败 0 成功。

- VSP(2 3 4):厂商自定义。

- ARDY(5):1,没有正在执行的Flash array操作。 0 ,最后一条命令的上一条命令还未执行完成。

- RDY(6):1,表示最后一条命令执行完成并处于ready状态。0,最后一条命令还未完成,SR[5]也无效。

- WP_n(7):1,没有开启写保护。 0 开启写保护。

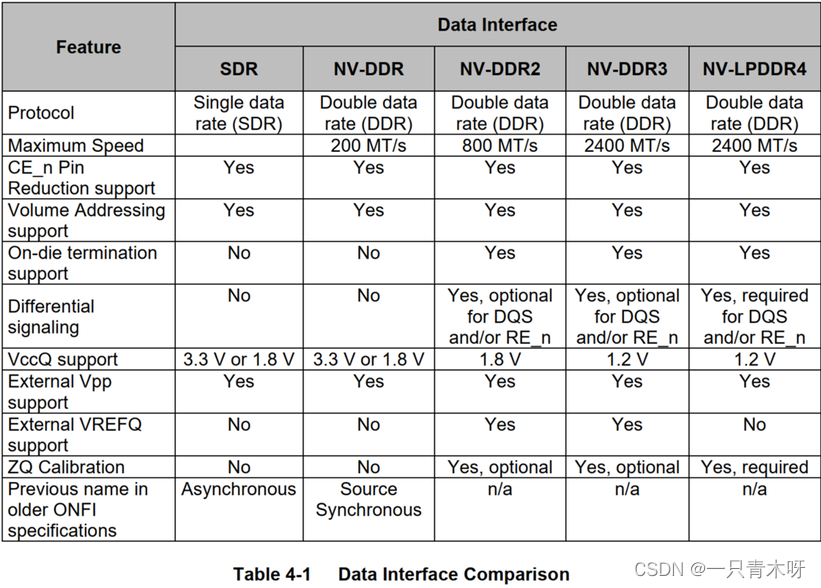

4、数据接口

- NV-DDR:双边沿采样,并采用源同步时钟来精确所存数据、命令、地址信号。

- NV-DDR2:引入了差分信号和On-Die Termination (ODT)技术来提升信号质量。

- NV-DDR3:NV-DDR3引入了多项校准技术,包括ZQ Calibration、Duty Cycle Correction (DCC)和读/写DQ校准。

- NV-LP-DDR4:和NV-DDR3速率相同,优势在于采用LTT技术后可大幅度降低读操作功耗

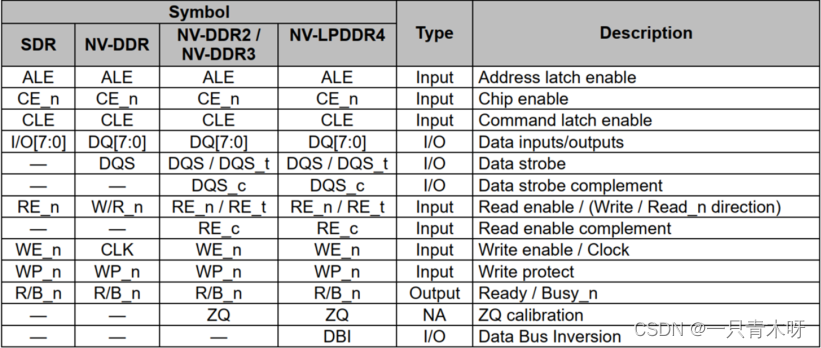

各个接口的信号线:

- R/B_n:Ready/Busy。闪存正在进行内部读的时候,Busy_n有效,当操作完成且数据准备好之后,Ready有效,用户可以来读了

- CLK:时钟。时钟信号由用户产生,在时钟信号的上升沿和下降沿都有数据被触发,实现DDR,意味着100MHz的时钟频率数据传输速率是200MT/s

- W/R_n:Write/Read_n。写的时候高电平,读的时候低电平

- DQS:Data Strobe。DQS用来区分出每个数据传输周期,便于接收方准确接收数据。读数据时,DQS由闪存产生,DQS上下沿和数据对齐。写数据时,DQS由用户产生,DQS中间对应数据的中间稳定区域。所以,DQS可以看成数据的同步信号

- DQ[7:0]:数据总线

- WE_n:Write Enable,写使能,这个信号是用户发给闪存的,有效时意味着用户发过来的写数据可以采样了

- RE_n:读使能。这个信号是用户发给闪存的,每发一个读使能,闪存就在数据总线上准备好数据,等用户采样