跨时钟域传输数据——单bit和多bit信号(总结)

文章目录

前言

2023.4.6 小雨

电平/边沿检测/脉冲同步器

FIFO

一、慢时钟域到快时钟域

快时钟域会多次采样,目标时钟频率必须是源时钟频率的1.5倍及以上,才能满足 “三时钟沿” 要求。如果目标时钟频率只是快一点,还是用握手机制。

1、单bit信号

- 边沿检测同步器(详细介绍笔记)

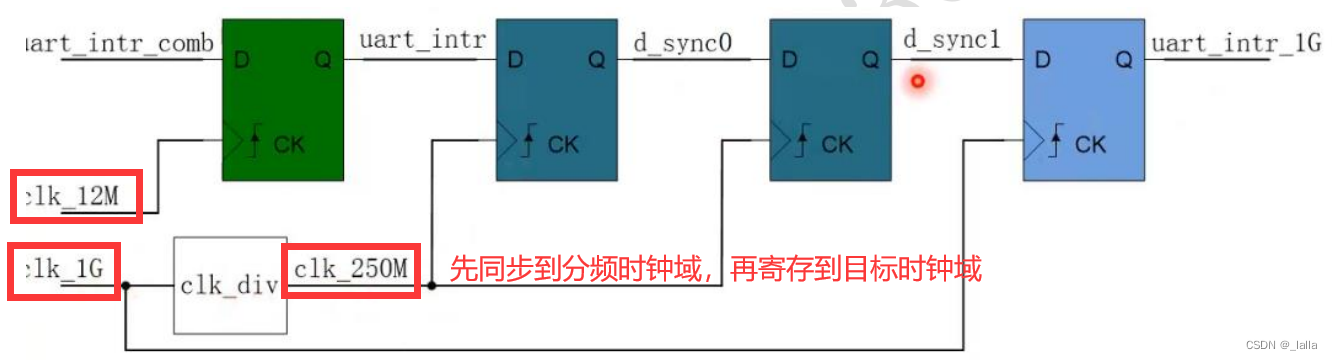

- 分频再同步(频率相差很大)

2、多bit信号

延迟采样法:引入使能信号,先缓存使能信号(三级缓存,前两级缓存,后一级上升沿检测),等输入使能信号有效时再缓存数据

module delay_sample(input clk1,input clk2,inout rst_n,input [31:0] din,input din_en,output dout_en,output [31:0] dout

);reg [2:0] din_en_r;//缓存使能信号always@(posedge clk2 or negedge rst_n)begin //注意这里是clk2if(!rst_n)din_en_r <= 0;elsedin_en_r <= {din_en_r[1:0], din_en};endwire din_en_pos = din_en_r[1] & !din_en_r[2];reg [31:0] dout_r;reg dout_r;//输入数据缓存always@(posedge clk2 or negedge rst_n)begin if(!rst_n)dout_r <= 0;else if(din_en_pos)dout_r <= din;end//输出使能信号always@(posedge clk2 or negedge rst_n)begin if(!rst_n)dout_en_r <= 0;elsedout_en_r <= din_en_pos;end assign dout = dout_r;assign dout_en = dout_en_r;

endmodule

二、快时钟域到慢时钟域

慢时钟域可能采样不到信号

三时钟沿要求:快时钟域信号宽度必须大于慢时钟域周期的1.5倍以上,也就是持续3个时钟沿以上(包括上升沿和下降沿)

1、单bit信号

- 脉冲同步器/结绳法

2、多bit信号

- 握手机制

三、多bit信号跨时钟域传输

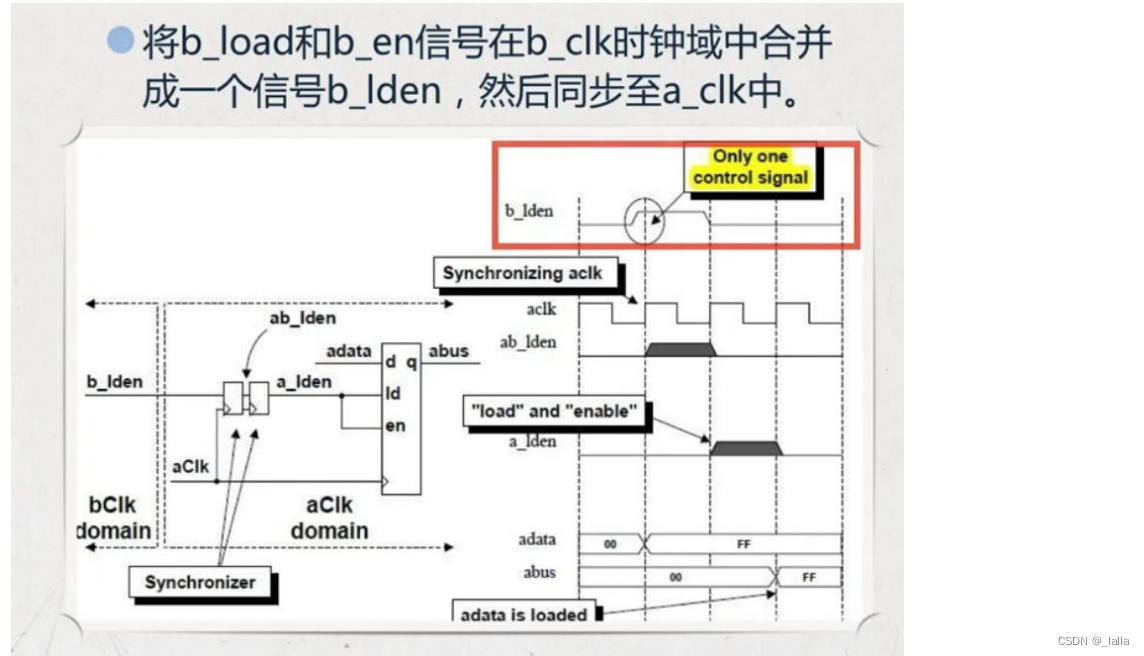

1、多个信号合并

把多个信号合并为1bit信号再跨时钟域传输

2、多周期路径 Multi-cycle Path/MCP

不同步多位数据,只同步一位控制信号

3、使用格雷码

- 如果多bit信号是简单递增或者递减,可以转化为

格雷码,再打两拍到目标时钟域,再解码 - 如果多bit信号没有规律,可以转化为

独热码,再打两拍到目标时钟域,再解码,适合于从慢到快

4、使用异步FIFO

详细介绍:同步FIFO、异步FIFO详细介绍、verilog代码实现、FIFO最小深度计算、简答题

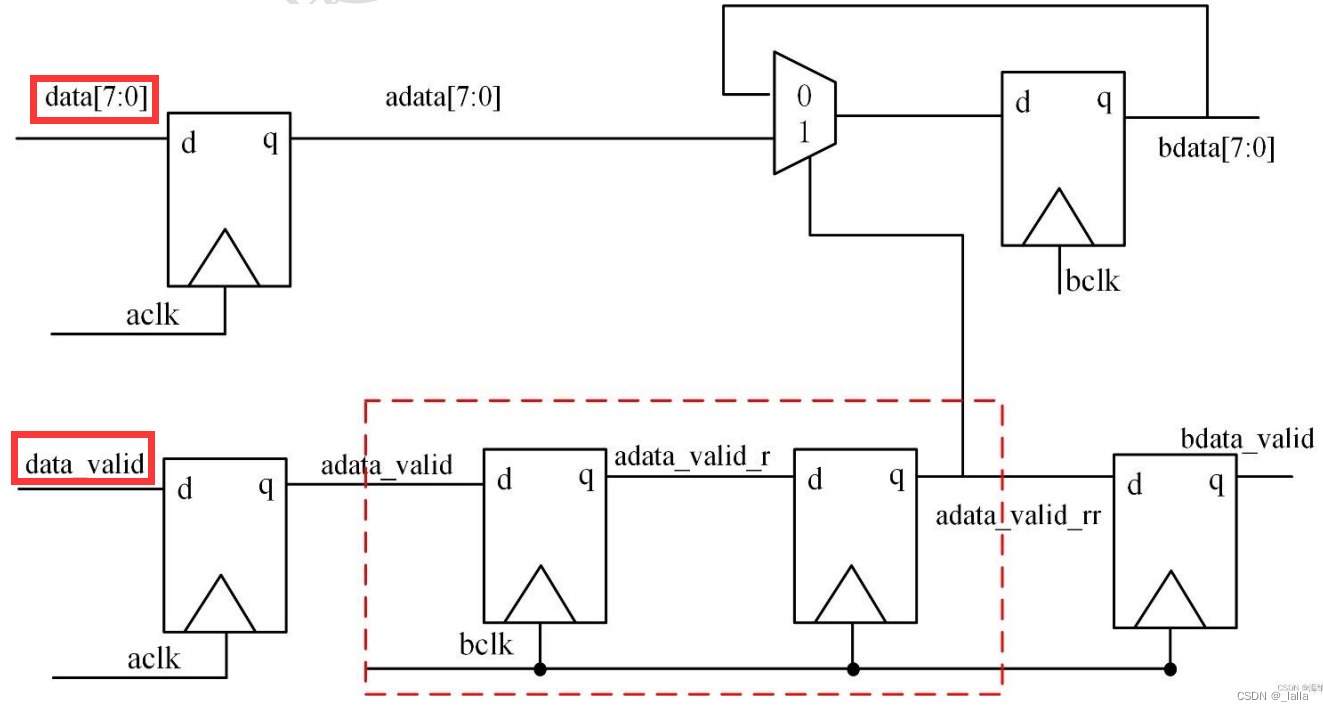

5、使用DMUX电路结构

适用:带有数据标志位的多bit信号跨时钟域传输(和延迟采样法差不多),适合于慢时钟域到快时钟域传播。

如果是快时钟域到慢时钟域,就把红色框内的两级同步器换成脉冲同步器。

adata_valid_rr再打一拍是为了和bdata的数据同步输出。

module mux_synchronizer(input aclk, input bclk,input data_valid,input rst_n,input [7:0] data,output reg [7:0] data_b,output reg bdata_valid

);reg data_valid_r, data_valid_rr, data_valid_a;reg [7:0] data_a;always@(posedge aclk or negedge rst_n)beginif(!rst_n)begindata_valid_a <= 0;data_a <= 0;endelse begindata_valid_a <= data_valid;data_a <= data;endendalways@(posedge bclk or negedge rst_n)beginif(!rst_n)begindata_valid_r <= 0;data_valid_rr <= 0;endelse begindata_valid_r <= data_valid;data_valid_rr <= data_valid_r ;endendalways@(posedge bclk or negedge rst_n)beginif(!rst_n)begindata_valid_b <= 0;endelse begindata_valid_b <= data_valid_rr;endendalways@(posedge bclk or negedge rst_n)beginif(!rst_n)begindata_b<= 0;endelse begindata_b <= (data_valid_rr) ? data_a : data_b;endend

endmodule

6、握手信号传输

四、简答题

1、跨时钟域传输的三种方法

打两拍、异步FIFO、握手信号