【从零开始学习 UVM】12.5、UVM RAL(续更) —— RAL Adapter

文章目录

-

- 用户定义的 reg_axi_adapter 实现

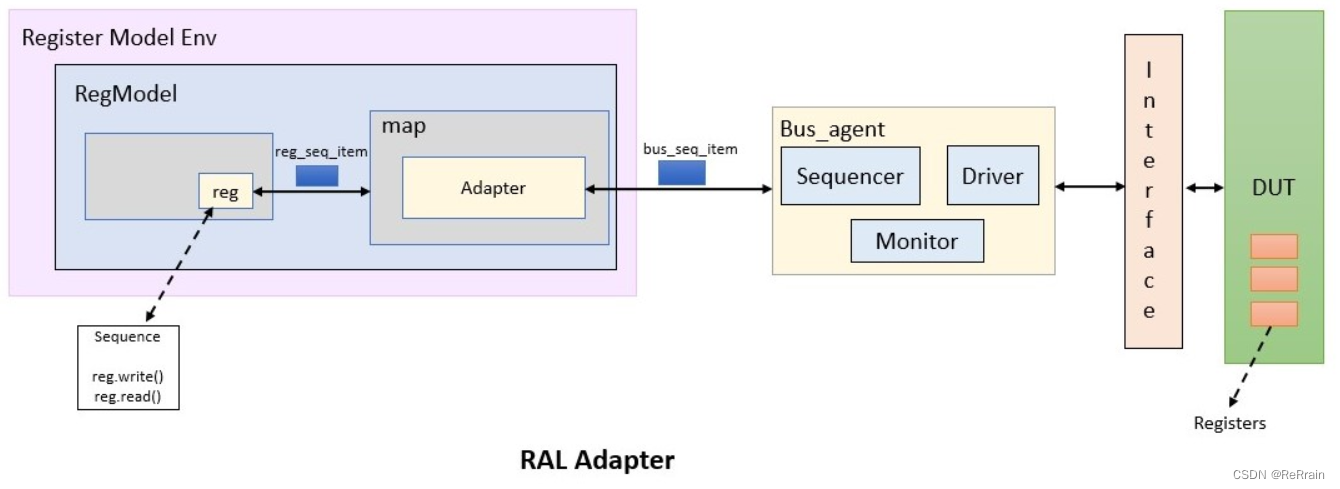

UVM寄存器模型(RAL)的方法,如write()和read()处理寄存器事务【register transactions】(即寄存器序列项【register sequence item】),DUT通过接口从/向TestBench接受或发送信号级别事务【signal level transactions】(总线序列项【bus sequence item】)。

因此,需要将寄存器事务转换为总线事务【register transactions to bus transactions 】,反之亦然。这由“Register Adapter”实现。用户定义的适配器类派生自uvm_reg_adpater基类。

每个前门访问操作(read() 或 write() 方法调用)都通过 reg2bus 和 bus2reg API 进行。用户必须实现这两种方法。

- reg2bus: 它将寄存器事务转换为总线事务

pure virtual function uvm_sequence_item reg2bus